20Q2.09B

20Q2.09BMIG を使って DRAM メモリを動かそう (4)

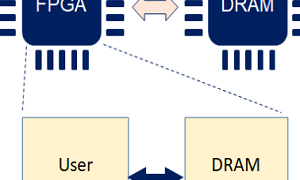

この記事では、前回まで解説してきた MIG ベースの DRAM コントローラのテストプログラムと先端の RISC-V ソフトプロセッサへの応用を説明していきます。 ソースコード: テストプログラム: ソフトプロセッサ: Wizard ベースのクロック生成スクリプト: 説明では、現時点 (2020年8月) ACRi ルームで使用可能な Vivado 2019.2 を使用します。ターゲットの FPGA ボードは Arty A7-35T です。 テストプログラムと RI...