コース紹介

コース紹介ACRi ブログの 20Q1 のコース紹介

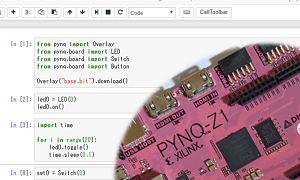

ACRi ブログへようこそ。このブログはアダプティブコンピューティング研究推進体が運営しています。 アダプティブデバイスの FPGA を活用するシステム、活用基盤、研究成果などの記事を発信していきます。 アダプティブコンピューティング研究推進体 参加組織 (2020年5月) この記事では、2020年4月に始まったコースを紹介します。 ACRi ブログは、3か月 (クォーター) 単位で新しいコース (連載とも呼びます) を提供していきます。2020年の第1クォーター (20Q1...