みなさんこんにちは。この「 FPGA をもっと活用するために IP コアを使ってみよう」のシリーズでは、全5回を通じて FPGA を使って実用的なアプリケーションを実装するために必要不可欠な IP コアの使い方を紹介していきます。

IPコアを使いこなせるようになると、既に開発されているモジュールの流用で開発コストを低く抑え、自分のアプリケーションの開発に注力できるようになりますよ。第一回では「IP コアって何?どんなもの?」について説明します。

IP コアってなに?

IP コアの IP は Intellectual property (知的財産) の略です。インターネットプロトコルではありません。 FPGA や ASIC 開発の界隈では、既に開発・検証されて流用できる部品を IP コアと呼びます。

ソフトウェアの開発ではゼロから自分で実装することはほとんどなくライブラリを積極的に利用します。たとえば、プログラミング言語 C を使ったプログラムでコンソールに “Hello World” と表示するときに標準 C ライブラリの printf を利用しますし、Python でプログラミングをするときに数値計算の numpy やグラフ描画用の matplotlib を利用することでしょう。

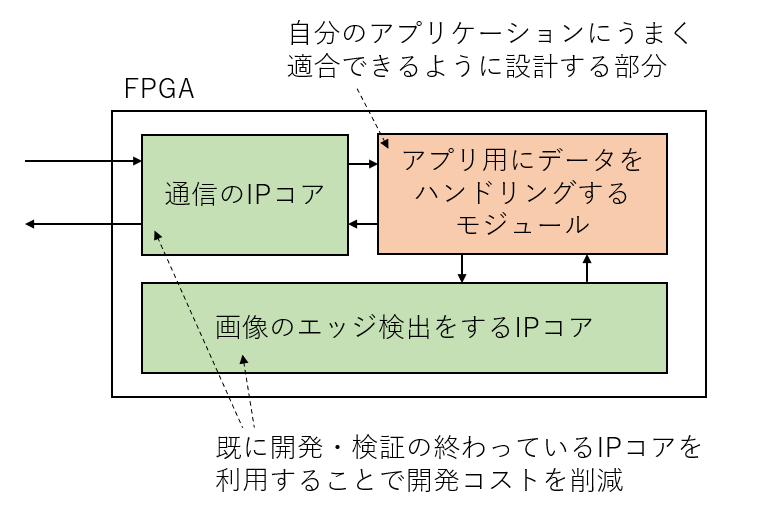

同じように、 FPGA にアプリケーションを実装する際に、必要な処理の全てを自分で実装する変わりに利用できるライブラリが IP コアです。たとえば、画像のエッジを検出するアプリケーションを実装したい場合に、ちょうどよい通信とエッジ検出の IP コアがあれば,データをハンドリングするモジュールだけ実装すればよくなります。

いろいろな IP コア

ソフトウェアプログラミングのために様々なソフトウェアライブラリが存在しているように、IP コアにもたくさんの種類があります。また、FPGA ベンダが提供する IP コアの他に、様々なメーカが開発、販売している IP コアや、オープンソースの IP コアもあります。

たとえば、FPGA ベンダの Xilinx 、Intel や Littice が提供する IP コアは、それぞれの Web サイトに掲載されています。

割り算や掛け算といった基本的な数値演算に相当する IP コアから、画像処理や CNN 計算といった高機能の IP コアまで、さまざまな IP コアが、それぞれの FPGA 向けに用意されています。

また、演算処理だけではなく、パソコンでおなじみの Ethernet や PCIe、マイコンなどでおなじみの I2C 、UART 、 といった通信処理用の IP コアもベンダから多数リリースされています。 FPGA 上に何かアプリケーションを実装するほとんどの場合に FPGA だけで完結することはなく、パソコンやネットワークに接続されることがほとんどです。それらの場合に通信用の IP コアを活用すると開発が楽になります。

ベンダから提供されている IP コアの一部はベンダの配布ライセンスに従う範囲で無償で利用することができますが、一部は使用料金がかかるものや評価用として利用期間が限定されるものもあります。

オープンソースの IP コアもあります。 OpenCores は、 IP コアの代表的な配布サイトです。GPL や MIT ラインセンスなどのもとで様々な IP コアが配布されています。

IP コアの利用方法

ソフトウェアは、ライブラリの呼び出しに ABI (アプリケーションバイナリインターフェース) のように守るべきインターフェースが規定されています。一方で、 FPGA 用の IP コアの場合、必ず守るべきインターフェースは存在しません。「プロセッサのように変更できないものに従う」必要がないからです。

とはいえ、いろいろな開発者が好き勝手に IP コアを開発していると、ユーザはそれぞれにあわせた使い方を調べて対応する必要があり不便です。そのため、2020年現在では共通の接続方式に集約されつつあります。代表的なものに、AXI 、Avalon 、Wishbone といった方式があります。

特に重要な IP コア – 入出力、クロック管理、メモリ

IP コアを利用すると FPGA でアプリケーションを開発するときの手間を省くことができます。実装したいアプリケーションに応じて便利なコアを探してきて使えばよいのですが、実用的なアプリケーションに不可欠なコアも存在します。

それが、入出力、クロック管理およびメモリの IP コアです。ソフトウェアプログラムを書く場合でも、入出力とメモリ、データ管理は必須ですね。一方で、クロック管理はソフトウェアプログラミングではあまり馴染みがないかもしれません。

パソコンのプロセッサでは負荷に応じてクロックの動作周波数が高くなったり低くなったりします。 FPGA を使う場合には、ハードウェアが適切に動作するように積極的にクロックの値を設定する必要があります。 IP コアを使うことで簡単に設定できるので、とりたてて怖れることはありません。このシリーズでも5回目で IP コアを使ってクロックを制御する方法を紹介する予定です。

次回は

次回は、FPGA でのアプリケーション開発に重要で使いこなせばとても便利な入出力用の IP コアである Xilinx の VIO (Virtual Input/Output) という IP コアを紹介します。VIO は、仮想的なスイッチを FPGA の中に埋め込むことができる IP コアです。これを使えば遠隔にある FPGA を制御したり内部の様子のモニタリングが簡単にできるようになります。

それでは次回をお楽しみに。

わさらぼ合同会社 三好健文