みなさんこんにちは。このコースでは FPGA を使いこなすために理解しておきたい論理回路の基本について説明します。FPGA を使って開発しているけどハードウェアはよく分からないという方は、ぜひお付き合いください。

前回は4ビットカウンタ回路の挙動をシミュレーションで確認しました。また、前回までで論理回路の基礎事項はあらかた説明しています。

今回は、回路設計、最適化に重要なタイミング解析について、よく出てくる用語とともに掘り下げて説明します。

タイミング解析

論理回路は値が0と1のみの世界です。したがって、回路の遅延はざっくりと説明すると値を0から1、もしくは1から0にする時間、つまり電圧を Low から High に充電、もしくは High から Low に放電するためにかかる時間です。

タイミング解析は、回路の遅延を見積り、設計している回路が目標のクロック周期で動作するかを確認することです。入力ピン、出力ピン、フリップフロップ (FF) のすべての組み合わせの間に存在するすべてのパスの遅延を見積もり、クリティカルパスを発見します。そしてそのクリティカルパスの遅延とクロック周期からその回路が動作するどうかを判定します。

例えば、設計中の回路を100 MHz で動作させたいとします。タイミング解析によりクリティカルパスの遅延が100 MHzのクロック周期よりある程度小さければその回路は100 MHzで動作します。タイミング解析により目標の動作周波数で動くことが確認できることをよく「タイミングがメット (MET)する」と言います。逆にクリティカルパス遅延が目標の動作周波数より大きい場合をタイミング・バイオレーションと言います。

クリティカルパスの遅延がクロック周期より「ある程度」小さければ動作すると言いましたが、その2つの単純な大小比較で小さければ良いわけではありません。回路が正しく動作するためにはいくつかの制約を満たす必要があります。また、IC や FPGA に実装した後も温度や電圧によって遅延が変化するため、最悪のケースを想定してマージンをとる必要があります。

セットアップ時間とホールド時間

回路中の FF を正しく動作させるために、セットアップ時間とホールド時間を守る必要があります。これは、FF が入力された値を正しく取り込むために必要な時間です。この時間を守らずに FF を動作させると、値は0か1のどちらかではあるけれども、どちらか分からない状態になります。ゲートレベルシミュレーションでは値が不定値 (x) になります。このセットアップ時間とホールド時間についての時間的制約をそれぞれセットアップ制約、ホールド制約といいます。

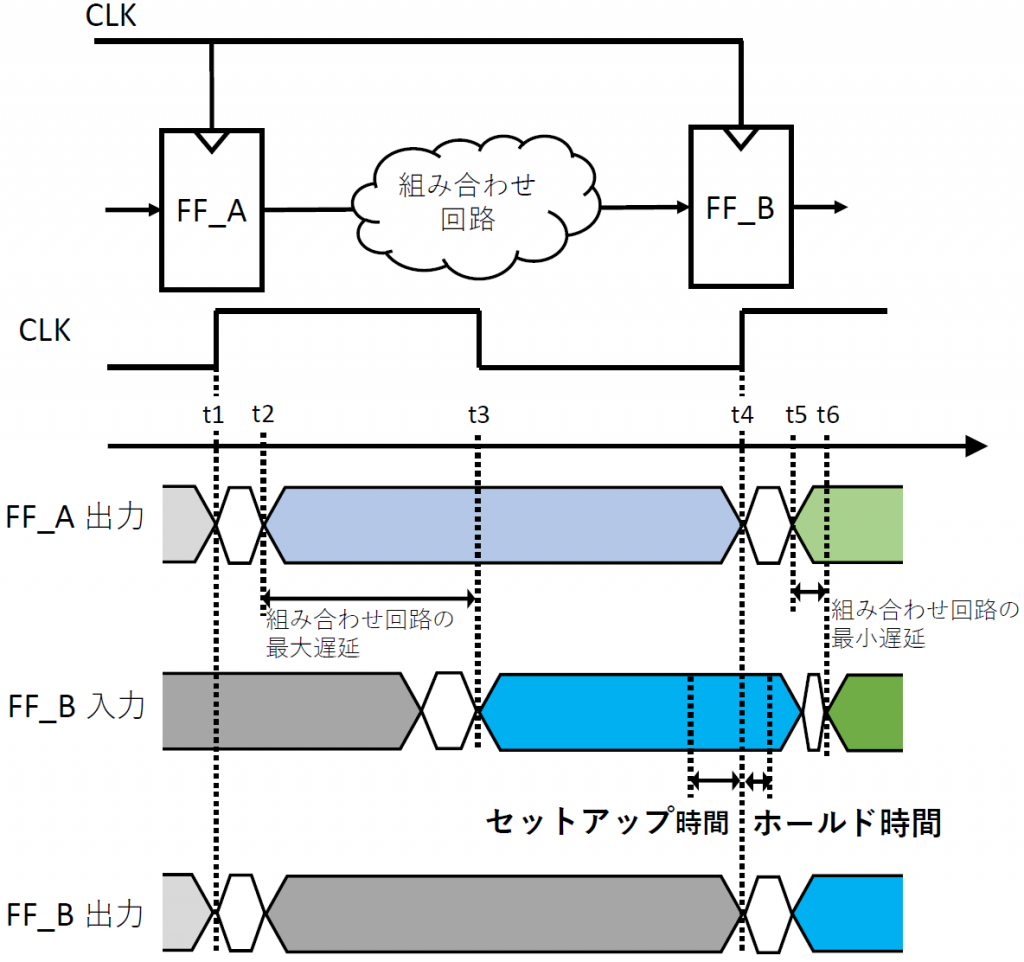

下の例で説明していきます。FF_A と FF_B があり、その間に何らかの組み合わせ回路があります。FF_A から出力された値は組み合わせ回路で計算され、計算結果がFF_B に取り込まれます。FF_A と FF_B は単一のクロック信号で動作 (単相クロック同期回路) しており、まずは簡単のためにクロック信号のズレは考慮しません。FF はクロックの立ち上がりエッジで値を取り込みます。

「FF_A 出力、FF_B 入力、FF_B 出力」はそれぞれ FF_A から出力される値、FF_B に入力される値、FF_B から出力される値の時刻ごとの変化を表しています。色の付いた区間は値が有効な区間で、白の区間は値が不安定な区間です。

FF_A の出力は、t1 からのクロックサイクルでは t2 で出力値が安定し t4 までその値を出力し続けます。FF_B の入力は、言い換えれば組み合わせ回路からの出力です。t2 でFF_A からの値が組み合わせ回路に入力され、組み合わせ回路の計算を経て t3 で計算結果が確定し、次のクロックサイクルの入力があるまでその値が維持されます。FF_B の出力は、挙動としては FF_A 出力と同様で、t3 からのFF_B 入力の値を取り込み、t4 からのクロックサイクルでその値を出力します。

図の例で、組み合わせ回路の遅延は FF_A から値が出力されてから FF_B に入力される値が確定するまでの時間です。図では (t3 – t2) と (t6 – t5) のそれぞれを組み合わせ回路の最大遅延と最小遅延であるとします。あるサイクルにおける「組み合わせ回路の遅延」は、入力の値が異なることで変化する点に注意してください。

セットアップ時間は、FF が正しく値を取り込むために必要なクロックの立ち上がりエッジの前の時間です。組み合わせ回路における計算は、FF のセットアップ時間を考慮して、それよりも前に値を確定させる必要があります。

ホールド時間は、FF が正しく値を取り込むために必要なクロックの立ち上がりエッジの後の時間です。組み合わせ回路における計算は、FF のホールド時間を考慮して、それよりも後まで値を入力し続ける必要があります。

図の例で、FF_B 入力の t3 からの(青色で示した)値は、FF_B のホールド時間の後まで値が維持されており、正しく値が取り込まれます。そして、t4 からのクロックサイクルで FF_B は取り込んだ(青色の)値を出力します。

セットアップ制約が問題となる場合は、FF への入力の値が最も遅く確定する、すなわち組み合わせ回路の最大遅延となる計算の場合です。図の例で、最大遅延となる t3 が (t4 – セットアップ時間) より前であればセットアップ制約が満たされます。

ホールド制約が問題となる場合は、組み合わせ回路の出力が最も早く変化する場合です。これは、例えば、組み合わせ回路の遅延が最小となる計算の場合です。図の例で、最小遅延となる t6 が (t4 + ホールド時間) よりある程度後であればホールド制約が満たされます。これが満たされないときは、t3 からの計算結果が FF_B に正しく取り込まれないことがあります。

単相クロック同期回路を設計する場合、FF 間には配線遅延などの何らかの遅延があるので、ホールド時間が問題になることはあまりありません。

クロックスキュー

上の説明はクロック信号のタイミングがズレないことを前提としましたが、 実際の回路でタイミングのズレないクロック信号を作ることは不可能です。

例えば、単相クロック同期回路ではすべての FF に入力されるクロック信号は同時であることを仮定して設計するため、可能な限り、クロック信号のタイミングがずれがないように設計しますが、どうしてもズレは生じます。

設計の段階で仮定したクロック信号のタイミングと実際のタイミングのズレをクロックスキューといいます。

クロック信号のズレは、早くも遅くもなります。このズレによってセットアップ制約とホールド制約の違反が発生すると回路は正しく動作しなくなります。そのため、タイミング解析では FF 間のパスの遅延だけではなくクロック信号の遅延も可能な限り含めて見積もります。

Data Arrival Time と Data required Time

タイミング解析は、Data Arrival Time と Data Required Time を比較することでセットアップ制約とホールド制約についての違反を確認します。詳しくは下で説明しますが、セットアップ制約とホールド制約それぞれの確認のために見積もり方が異なる Data Arrival Time が使われます。また、それぞれの確認のために異なる Data Required Time が使われます。

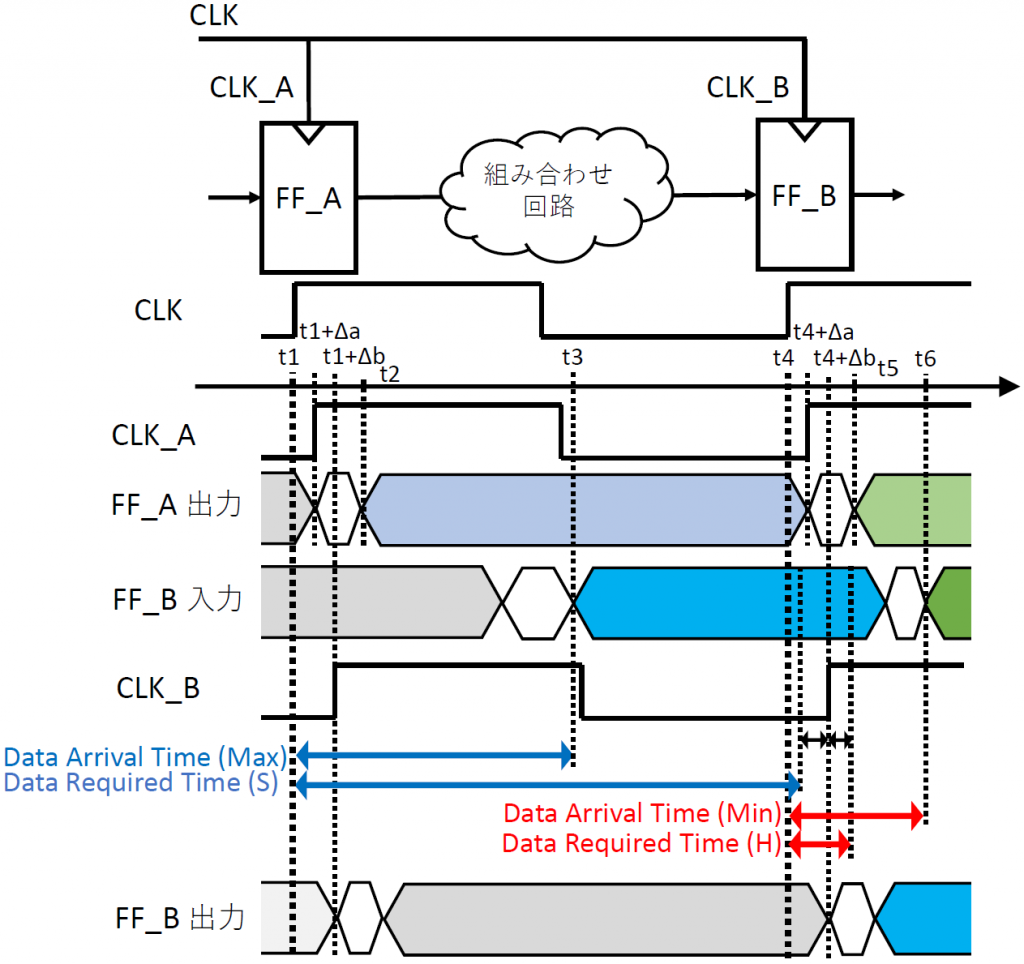

下の図を使って説明します。状況は上の図と同じですが、クロック信号にソースがあり、FF_A と FF_B に入力されるクロック信号 (CLK_A, CLK_B) にそれぞれズレが生じています。CLK と CLK_A のズレを Δa、CLK と CLK_B のズレを Δb とします。

Data Arrival Time は値を取り込む FF に値が届く時間を表します。ソースのクロック信号の立ち上がりエッジを起点に、値を出力する FF と組み合わせ回路を経て値を取り込む FF の入力に信号が到達するまでの時間です。セットアップ制約の違反を確認する場合は最大遅延を計算し、ホールド制約の違反を確認する場合は最小遅延を計算します。「見積もり方が異なる」とは、最大遅延で見積もるか最小遅延で見積もるかの違いです。

上の図で、最大遅延で見積もられた Data Arrival Time (Max) は t1 から t3 までの時間です。その計算では Δa、FF_A から値が出力されるまでの最大遅延、組み合わせ回路の最大遅延などが足し合わされます。

最小遅延で見積もられた Data Arrival Time (Min) は t4 から t6 までの時間です。その計算では Δa、FF_A から値が出力されるまでの最小遅延、組み合わせ回路の最小遅延などがたし合わされます。

Data Required Time は目標のクロック周期で回路を動作させた場合に値を取り込む FF が正しく値を取り込むためのタイムリミットを表す時間です。Data Arrival Time と同様にソースのクロック信号の立ち上がりエッジを起点に計算されます。セットアップ制約の違反を確認する場合はセットアップ時間を考慮した時間 (Data Required Time (S))、ホールド制約の違反を確認する場合はホールド時間を考慮した時間 (Data Required Time (H)) が Data Required Time になります。Data Required Time は、確認する制約によって異なる時間に注目しています。

上の図で、Data Required Time (S) は (Δb + クロック周期 – FF_B のセットアップ時間)です。Data Required Time (H) は (Δb + FF_B のホールド時間)です。

Data Arrival Time は値を出力する側の FF に注目し、Data Required Time は値を取り込む側の FF に注目します。

スラック

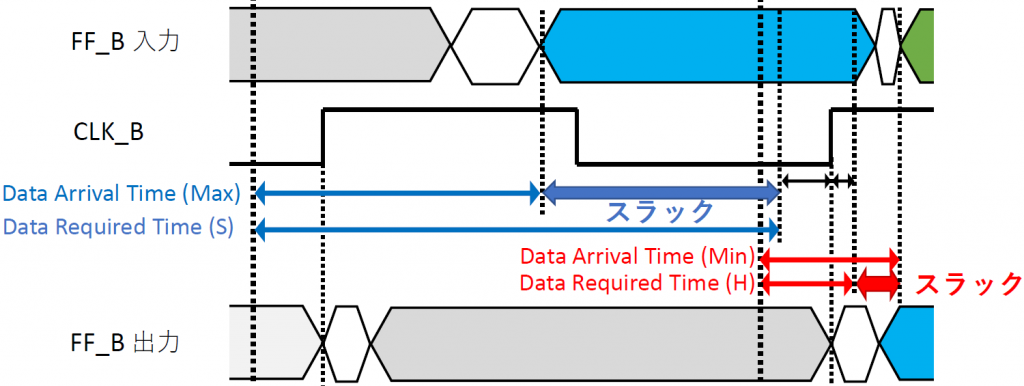

スラックは Data Arrival Time が Data Required Time に対してどのくらい余裕があるかを表す値です。

スラックの値が正であればタイミングに余裕があり、負であればタイミング違反となります。したがって「タイミングはメット (MET)する」とは、すべてのパスについてスラックの値が正であることです。

上の図の一部にスラックを追記して示します。

セットアップ制約の違反を表すスラック (青) は (Data Required Time (S) – Data Arrival Time (Max)) で計算し、ホールド制約におけるスラック (赤) は (Data Arrival Time (Min) – Data Required Time (H)) で計算します。

確認する制約の違いでスラックを計算する引き算の前後が逆になり混乱しますが、セットアップ制約とホールド制約を満たすということは、スラックの値が正、つまり Data Arrival Time (Max) と Data Arrival Time (Min) が Data Required Time (S) と Data Required Time (H) の間に入っていれば良いということです。

このように、タイミング解析により、設計している回路の遅延が計算されて目標の動作周波数で動くかどうかを確認できます。

これまで説明してきたタイミング解析は、特に静的タイミング解析 (Static Timing Analysis, STA) と呼ばれる解析です。上で説明した値は回路図さえあれば計算できるため、静的な手法になります。

静的があるのでもちろん動的タイミング解析もあります。これは回路に入力パターンを与えて動作させるシミュレーションによってタイミング解析をします。時間はかかりますが、入力パターンが決まっている場合には静的タイミング解析よりも最悪のケースのマージンを少なく設計できる可能性もあります。

タイミング解析は、設計している回路の遅延を計算してクリティカルパスを教えてくれますが、その回路をより高性能にする方法は教えてくれません。FPGA で一般に設計される単相クロック同期回路をより高性能な回路にするにはクリティカルパスの遅延を小さくしないといけませんが、それにはアルゴリズム設計やアーキテクチャ設計の段階などで改善をする必要があります。

まとめ

今回はタイミング解析について掘り下げて説明しました。

今回でこのシリーズの記事は終了になります。これまで説明してきた内容が高性能な回路を設計する手助けになれば幸いです。

東工大 佐藤真平