FPGA の設計は様々な言語で行うことが出来て、ツールもかなり複雑になっているので、ここでは VHDL による最も簡単な LED 点滅回路の作成フローを解説します。以下、

- Vivado の起動と新規プロジェクトの作成

- ソースコード (VHDL) の作成

- 制約ファイル (XDC) の作成とビットストリーム・ファイルの生成

- FPGA への書き込み

の順で解説します。

Vivado の起動と新規プロジェクトの作成

1.Vivado を起動します。類似のものに Vivado HLS というものがありますが、これは別のアプリケーションです。

2.Vivado を起動したら、Quick Start の Create Project、もしくは File -> Project -> New からプロジェクトの新規作成を行います。

FPGA の設計は様々な言語で行うことが出来て、ツールもかなり複雑になっています。

今回は、VHDL による LED 点滅回路を用いて Vivado の基本的な設計の流れを解説します。

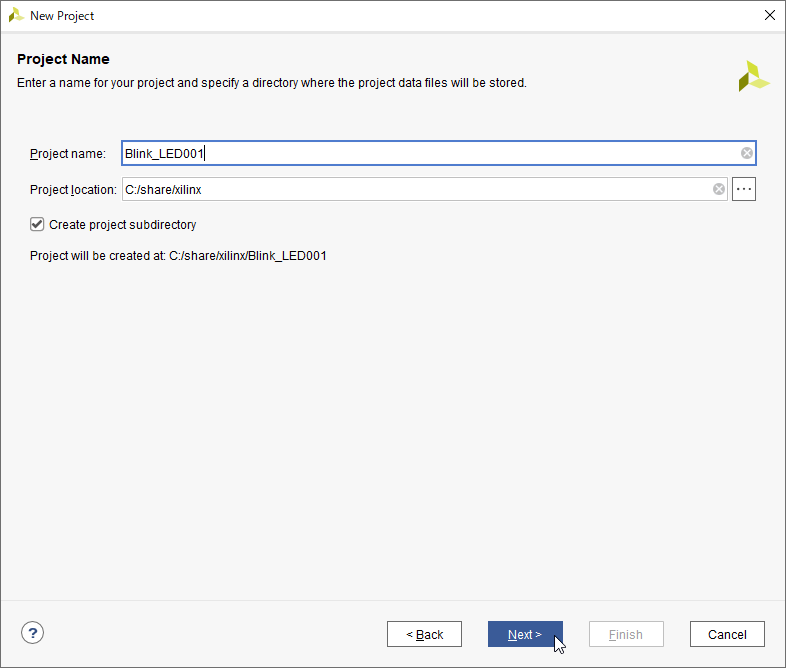

3.プロジェクト名と保存先を指定します。

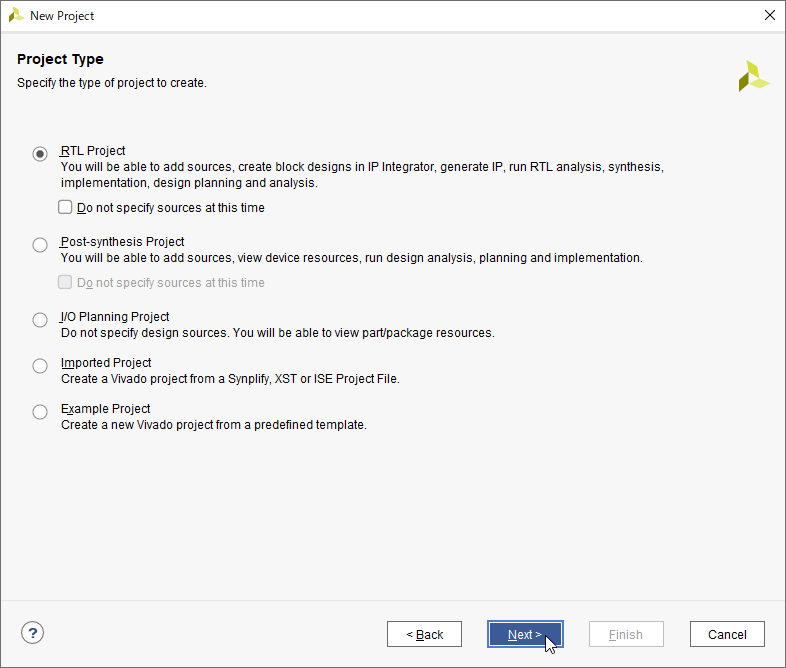

4.次に一番上の RTL Project を選択します。

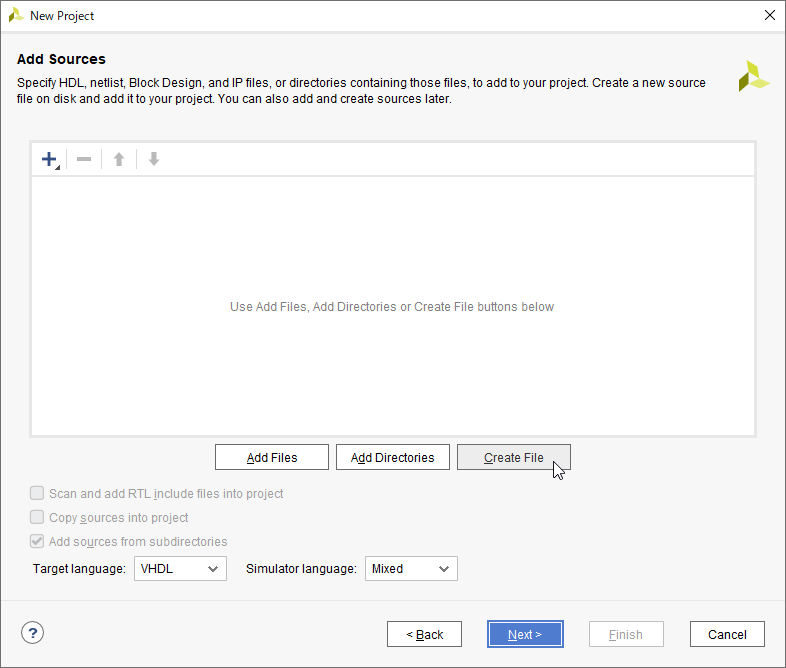

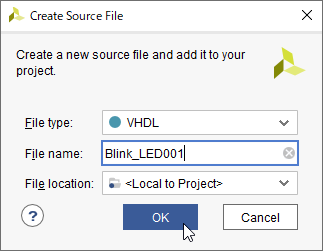

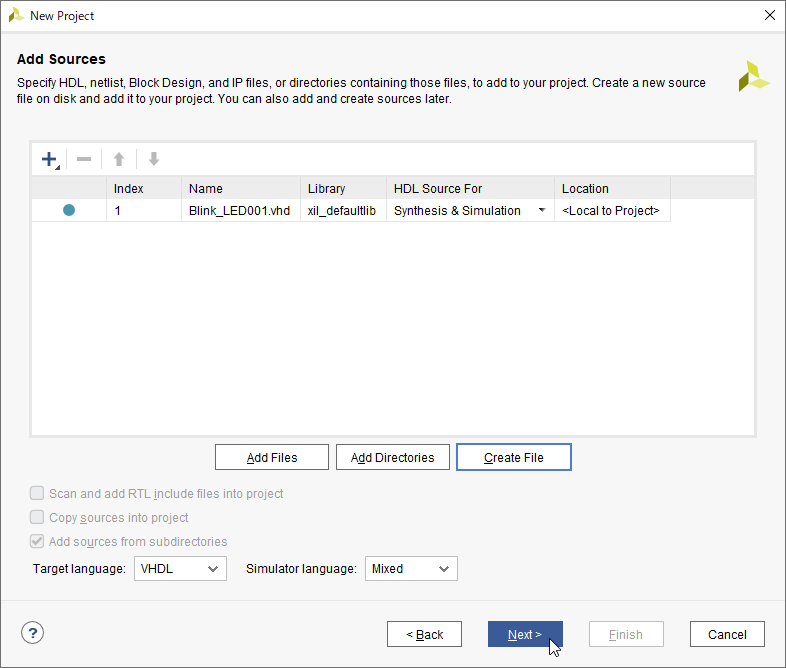

5.ソースコードの追加画面になるので、右下にある “Create File” をクリックして新規ファイル(ここでは VHDL を選択)を作成します。ファイル名はプロジェクト名と同じにしました。

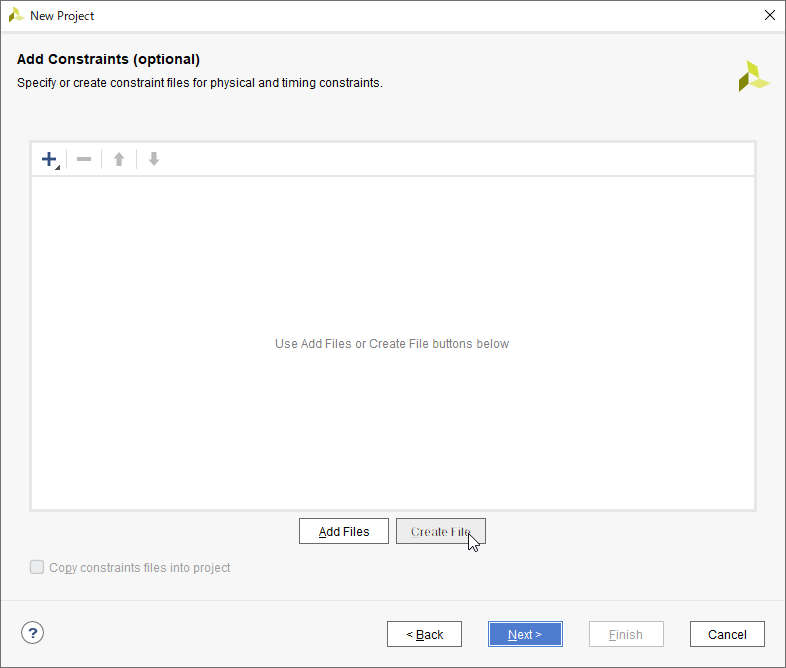

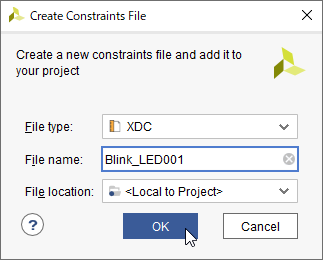

6.続いて、制約ファイルを作成します。これもここではプロジェクト名と同じにしました。

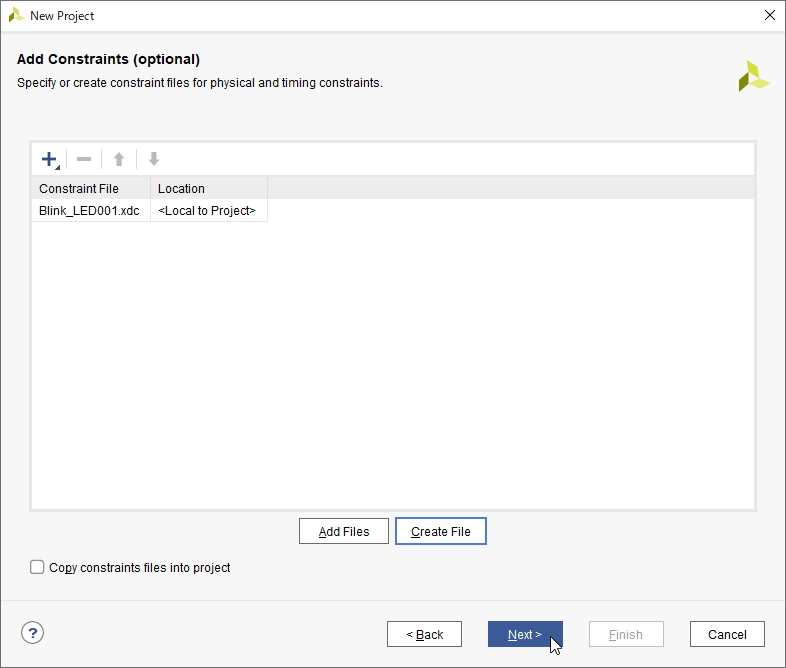

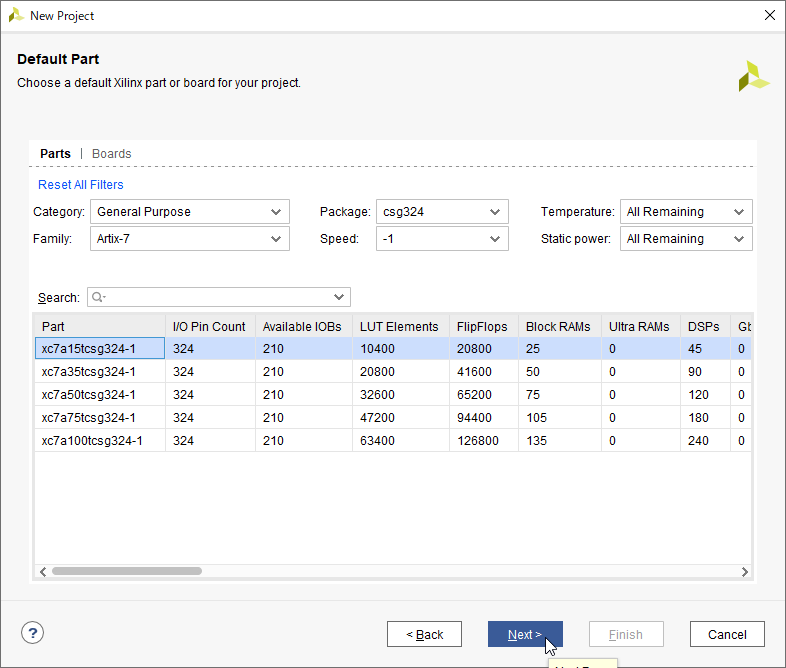

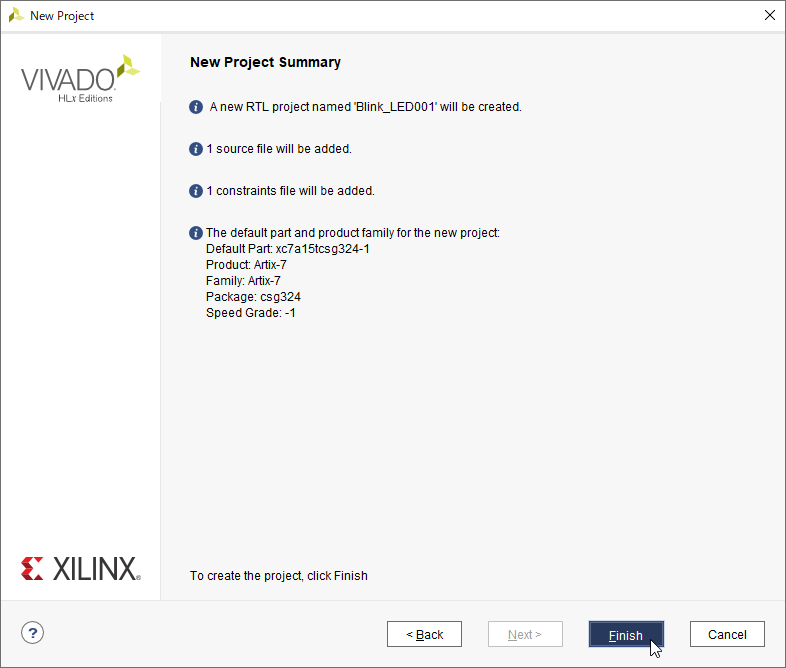

7.使用するボードに搭載されている FPGA を指定します。パッケージの他に、スピードグレードも指定する必要があります。

ソースコード (VHDL) の作成

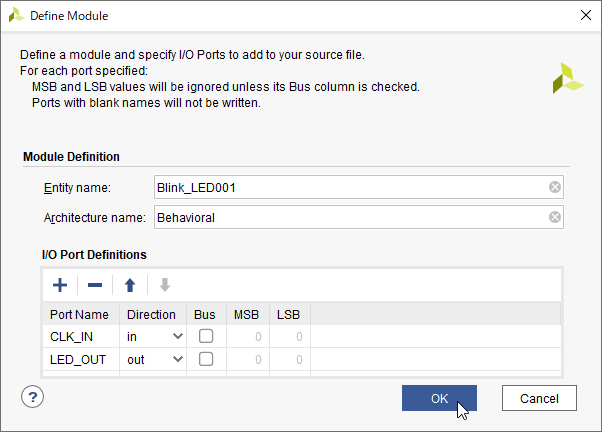

8.以上でプロジェクトが出来ますが、続いてソースコードの作成ウィザードが始まります。エンティティ名は先程指定した VHDL ファイルの名前と同じに、ポート名に “CLK_IN” と “LED_OUT” の2つを追加します。ポート名とは、入出力名のことで、これがそのまま端子名となります。

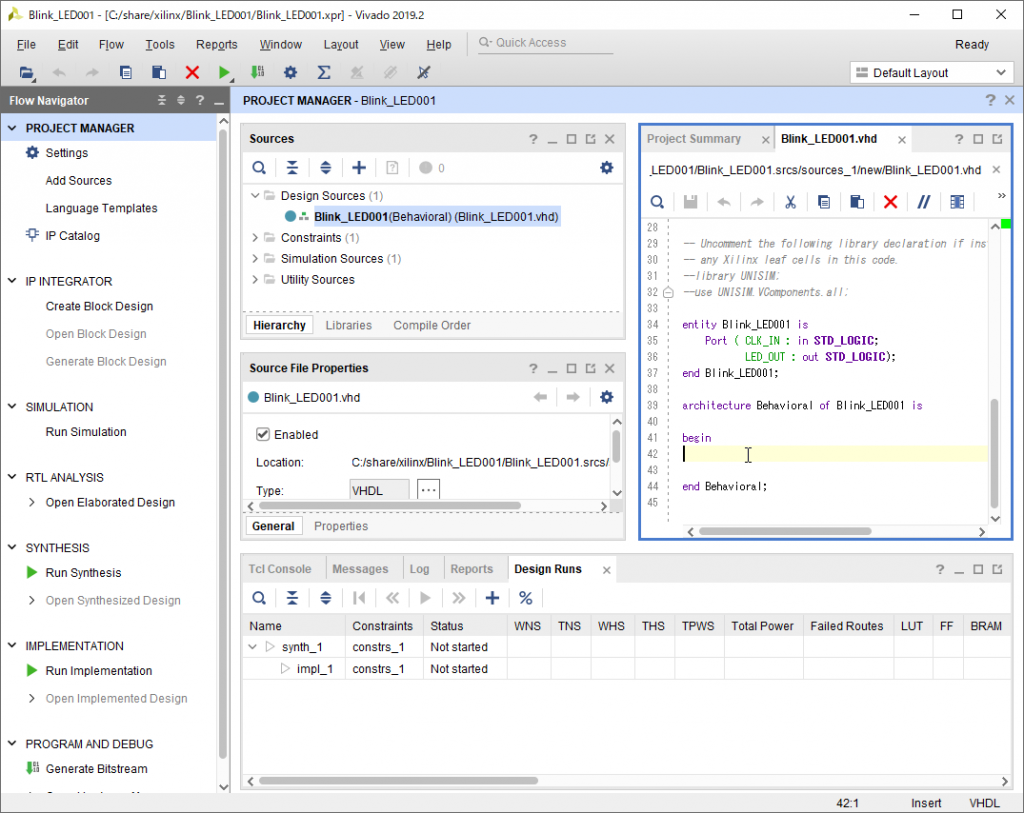

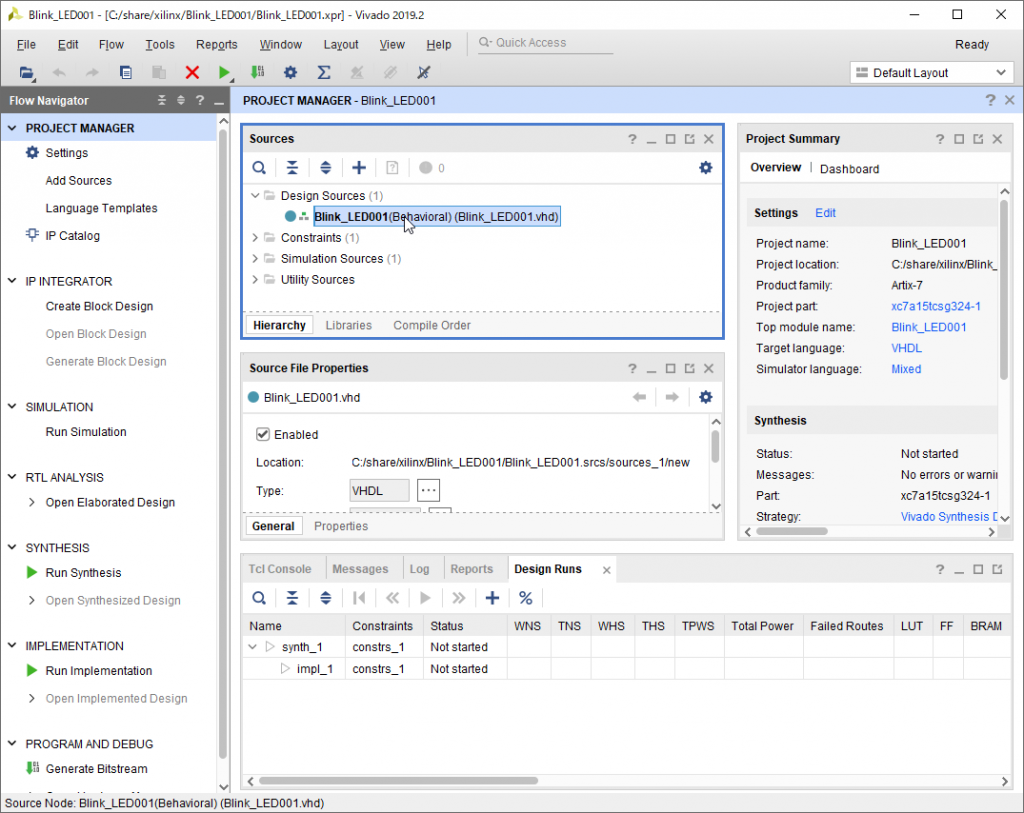

9.これで VHDL ファイルが作成されるので、SourcesのDesign Sources にある “Blink_LED001” をダブルクリックすると、編集できるようになります。

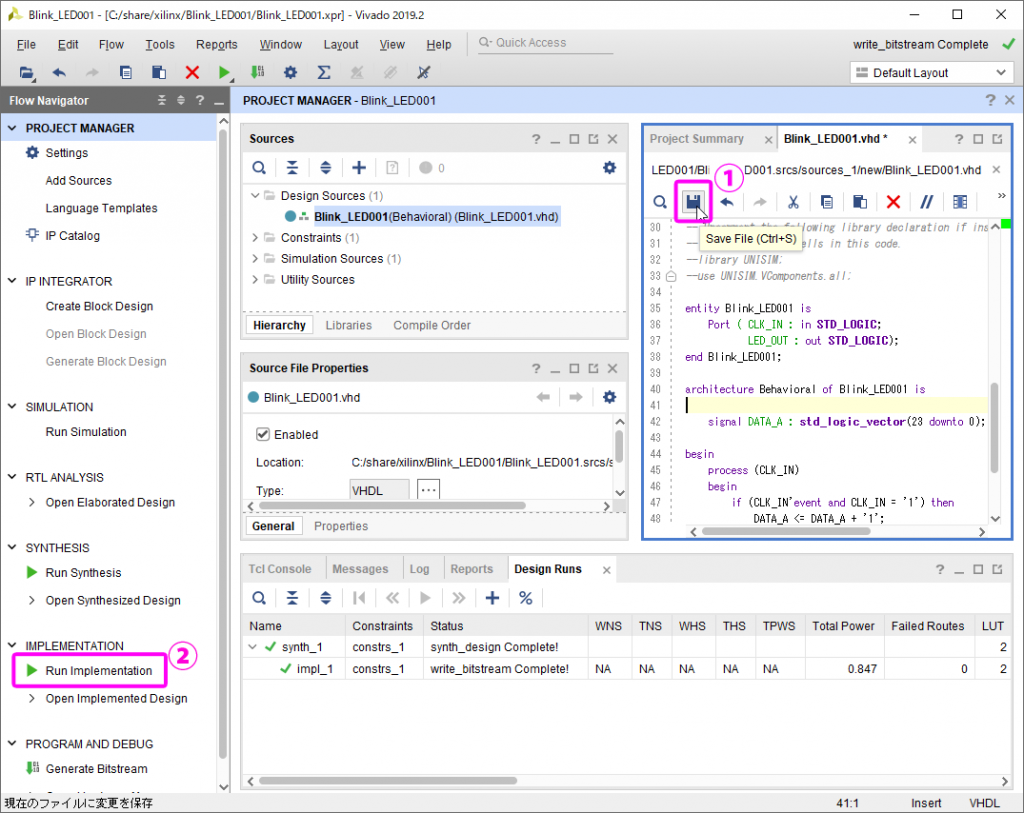

10.先程のウィザードで指定したエンティティやポートの指定が完了しているので、architecture 以降を追記して、下記のようにします。ここで冒頭に、”use IEEE.STD_LOGIC_UNSIGNED.ALL;” も追記してください。これは+演算子を使用するためのものです。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity Blink_LED001 is

Port ( CLK_IN : in STD_LOGIC;

LED_OUT : out STD_LOGIC);

end Blink_LED001;

architecture Behavioral of Blink_LED001 is

signal DATA_A : std_logic_vector(24 downto 0);

begin

process (CLK_IN)

begin

if (CLK_IN'event and CLK_IN = '1') then

DATA_A <= DATA_A + '1';

end if;

end process;

LED_OUT <= DATA_A(24);

end Behavioral;

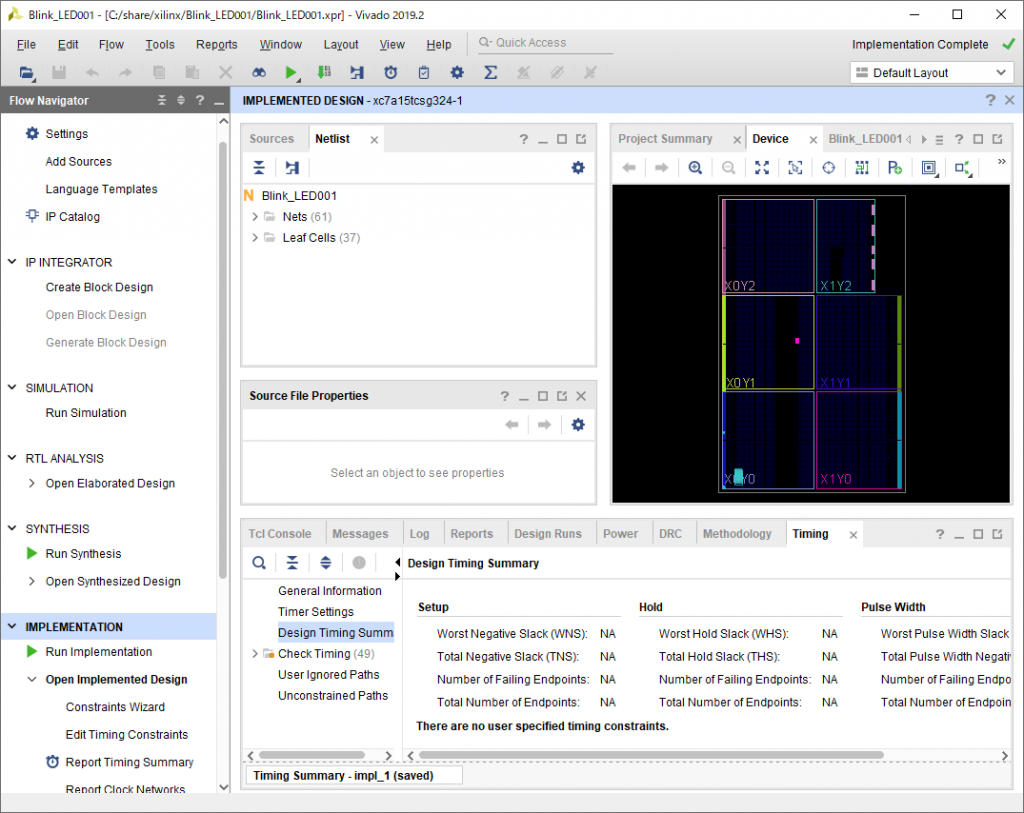

11.コードが出来たら、① Save ボタンでファイルを保存し、② 左下の方にある “Run Implementation” をクリックします。

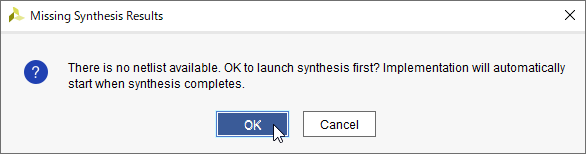

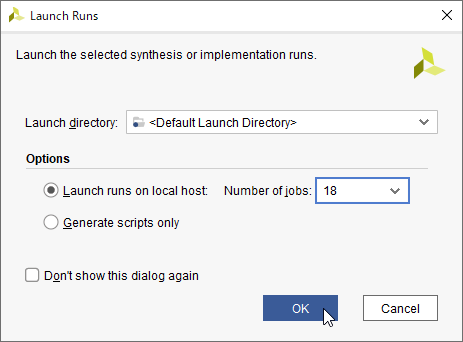

12.論理合成も行うかの確認と、実行ジョブ数を聞かれるので、そのまま進みます。

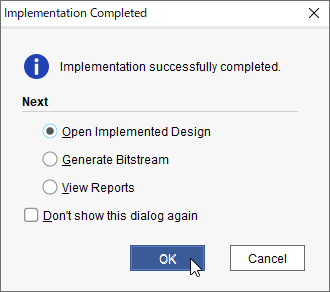

13.論理合成、インプリメンテーションが無事完了すると下記のメッセージになるので、”Open Implementation Design” を選択して、再度プロジェクトマネージャに戻ります。

制約ファイル (XDC) の作成とビットストリーム・ファイルの生成

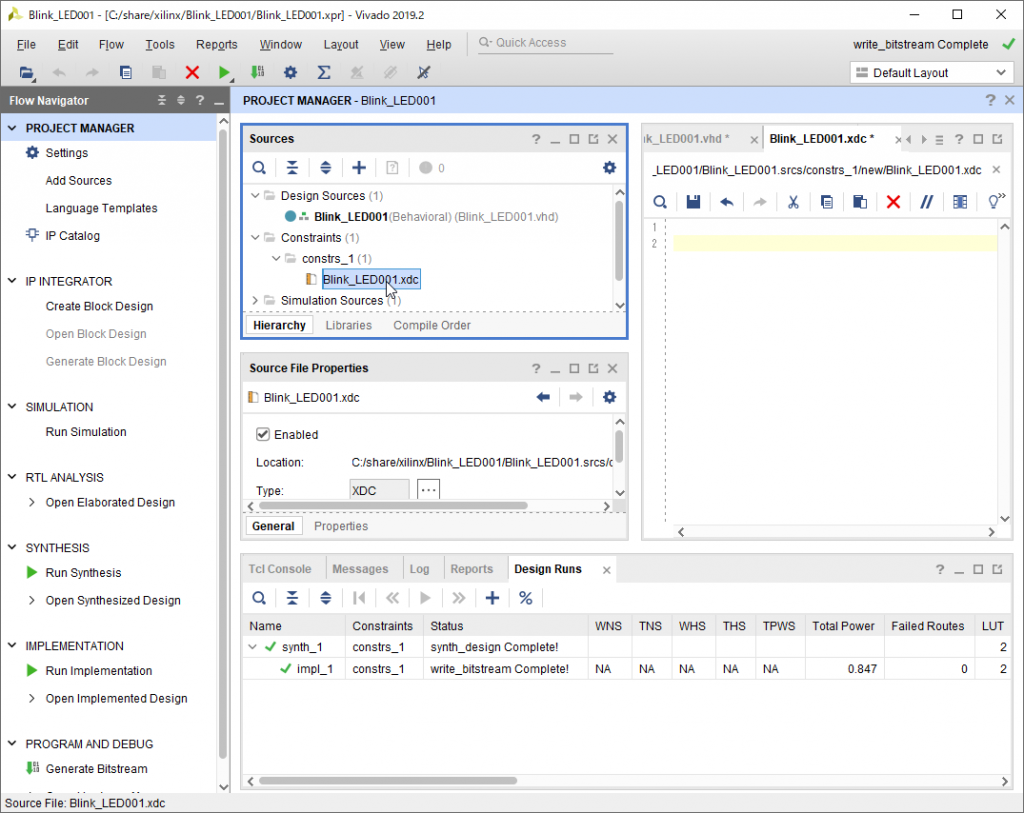

14.次に制約ファイルを記述します。ファイル自体は既に出来ているので、Sources の Constraints -> constrs_1 の下の “Blink_LED001.xdc” をダブルクリックして編集します。

15.使用するボードのクロック入力端子、LED 出力端子に合わせて、下記のように記述します。(下記例はクロック入力端子 CLK_IN が T4 番ピン、LED出力端子 LED_OUT が B6 番ピンの場合です。)

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property PACKAGE_PIN T4 [get_ports CLK_IN]

set_property PACKAGE_PIN B6 [get_ports {LED_OUT}]

set_property IOSTANDARD LVTTL [get_ports CLK_IN]

set_property IOSTANDARD LVTTL [get_ports {LED_OUT}]

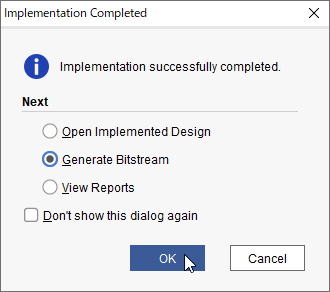

16.VHDL ファイルと同様に、保存したら、”Run Implementation” を再度実行します。成功すると下記のようになるので、今度は “Generate Bitstream” を選択してビットファイルを生成します。

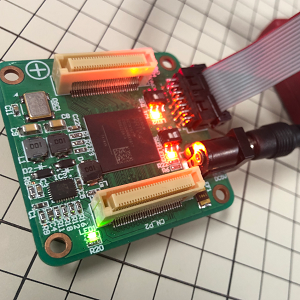

FPGA への書き込み

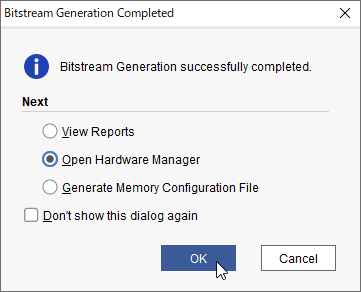

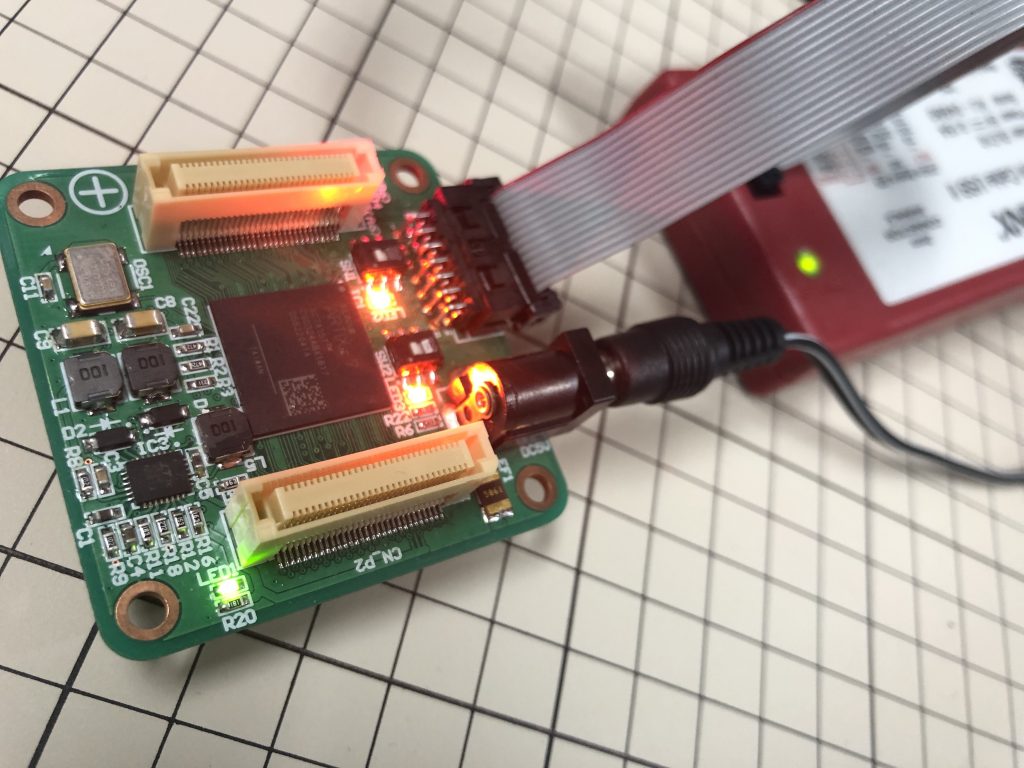

17.ビットストリーム・ファイルの生成が完了すると下記のようになるので、各ボードに合わせて FPGA へ書き込めば完成です。Xilinx 標準の書き込み器(Platform Cable USB II 等)で書き込む場合は、ボード接続、電源投入後に下記の “Open Hardware Manager” で書き込めます。

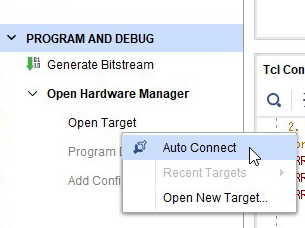

18.最初にボードを接続した際は左下の Open Hardware Manager -> Open Target を左クリックして “Auto Connect” を選択します。

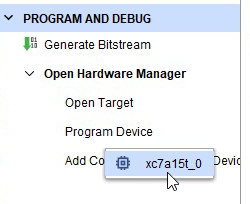

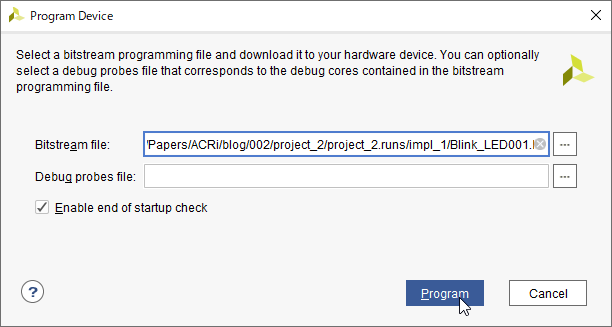

19.接続できると、その下の Program Device が選択できるようになるので、これをクリックして対象の FPGA デバイスを選択します。

20.そうすると下記のように書き込むビットストリーム・ファイルの選択になるので、このまま進めば書き込みが開始されます。

すすたわり