自分で基板を作るようになると、FPGA のどの端子にどの信号をつなげばよいか悩むことになるでしょう。

FPGA は論理回路や配線も自由にできる IC だから、どこにつないでも同じだと考える人がいるかもしれません。しかし、データシートを読むと、FPGA の I/O はどれも同じではなくバラエティーに富んだ機能があることに気づかされます。どうやって処理すればよいか悩ましいピンもあります。

FPGA の端子には電源やコンフィグなどの専用ピンだけでなく、普通のユーザ I/O に見えるピンにも特別な機能が割り当てられた多目的ピンがあります。

今回は、Xilinx の FPGA のうち、特に7シリーズの FPGA について基板を自作する人たちのために I/O ピンの使い方を説明します。

I/O ピン

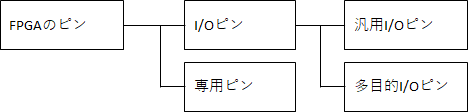

FPGA のピンにはユーザ論理回路の入出力に使える I/O ピンと、そうでない専用ピンがあります。

I/O ピンには、特別の機能を兼ね備えた多目的 I/O ピンと、特別な機能を持たないただの汎用 I/O ピンがあります。たいていの I/O ピンは特別な機能を備えていて、何の機能もない I/O ピンはむしろ稀です。

専用ピンというのは、電源やモード設定、コンフィギュレーションに使わます。

I/O バンク

I/O ピンについて説明する前に、まず I/O バンクについて説明しなければなりません。

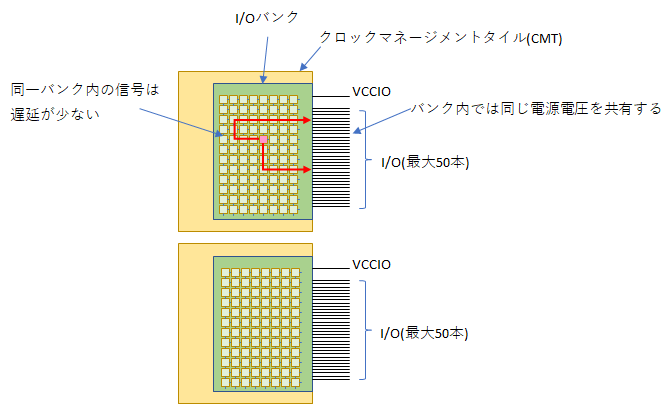

7シリーズ FPGA の I/O は、50個の I/O をまとめたバンク (Bank) という単位で構成されています。バンクに含まれる I/O ピンは同じ電源電圧を共有するという決まりごとがあります。また、同じバンクにある I/O は FPGA 内の距離も近く、クロックマネージメントタイル (CMT) も共有しているので、信号間のタイミングの差が小さくなります。つまり、同じような機能の端子や、同じ周辺 IC に接続する信号は同じバンクに配置することが鉄則です。

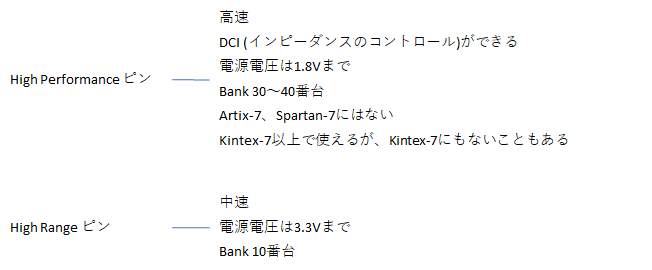

バンクにはそれぞれ番号が付いていて10番台は主に汎用の I/O です。30~40番台はちょっと高速な用途に使われます。

また、コンフィグ用の0番、ギガビットトランシーバ用の100~200番台、ZYNQ の MIO の500番台は、普通のユーザ I/O ではなく専用ピンの塊です。

Kintex-7 と Virtex-7、および XC7Z030 以上の ZYNQ は High Performance バンクと言って高性能の I/O が使えるものもありますが、HP バンクは30~40番台に割り当てられます。そのため、30番台は高速な用途に使うのが普通です。

I/O バンクの中ですべてのピンは同じ電源電圧を共有しなければなりません。例えば、バンク15のあるピンから 1.8V 規格の信号を出力しつつ別のピンから 3.3V 規格の信号を出力する、といったことはできません。ただこの制限は出力にのみ適用され、I/O 電圧が異なっていても入力だけならできることもあります。詳しくは後述します。

基板を設計する際には、FPGA に接続したい周辺 IC がどのような電圧のロジックで動作するかを調べて、同じ電圧規格の信号は極力同一のバンクにまとめましょう。もし、電圧の種類が多すぎてバンクが足りなくなったり、1つの電圧振幅の信号が多すぎてバンクに収まりきらなくなった場合は、ひとまわり大きなパッケージを選択する必要が出てきます。

ピンの命名規則

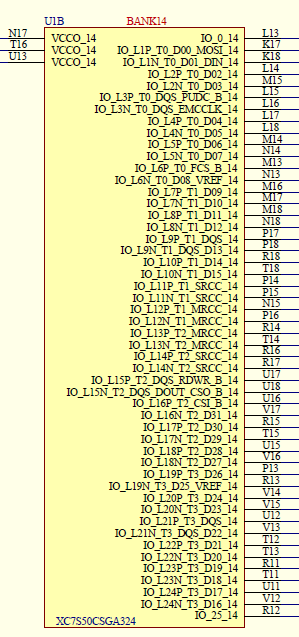

7シリーズ FPGA の I/O ピンの命名規則は

- IO_LXXY_Tn_M_# ・・・差動ペアの I/O ピン

- IO_XX_# ・・・シングルエンドの I/O ピン

となっています。(斜体の文字は番号や機能に置き換わります。) Lは差動ペアであることを表しています。XX はバンク内の差動ペアの固有番号で1~24です。Y は差動ペアとして使った場合の正側 (P) または負側 (N) を表します。#はバンクの番号です。M は多目的ピンの機能です。

バンクの中にはメモリバイトグループというサブグループがあり、n はその番号 (0~3) です。バンク内の信号は強く結合されているため少ない時間差で入出力されますが、メモリバイトグループに属するピンはさらに強く結合されています。

例えば、XC7S50-1CSG324C には IO_L3P_T0_DQS_PUDC_B_14 という端子がありますが (上の図4参照)、これはバンク14で PUDC_B と DQS という2つの多目的ピンを兼ねていて、メモリバイトグループ0に属し、差動ペアとして使う場合は3番目の P 側であることを意味しています。

1つのバンクに差動ペアは1~24までの24組ありますが、これらは48個のシングルエンドとしても使うことができます。なお、バンクの上下1個は差動ペアになれないシングルエンド専用のピンがあります。

多目的 I/O ピンの機能

この節では、多目的 I/O ピンの機能について説明します。

VREF

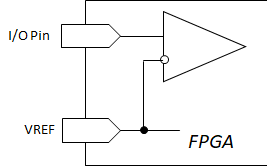

各バンクには最大2個の VREF ピンがあります。VREF ピンは基準電圧と比較して高ければH、低ければLとするような I/O 規格 (例えばSSTL) で使われます。VREF を使う I/O 規格にする場合、2個の VREF は相互につなぐ必要があります。例えば、DDR3 メモリを使う場合はここに 1/2 VCCIO を与えます。(内蔵VREFを使ってVREF多目的ピンをという選択肢もあるが、あまり使ったことがない)

差動ペア

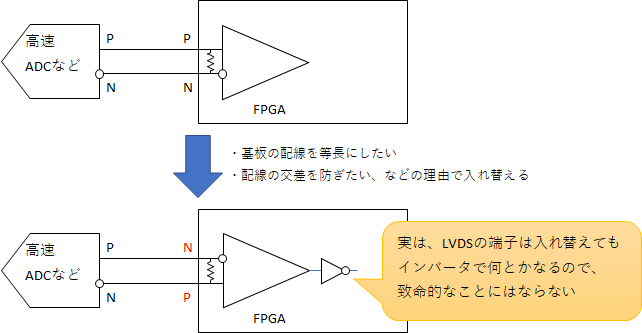

各バンクに24個ずつある差動ペアは、P 側と N 側になれるピンが決まっています。

ただ、実際には FPGA の中では論理を反転させるコストは限りなくゼロに近いので、どちらにつないでも基板の作り直しを伴う致命的な失敗になることは少ないでしょう。慣れてきたら基板の配線をすっきりさせるために反転させることもできますが、慣れていないうちは P 側の信号は P 側に、N 側の信号は N 側につなぎましょう。

クロック

MRCC と SRCC という端子が各バンクにありますが、これらはクロック入力ピンです。これらの端子は差動信号にも対応していて、各バンクに MRCC と SRCC は2つずつあるので、MRCC で4本、SRCC で4本、計8本のクロック用 I/O があります。こんなにたくさんのクロックを使うことはまずないでしょう。使わなかったクロック用端子は一般の I/O として利用できます。各バンクのクロックは FPGA 全体で使っているグローバル配線 (BUFG) のクロックを中でルーティングできるので、必ずしもバンクごとの MRCC や SRCC につなぐ必要はありません。

MRCC は BUFG、BUFR、BUFIO および MCMM/PLL を駆動することができ、SRCC は BUFR、BUFIO および MCMM/PLL を駆動することができます。その違いは BUFG を駆動できるかどうかです。SRCC の「S」はシングルリージョンを意味するので、そのバンクでのみ使われるクロックの入力に使います。(実際には MMCM につないだり、一般配線を経由して BUFG につなぐこともできますがが推奨はしません。やはりシステムクロックは MRCC に入れるべきです。)

FPGA の各バンクには MRCC があって、その P 側にクロックを入れれば FPGA 全体で利用できるので、あまり悩むことはないでしょう。

ちなみに裏技的ではありますが GTX の REFCLK に入れた GTX 用のクロックは、7シリーズでは IBUFDS_GTE を使って一般のロジックに引き出してくることができます。Spartan-6 のときには GTP を使わないとできなかった配線の引き回しが7シリーズではできるので、MRCC や SRCC を一切使わないデザインも可能です。

DQS

DQS はデータ (DQ) のストローブに使います。DQS は出力だけではなく入力にもなる双方向ピンで、データのトグルに使われる半クロック的な存在です。ただしそれは、メモリインタフェースに使う場合の多機能ピンなので、ユーザ回路ではまったく気にする必要はありません。

アナログ入力

7シリーズ以降の FPGA は逐次比較型の AD コンバータを内蔵しています。この AD コンバータは GND に対する電圧を測るシングルエンドモードだけではなく、VP と VN 間の電圧を測る差動モードにも対応しています。AD 変換器の入力は16個あるため、AD 変換用ピンは AD0P から AD15P、AD0N から AD15N の計32本があります。もちろん AD 変換を使わなければ普通の I/O になるので気にする必要はありません。ちなみに、16チャネルあるといっても同時サンプリングではなく、マルチプレクサで切り替えていくタイプです。

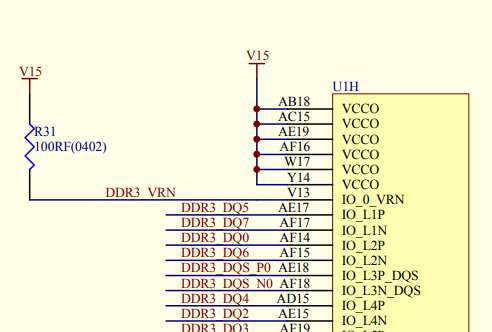

VRN と VRP

Kintex-7 以上の FPGA では高性能な HP I/O バンクが使えるものもあり、HP バンクには VRP と VRN というピンがあります。

VRN と VRP には DCI (Digital Controlled Impedance) という機能で使われる参照抵抗を接続します。ここには所望のインピーダンスの2倍の抵抗を接続します。例えばインピーダンス 50Ω の配線の場合は、VRP を 100Ω でプルダウン、VRN は 100Ω でプルアップします。

DCI は HP バンクでのみサポートされる機能なので、Artix-7 と Spartan-7 にはありません。

リセット

7シリーズ FPGA にはいくつかのリセットがあります。

普通の FPGA の場合

PROG_B は、Artix-7、Kintex-7、Virtex-7 に存在する端子で、L にするとコンフィギュレーションが最初からやり直されます。いわばロジック回路のリセットです。

ZYNQ の場合

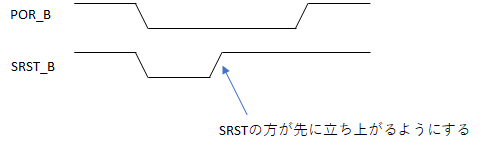

ZYNQ には PS_POR_B と PS_SRST_B という2つの信号があります。どちらも PS をリセットして FSBL から再スタートするのですが、POR_B はパワーオンリセット、SRST は JTAG コネクタからのデバッグリセットとして使われます。

注意すべき点としては、SRST のほうが POR よりも先にディアサート (Hになる) されるようにする必要があります。ZYNQ は FSBL よりも先に BootROM というのが動いていますが、BootROM の動作中に SRST を L にしてはいけないためです。SRST は使わないように H にプルアップしたままにして、リセットは POR_B でかけるのでもよいでしょう。

ちなみに、筆者が最初に作った ZYNQ ボードでは SRST をオープンにしてしまうという致命的なミスをしました。これらのリセット端子にはプルアップ抵抗が入っていないので、オープンにしてはいけません。必ずプルアップ抵抗などで外に引き出してください。

各バンクの特徴

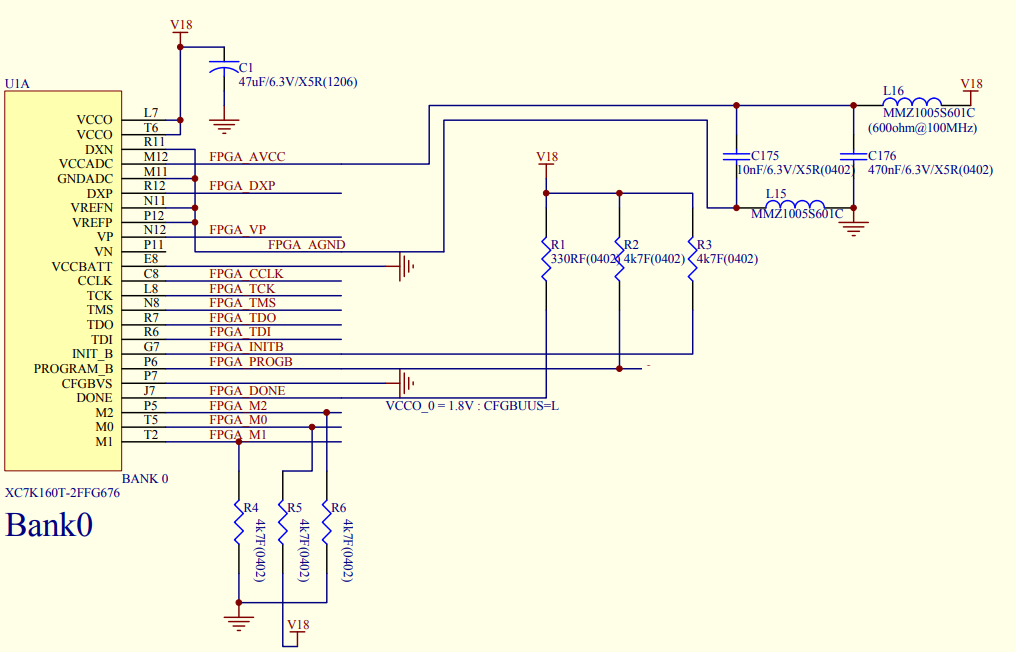

バンク0

Bank 0 はすべての FPGA に存在し、コンフィギュレーションや FPGA のモード設定に必要な専用ピンが凝縮されています。

このバンクのピンの機能を1つずつ見ていきましょう。なお、Xilinx FPGA の慣例として、端子名の後にアンダーバーを書いてバンク番号を書くことになっています。

電源

VCCO_0 は Bank0 の I/O 電源ピンです。JTAG やコンフィギュレーション信号の振幅は VCCO_0 によって決まります。

VCCO_0 は 2.5V、3.3V、1.8V、1.5V などが選択できますが、Bank0 はコンフィギュレーションにも使われるので 3.3V か 1.8V を使うことになるでしょう。なぜならば 1.5V 以下で動くコンフィギュレーションメモリは事実上存在しないからです。

注意しなければならないのは、JTAG 信号も Bank0 の VCCIO で決まることです。もし、NVidia の GPU や Intel CPU など大規模な IC を FPGA 外に置き、JTAG 信号をデイジーチェーンで接続する場合は、JTAG 信号の電圧規格が一致するようにしなければなりません。

VCCBATT_0 はバッテリをつなぐための電源です。なぜバッテリをつなぐ必要があるのかと疑問に思う人も多いと思います。いや、普通は思うでしょう。Xilinx FPGA はコンフィギュレーション ROM のコピーを防ぐため、コンフィギュレーションデータの暗号化に対応しています。簡単に言うと、コンフィグ ROM には暗号化したビットストリームを書いておいて、FPGA の中の SRAM に復号化の鍵を書いておくというしくみです。

不正なユーザが解析したりコピーしようとして基板に細工をすると、電源を落として鍵が消えて起動しなくなるというわけです。正常動作時には電源 OFF しても暗号化キーを保持するためのバッテリバックアップ用の電源端子が VBATT です。普通のユーザはそんなことはしないので VBATT を使わないのですが、使わないならば VBATT は電源につなぐか GND に落としておかなければならないとされています。

ADC

7シリーズからは AD コンバータ「XADC」が内蔵されるようになったのですが、この AD コンバータは 1M サンプリングの 12bit ADC で、温度や電源電圧を測るだけではなく、ユーザが自由に使うこともできます。したがって、7シリーズからはバンク0にアナログ的なピンが追加されています。

ただしノイズまみれなので本格的な計測には向かない

VCCADC、GNDADC はその名の通り、FPGA の中の ADC の電源です。VCCADC には 1.8V を与えます。

ユーザ回路では AD コンバータを使わないし、電源電圧も測らないという場合でも、DDR2/3 メモリを扱う MIG はこの ADC で温度を計測してリフレッシュレートの決定に使っているので、使えるようにしておいたほうがよいでしょう。

1.8V が近くにないという場合は、設計が間違えています。バンク0の近くには必ず 1.8V を置いておくべきです。

VREFP と VREFN は ADC 用の基準電源で、ここには 1.25V を供給する必要があります。

バンク0は BGA パッケージの中心にあります。FPGA の狭い中心部分にはコア電源の 1.0V、ADC の VREF の 1.25V、VCCAUX や VCCADC の 1.8V、それから VCCIO_0 の電源と4種類の電源が必要になってしまい3密どころか4密になっています。この中で一番いらない電源は何かというと 1.25V の VREF です。VREF は GND につなげば内蔵リファレンスが使われるので、ぜひ内蔵リファレンスを使うようにしよう。

VP_0 と VN_0 は、ユーザ用の ADC のアナログ入力ピンです。使わなければアナログ GND につなぎます。

DXP と DXN

DXP と DXN は非常に謎が多いピンです。どうやら FPGA の中には温度計測用のダイオードが入っているらしく、汎用の温度監視 IC を DXP と DXN につなぐことで FPGA の温度が測れるというものらしいのですが、当然ながら使ったことはないし、使った回路を見たこともありません。使用しない場合は GND につなぎます。

一度使ってみたいですね。

モードピン

M0、M1、M2 はモードピンと言って、FPGA のビットストリームをどこから取得するかを決めるものです。このピンの値を変えることで、SPI ROM から起動したりパラレルフラッシュから起動したりすることができます。詳しくは後の記事で詳しく解説することにします。

なお、Spartan-6 では M0, M1 は専用ピンではなくユーザ I/O と兼用になっていたのですが、Spartan-7 からは専用ピンに戻りました。I/O と兼用して様々なトラブルがあったことは想像に難くありません。

7シリーズでは、SPI ROM からの起動にするのであれば、M2=L、M1=L、M0=H にします。これで Master Serial というコンフィギュレーションモードになります。ここでいう H レベルというのは、VCCIO_0 の電圧のことであることに注意してください。VCCIO_0 が 3.3V ならば H は 3.3V で、VCCIO_0 が 1.8V ならば H は 1.8V です。プルアップ抵抗の接続先には常に注意が必要です。

コンフィグピン

PROGRAM_B_0、CCLK_0、INIT_B_0、DONE_0 はコンフィギュレーションに使うピンです。コンフィグは奥が深いので、後の記事で詳しく解説します。

一般的には、Xilinx の I/O ピンで _B という名前が出てきたら負論理を表します。おそらく Bar の意味と思われます。つまり、読み方は「イニットビー」でもよいですが、「イニットバー」と呼ぶと通っぽく振舞えます。

JTAG

TCK、TDI、TMS、TDO は JTAG (ジェイタグ) といって、FPGA の書き込みやデバッグに使われます。開発中の基板ではこの端子を必ず基板上のどこかに出しておきます。本番稼働では使わないかもしれませんが、これがないとデバッグができません。

逆に言えば、本番用の基板では JTAG を隠すことで耐タンパー性を高めることができます。

CFGBVS_0

U を V で表記するラテン語でコンフィグバスと読むのかもしれませんが、違います。

おそらく、Bank Voltage Select の略でしょう。VCCIO_0 が 2.5V または 3.3V ならば CFGBVS_0 を VCCIO_0 に接続し、1.8V 以下ならば GND に接続します。平たく言えば Bank0 を 1.8V 以下にするならば GND につなぎます。

以上でバンク0の使い方についてざっと解説しました。次は一般の I/O に使われるバンクの説明です。

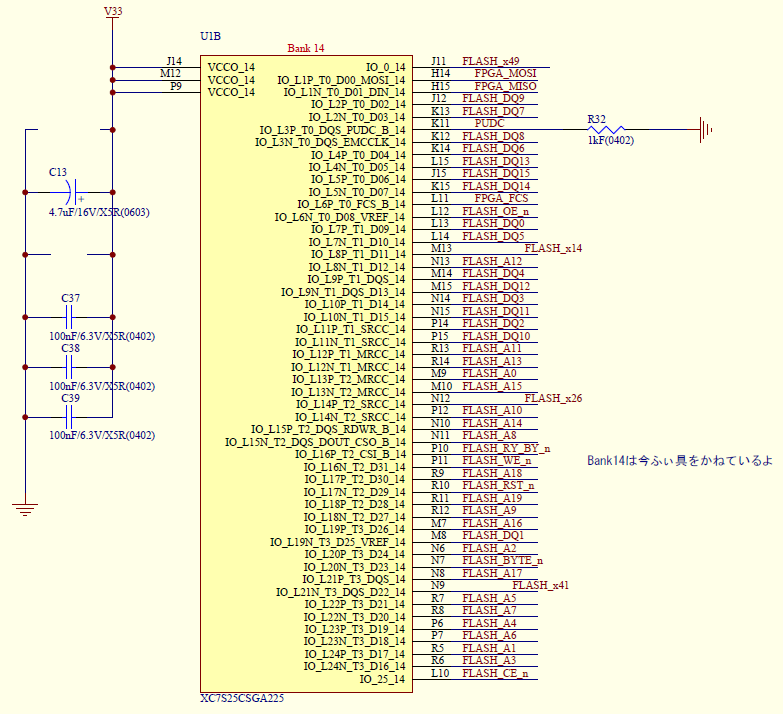

罠だらけのバンク14

バンク14はユーザ回路で使う信号が出入りする普通の I/O バンクのように見えますが、コンフィグ機能を兼ねているので少しだけ注意しなければなりません。

SPI ROM の信号

L1P のところには MOSI、L1N は DIN と書かれていて、L6P は FCS と書かれています。これはコンフィグ用の SPI ROM を接続するための多目的ピンです。もしパラレルフラッシュを使うのであれば、バンク14の数多くの端子にフラッシュ ROM のアドレスやデータを接続することになります。

VCCIO_14 はコンフィギュレーション用のメモリをつなぐバンクなので電圧は自由にできません。

実務上は VCCIO_14 は VCCIO_0 と同じ電圧にせざるを得ないのです。

PUDC

パドックではなく、Pull-Up-Down-Control の略でしょう。(Downかどうかは自信ない)

これは、電源投入およびコンフィギュレーション中に I/O ピンをプルアップにするかハイインピーダンスにするかを選択する端子で、GND につなぐと全 I/O ピンがプルアップにります。H レベル (すなわちVCCIO_14) につなぐとハイインピーダンスになります。直接つないでもよいですが、抵抗を介してつなぐ場合は 1kΩ 以下にすることという条件があります。

そもそも、なんでこんな機能があるかというと、コンフィギュレーション完了前の FPGA の端子を安全な状態にするためです。FPGA が起動する前のピンの状態がわかっていないと危険なことが起きる回路では、起動前にプルアップで H になることが分かっている必要があります。例えば、FPGA が起動する前や、コンフィグデータが壊れていた場合にモータを安全な状態に停止する必要があるような場合を考えてみてください。

コンフィグ中にハイインピーダンスになるとノイズを拾ってしまうので良くありません。そのため、PUDC は GND につないでプルアップを有効にすることを強く推奨します。

PUDC に気が付かずに作ってしまうと悲惨なことになります。

Spartan-3 や Virtex-5 の頃は HSWAP や HSWAPEN と言われていました。ハイインピーダンスにするのはホットスワップ(電源を入れたまま拡張基板を抜き差しすること)に対応する機器で需要があるのでしょう。

平凡なバンクの10番台

バンク15は AD コンバータのピンを兼ね備えているほかは、特に何の変哲もない普通の I/O です。

Kintex-7 の 676 ピンにはバンク12,13があり、これらも何の特色のないバンクです。

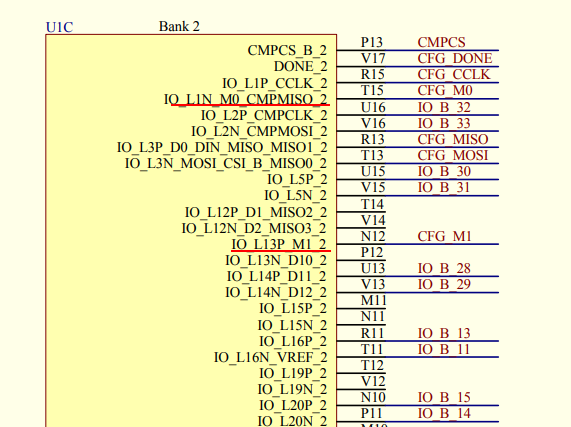

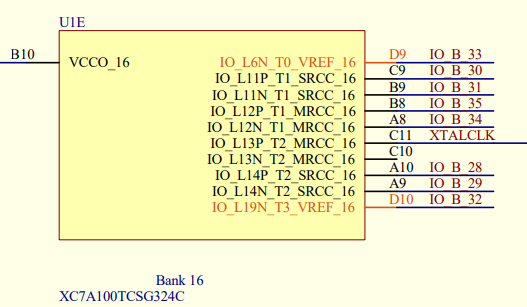

小さいバンク16

CSG324 ピンの Artix-7 ではバンク16は小さいバンクです。全ての I/O が引き出されているわけではなく、MRCC/SRCC と VREF だけが利用できるようになっている縮小されたバンクとなっています。が、クロック専用のバンクというわけではないので普通の I/O としても使えます。

例えば、1個や2個の LVDS の出力をしたいために 2.5V を使う必要があるけど、汎用のバンク15を 2.5V にすると残りの I/O ピンが 2.5V になってしまってもったいないという場合に使うといいかもしれません。

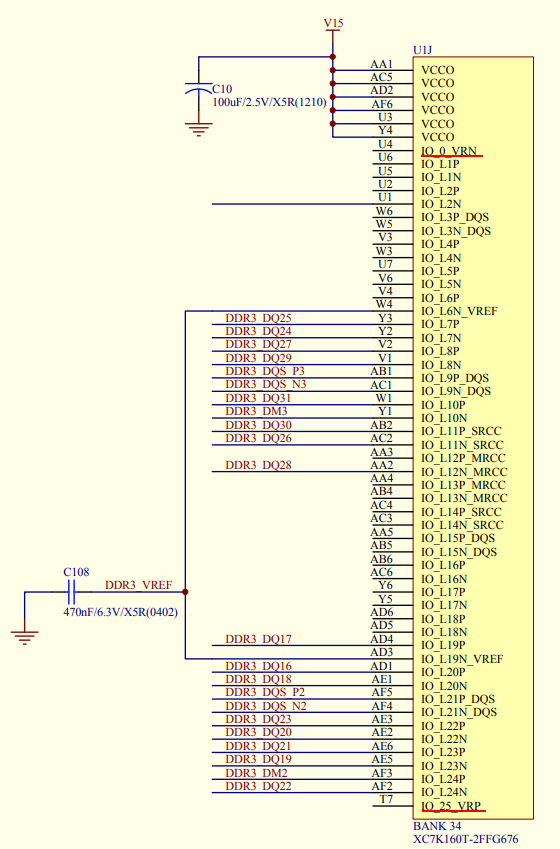

高性能なバンク32,33,34,35

繰り返しになりますが、Kintex-7 以上では30番台と40番台のバンクは高性能 (HP) バンクです。高性能バンクでは 3.3V の I/O が使えない代わりに、DCI というインピーダンスコントロールの効いた I/O が使えます。

これらのバンクでは VRN と VRP という DCI ピンがあります。Kintex-7 では隣り合うバンクどうしで DCI の参照抵抗情報を融通できるので、1か所のみに付ければよいという特例もあります。

LVDS

周辺 IC と差動信号で高速なインタフェースをするならば、ほとんどの場合 LVDS が選ばれます。

注意しなければならないのは、HR バンクで LVDS を使うのであれば VCCIO を 2.5V にし、HP バンクで LVDS を使うのであれば VCCIO を 1.8V にすることです。

この電圧にしないと配置配線の段階でエラーが出てツールが親切に教えてくれます。ずる賢い設計者が XDC ファイルをごまかして何とかビルドに通ったとしても、実際の信号は出てきません。つまり、2.5V のふりをした XDC ファイルを書いて実際に 1.8V や 3.3V の電源電圧を与えて LVDS 信号を出そうとしても、上や下に張り付いて出てこないのです。どうやってもだめなのです。

ややこしいのですが、7シリーズでは LVDS といったら 1.8V の HP バンクでの LVDS で、HR バンクでの LVDS のことは LVDS_25 といいます。

なお、電源電圧が 2.5V (HP バンクは1.8V) でなくても LVDS の受信だけならできてしまいます。ただし、ここにも罠があります。LVDS は 100Ω の終端抵抗を使って電流を電圧に変換して受信するのですが、シグナルインテグリティ向上のためこの終端抵抗はレシーバの直近に置くのがよいわけです。そのため、FPGA には終端抵抗が内蔵されていて DIFF_TERM という属性を ON にすると内蔵終端抵抗が使われるのですが、VCCIO が規定の電圧でないと DIFF_TERM が使えません。受信だけなら 3.3V バンクでもいいや・・と思っても終端抵抗が使えないのです。FPGA 外部に 100Ω の抵抗を置いて 3.3V バンクで受信すればいいんですが。

したがって、2.5V (HP バンクは 1.8V) 以外の VCCIO で LVDS を使うのであれば、送信はできないけど、受信は 100Ω の終端抵抗を外部につけるということになります。多少の不便はあるけれども何とか受信だけならできるのです。実際、2.5V の CMOS ロジックは他の IC とインタフェースする使い道がほぼないので、LVDS を使うバンクは 2.5V 専用のバンクになるでしょう。

LVDS 類似の規格で RSDS や mini-LVDS (フラットパネル内でつなぐ)、PPDS、BLVDS というのがありますが、これらは HR バンクでのみ使用できる 2.5V の VCCIO です。LVDS 類似の I/O はどうやっても 2.5V バンクでしか使えません。

DDR3 と MIG

7シリーズの FPGA は MIG というソフトウェア DDR メモリコントローラが使えます。Spartan-6 のときは MCB というハードウェアマクロだったのでユーザロジックの消費も少なかったのですが、7シリーズではソフトウェアコアになりました。そのほうがバグ対策や、どのバンクにも配置できるなどのメリットがあったのでしょう。

ソフトコアといっても、ISERDES や OSERDES などのプリミティブは活用するのでデータやアドレスの配置には制約があります。MIG の使い方は後の記事でいずれじっくりと解説することにします。

I/O 電圧と様々な IO 規格

VCCIO の電圧と、よく使われる IO 規格について表1にまとめます。

LED やスイッチなどの汎用部品や一般の IC と接続するのであれば、LVCMOS を使います。表では省きましたが LVTTL でも構いません。

SSTL と HSTL

HSTL と SSTL は参照電圧 (1/2 VCC) と比較して高ければ H、低ければ L という規格で、VREF が必要になります。

これらは似ているのですが用途は若干異なります。SSTL は DDR2、DDR3 などのメモリに使うもので、Strub-Series-Terminated という名前のとおり芋づる式にたくさんのメモリがつながる DIMM を想定しています。

HSTL はメモリ以外の一般的な高速信号に使われます。いわば、インピーダンスコントロールされた高速なシングルエンド信号です。

TMDS_33 とは

HDMI 信号 (DVI 信号) を使う場合は TMDS_33 を選択しますが、TMDS は 3.3V で高速差動信号が使える珍しい規格です。とはいっても HDMI 以外で使うことはないでしょう。

信号の電圧が VCCIO をオーバーしないように注意

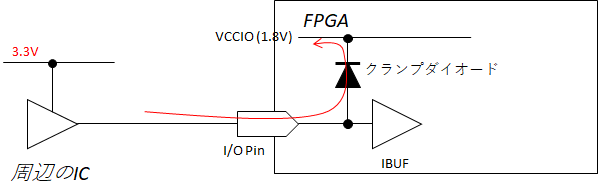

FPGA の I/O にはクランプダイオードが入っているので、VCCO+0.55V を超えた電圧を加えてはいけません。最悪の場合、デバイスが壊れます。例えば、1.8V バンクに 3.3V の IC からの信号をダイレクトに入れるのは NG です。

チェックリスト

回路を設計したら、以下のチェックリストでもう一度見直してください。

- Bank0 は 1.8V か 3.3V か 2.5V になっているか?

- Bank0 が 1.8V なら、コンフィグ ROM は 1.8V 対応品を選んでいるか?1.8V と 3.3V に両対応したのは意外とないぞ。

- 1.5V 以下のコンフィグ ROM はないぞ。Bank0 を 1.5V 以下にする選択肢はない。

- JTAG 信号の振幅は Bank0 の VCCIO になる。デイジーチェーンする IC と電圧は合っているか?

- Bank0 が 1.8V なら、CFGBVS を GND につないだか?

- LVDS で出力するバンクの VCCIO は、1.8V (HPバンク) か、2.5V (HRバンク) になっているか?

- LVDS の入力だけしかしない場合でも、VCCIO を 1.8V (HPバンク) か、2.5V (HRバンク) にしないと、DIFF_TERM が使えないことを理解しているか?

- LVDS が使えないことに後から気が付いて、DIFF HSTL とか DIFF SSTL を使おうとしても後の祭りだ。

- LVDS の入力だけしかしない場合でも、VCCIO を 1.8V (HPバンク) か、2.5V (HRバンク) にしないと、DIFF_TERM が使えないことを理解しているか?

- Bank14 の VCCIO は Bank0 の VCCIO と同じ電圧にしたか?

- Bank14 からコンフィグ ROM の、MISO、MOSI、FCS を引き出したか?

- PUDC は 1kΩ でプルダウンしたか?絶対にフロートにしてはいけない。

- クロックに使われる可能性のあるピンは MRCC か SRCC につないだか?

- シングルエンドのクロックならは MRCC の P 側につないだか?

- Bank0 の配線は図9と比較して相違はないか?

- Bank0 の VREFP には 1.25V を入れるか、もしくは GND につないだか?

- DXP、DXN、VP_0、VN_0 などのアナログピンは GND につないだか?

- JTAG は引き出したか?引き出さない場合は対タンパ性のためにあえてそうしているか?

- VCCBATT は GND または VCCIO_0 につないだか?

- 1つのバンク内で電圧の競合はないか?

- 一般に、受信だけなら VCCIO は混在してもよい。

- 受信だけでも VERF が異なる I/O 規格 (SSTL_15 と SSTL_18) は混在できない。

- VCCIO を超える電圧が加わらないようになっているか?クランプダイオードを ON させてはいけない。

- 一般に、受信だけなら VCCIO は混在してもよい。

- ZYNQ のリセットは、SRST_B を H にする→ POR_B を H にするの順に解除されるか?

- 順序を守ることが難しければ SRST は H のままでもいいので、とにかくプルアップ抵抗に出す。

- MIG は30番台のバンクに配置したか?

- Kintex-7 の MIG で、32bit や 64bit など幅の広いデータバスを使う場合、連続するバンクに配置したか?

- DCI を使う場合、VRN をプルアップ、VRP をプルダウンにしたか?感覚的な名前と逆で正解。

- モードピンは 3.3V 電源や GND に直結ではなく、VCCIO_0 へのプルアップ・プルダウンにしたか?

- DONE は 330Ω、INIT と PROG_B は 4.7kΩ でプルアップしたか?

まとめ

I/O ピンでの扱いで一番怖いのは、I/O のバンク内での電圧規格の競合です。

基板が出来上がってから配置配線ができないことに気が付いても後の祭りです。特に LVDS には注意してください。あとから LVDS が配置できないことに気が付いて DIFF_SSTL_15 が使えいないか・・とかやってもリカバリーは困難でしょう。

ぜひ一度、何もしないパススルーな回路でもいいから回路を書いて、制約ファイル (XDC) を書いて、すべての信号が競合なく設計したとおりのバンクに配置できるかどうか論理合成して試してみてください。

次回は XDC の書き方を解説します。お楽しみに!