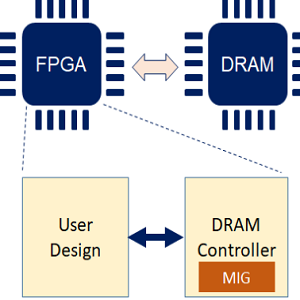

この記事では、Vivado で MIG の生成方法と DRAM コントローラ全体の Verilog HDL の実装を解説していきます。これまでのように、説明では、Digilent 社の Arty A7-35T FPGA ボードを想定します。

ソースコード: https://github.com/thiemchu/dram-arty-a7

現時点 (2020年8月) において、ACRi ルーム (ACRi の提供する FPGA 利用環境) で使用可能な Vivado 2019.2 を使いますが、新しい Vivado バージョンにも簡単に移植することができます。

MIG の生成方法

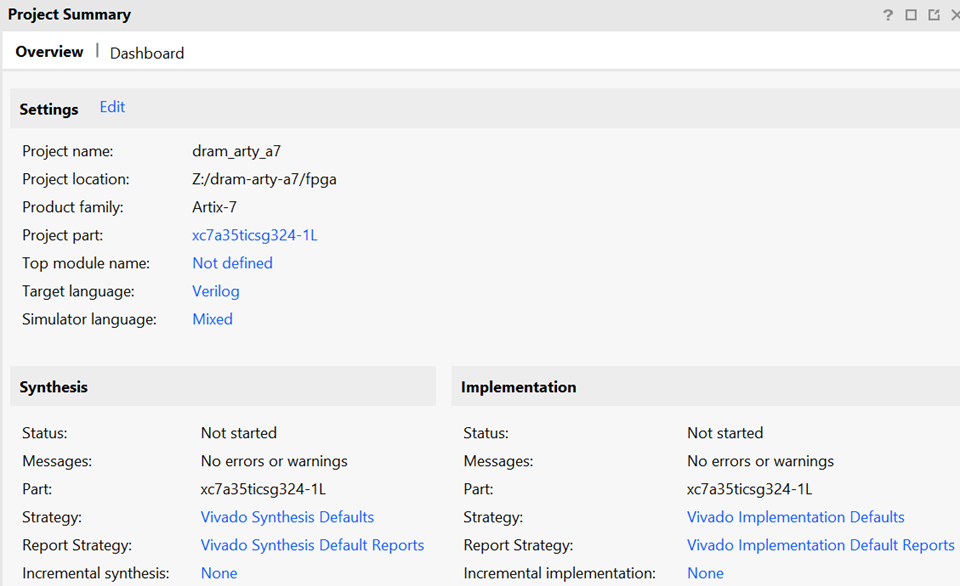

まず、ターゲット FPGA デバイス = XC7A35TICSG324-1L (Arty A7-35T FPGA ボードにのっている FPGA) の Vivado プロジェクトを作成します。プロジェクトの概要は下図に示します。

Vivado は様々な論理合成 (Synthesis) と実装 (Implementation) の戦略を提供します。ここでは、実行時間と回路の性能・エリア・消費電力等のバランスをとるデフォルトの戦略を採用することにします。

次に、作成したプロジェクト用の MIG を生成します。このために Arty A7 の参照マニュアルが役に立ちます。

https://reference.digilentinc.com/reference/programmable-logic/arty-a7/reference-manual

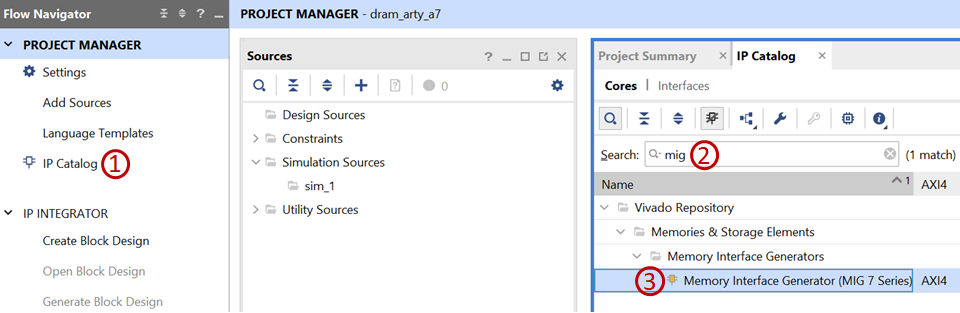

下図は MIG を生成するための IP コアの起動方法を示しています。

- ステップ①: 「IP Catalog」をクリックします。

- ステップ②: 「IP Catalog」タブの「Search」項目でを「mig」を入力して検索します。

- ステップ③: 表示された IP コア「Memory Interface Generator (MIG 7 Series)」をダブルクリックします。

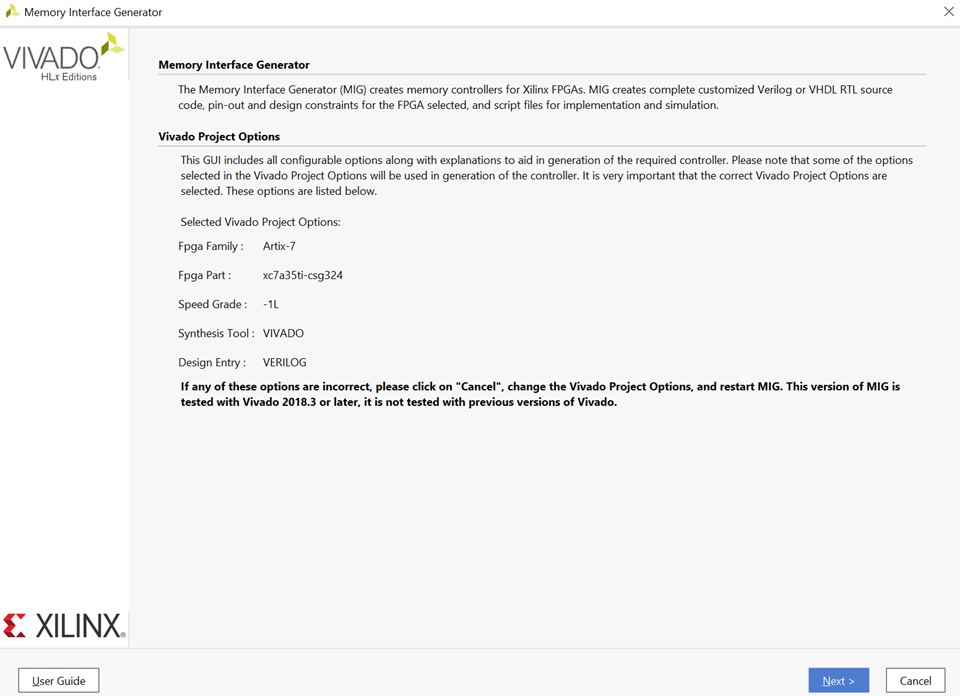

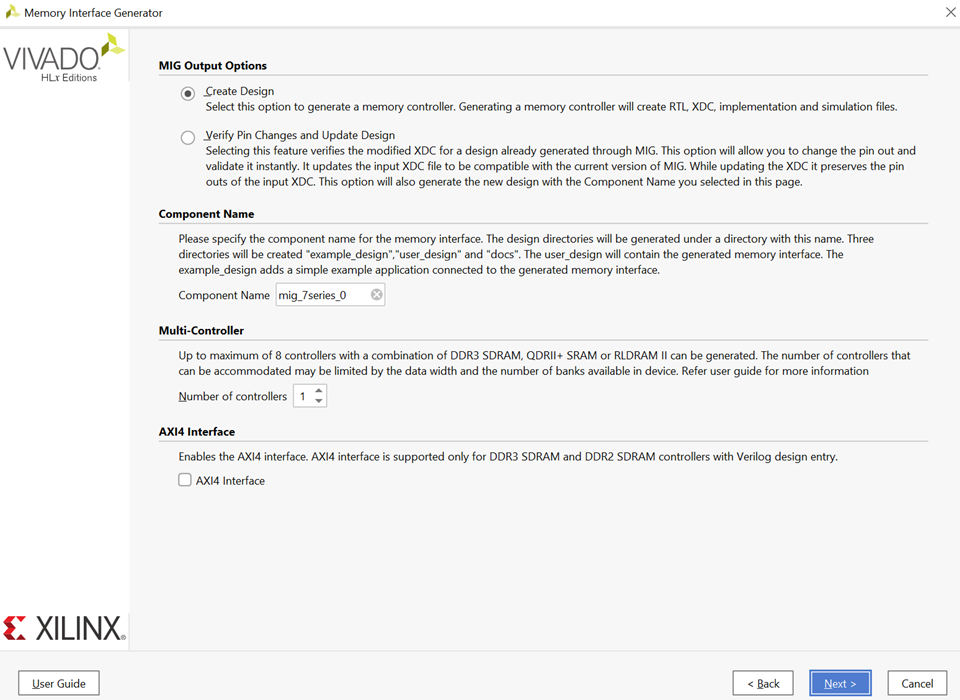

起動された IP コアの最初の構成画面は下図に示されます。

ここでは、「Next」をクリックして、次の構成画面に移動します。

生成される MIG の名前を「mig_7series_0」(デフォルトの名前) とします。ここでも、「Next」をクリックして、次の構成画面に移動します。

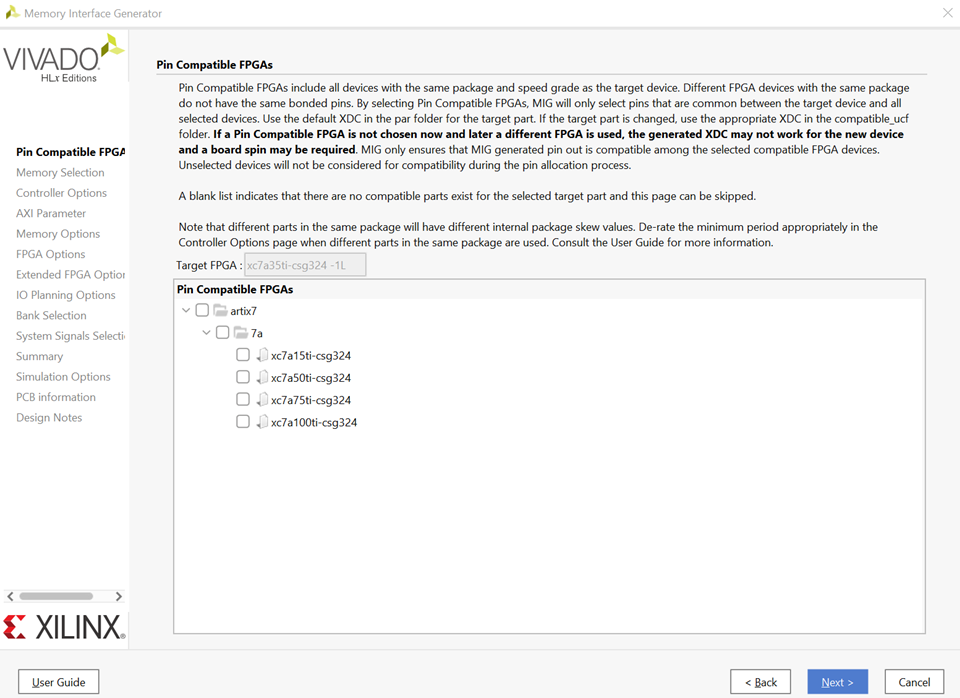

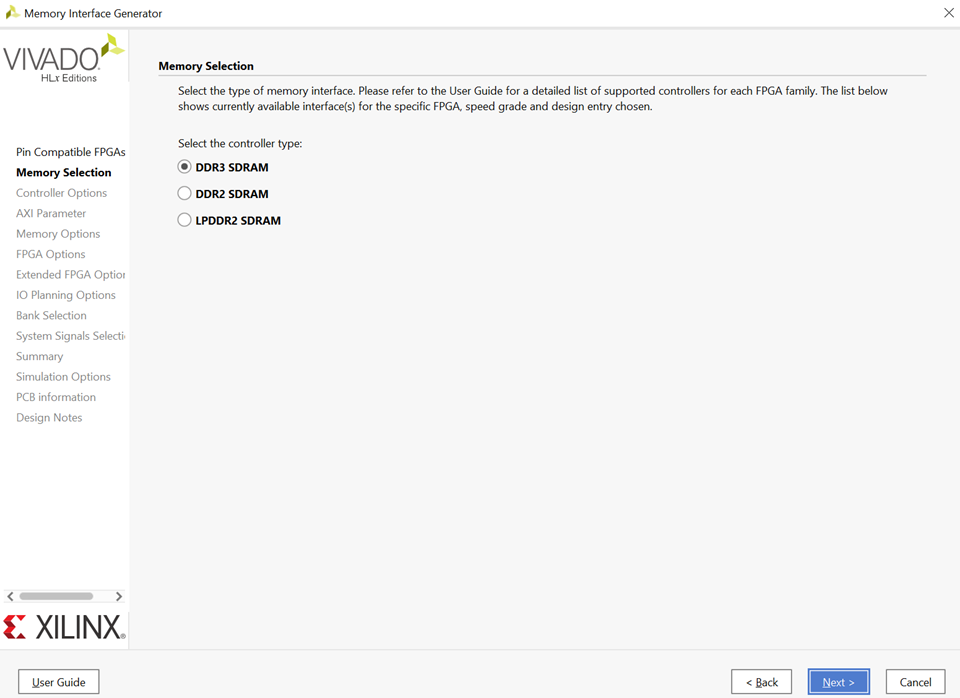

「Next」をクリックして、次の構成画面に移動します。

「Next」をクリックして、次の構成画面に移動します。

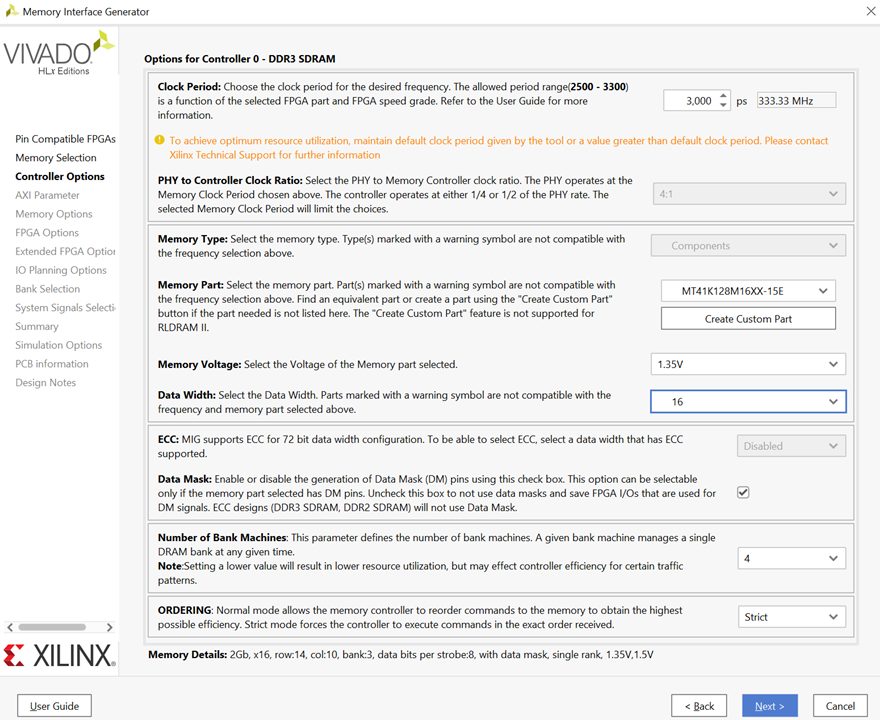

ここでは、図のように適切にパラメータを設定する必要があります。

- Clock Period: 3000 ps (333.33 MHz) => このパラメータは DRAM チップの動作周波数を決定します。

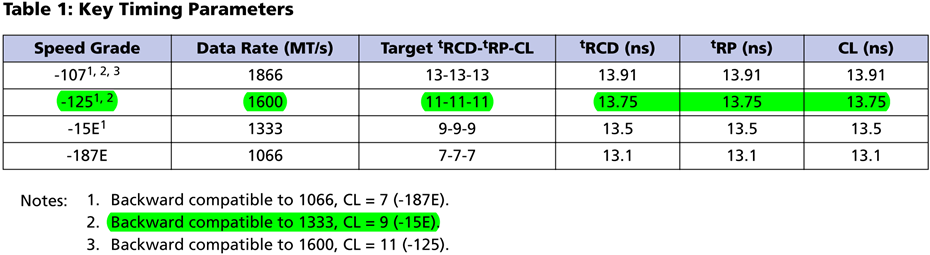

- Memory Part: MT41K128M16XX-15E => Arty A7-35T FPGA ボードに搭載する DRAM チップは MT41K128M16JT-125 ですが、MIG はこのチップをサポートしていません。その代わりに、MT41K128M16JT-125 と互換性のある MT41K128M16XX-15E を使うことができます。以下は MT41K128M16JT-125 のデータシートから抽出した表です。

- MT41K128M16XX-15E は MT41K128M16JT-125 よりデータレート (1,333 vs 1,600) が低いです。しかし、これは FPGA デバイス XC7A35TICSG324-1L がサポートできるデータレートより高いので、全体的に性能への影響がありません。

- Memory Voltage: 1.35V

- Data Width: 16 (MT41K128M16JT-125 DRAM チップのデータバスのビット幅は 16-bit です)

- Data Mask: Enabled

- Number of Bank Machines: 4 (デフォルトの推奨値)

- ORDERING: Strict

上記のパラメータを設定した後に、「Next」をクリックして、次の構成画面に移動します。

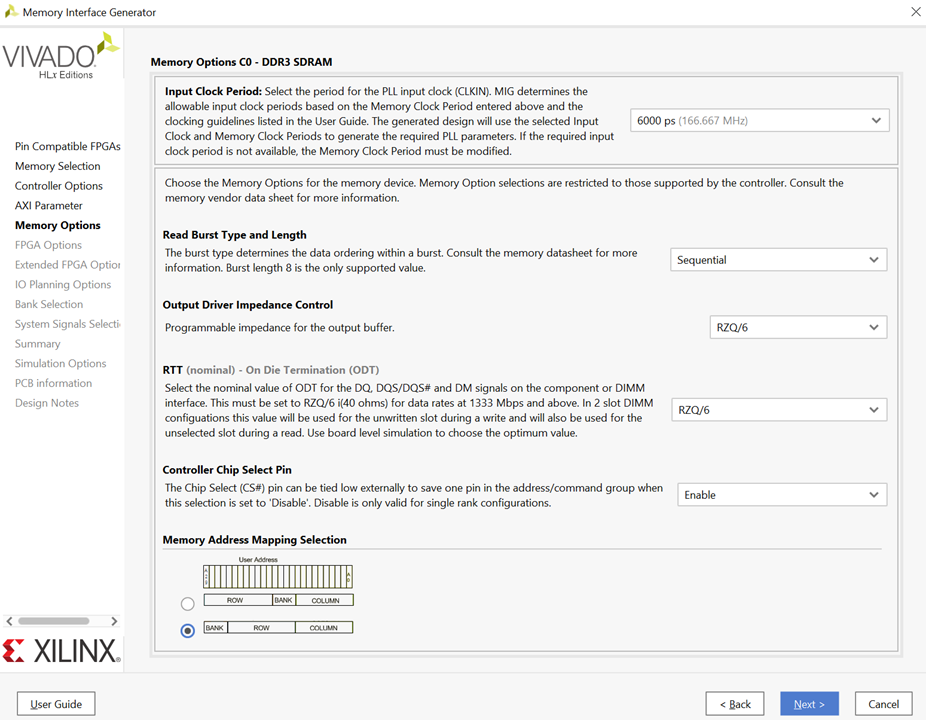

ここでは、図のように適切に次のパラメータを設定する必要があります。

- Input Clock Period: 6000 ps (166.67 MHz) => このパラメータは MIG の入力クロックの動作周波数を決定します。この場合、MIG に 166.67 MHz のクロックを提供する必要があります。

- Read Burst Type and Length: Sequential

- Output Driver Impedance Control: RZQ/6

- RTT: RZQ/6

- Control Chip Select Pin: Enabled

- Memory Address Mapping Selection: {Bank, Row, Column}

上記のパラメータを設定した後に、「Next」をクリックして、次の構成画面に移動します。

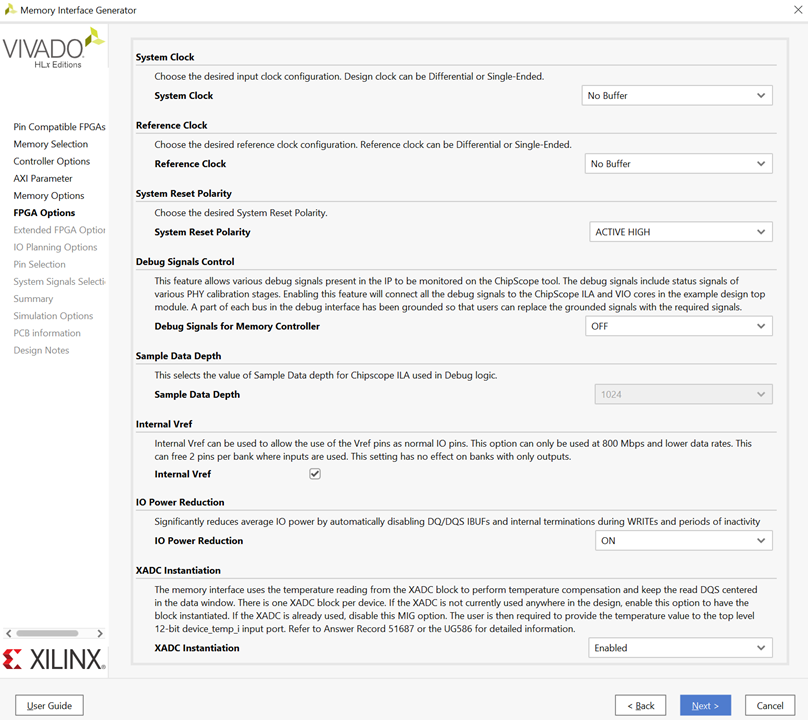

ここでは、図のように以下の設定を行います。

- System Clock: No Buffer => MIG の入力クロックは FPGA 内に生成されることを指定します。

- Reference Clock: No Buffer => MIG は上記の入力クロック以外に、200 MHz の参照クロックを求めます。この場合は、参照クロックも入力クロックのように FPGA 内に生成されることを指定します。

- System Reset Polarity: ACTIVE HIGH

- Debug Signals for Memory Controller: OFF

- Internal Vref: Enabled

- IO Power Reduction: ON

- XADC Instantiation: Enabled

次に、「Next」をクリックして、次の構成画面に移動します。

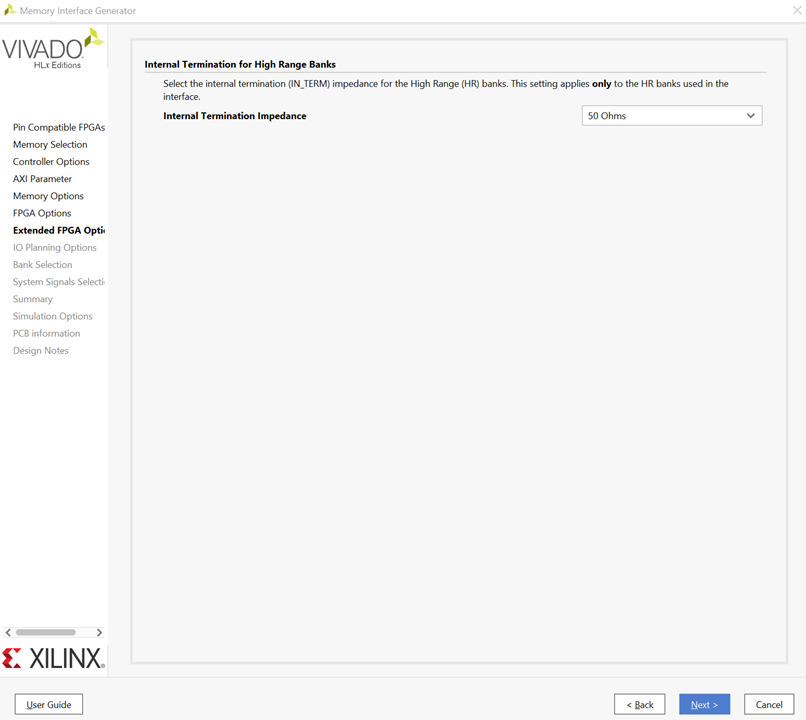

ここでは、「Internal Termination Impedance」を 50 Ohms に設定して、「Next」をクリックします。

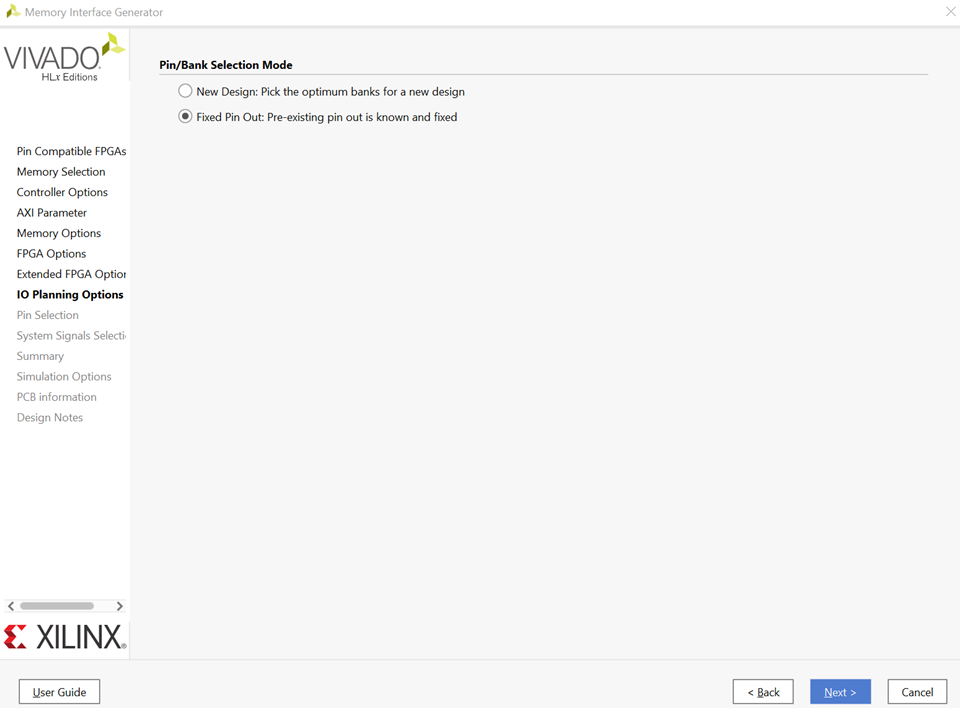

ここでは、「Fixed Pin Out: Pre-existing pin out is known and fixed」を選択して、「Next」をクリックします。

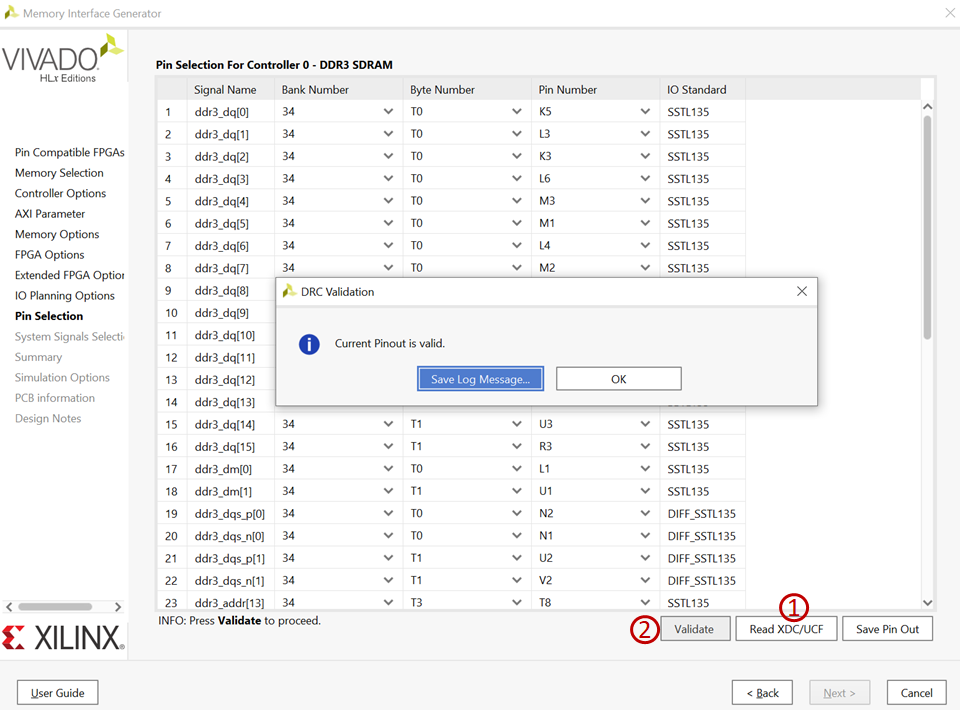

ここでは、DRAM チップに接続するための FPGA ピンの設定を行います。Digilent 社 (Arty A7-35T ボードのメーカ) は設定するための UCF ファイル (User Constraint File – Xilinx 社の独自の制約ファイル) を提供しています。

https://github.com/Digilent/Arty/blob/master/Resources/Arty_MIG_DDR3/Arty_C_mig.ucf

図のように、まず、①「Read XDC/UCF」ボタンをクリックして、上記の UCF ファイルの内容を読み込み、ピンの設定を行います。次に、②「Validate」をクリックして、設定した内容を検証します。問題なければ、次の設定画面に進むことができます。

残りの画面は特に設定することがないので説明を省略します。

DRAM コントローラ全体の Verilog HDL の実装

DRAM コントローラ全体の Verilog HDL の実装は、基本的に、前回と前々回で説明した内容に従います。次の github リポジトリからコードをダウンロードすることができます。

https://github.com/thiemchu/dram-arty-a7

このリポジトリは2つのディレクトリがあります。

fpga: Vivado プロジェクトファイル (*.xpr ファイル) を含みます。

rtl: Verilog HDL のソースファイル、MIG, Clocking Wizard IP コアを含みます。DRAM コントローラは rtl/dram ディレクトリにあります。

- dram.v: DRAM コントローラと異なるクロックドメイン間のデータ転送のため非同期 FIFO のラッパ。アプリケーション回路 (User Design) は直接にこのラッパにやり取りします。dram.v で使われた非同期・同期 FIFO の Verilog HDL ソースコードは rtl/common ディレクトリにあります。

- dram_controller.v: DRAM コントローラ。MIG とユーザインタフェース (User Interface) というアプリケーション回路と MIG の間のやり取りを抽象化するためのモジュールから構成されます。

- mig_ui.v: ユーザインタフェース

- mig_7series_0: 上記の説明のように生成された MIG

- clk_wiz_0: MIG は、自分自身の制御のために、外に1つのクロック信号を出力しています。このクロック信号の動作周波数は図7の構成画面で設定した DRAM チップの動作周波数の1/4倍です。ここでは、DRAM チップの動作周波数は 333.33 MHz なので、MIG によって出力されるクロック信号の動作周波数は 333.33/4 = 83.33 MHz。clk_wiz_0 はこの 83.33 MHz クロック信号から、アプリケーション回路のためのクロック信号を生成します。

まとめ

今回は、Vivado での MIG の生成方法と DRAM コントローラ全体の Verilog HDL の実装を説明しました。

次回は、実装した DRAM コントローラの検証とその応用を解説していきます。

東工大 Thiem Van Chu