20Q3.06B

20Q3.06BFPGA と予測不可能性と乱数 (4)

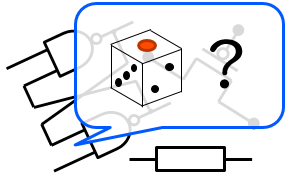

FPGA 向けの真性乱数生成器 (TRNG) の設計法に関するコースの第4回です.今回は、SR ラッチを禁止状態から保持状態へと移行させた時の挙動 (メタスタビリティ) を用いた TRNG の構成と、その改良について紹介します。 なお、この記事の最後に紹介するラッチ-ラッチ構造 (Latch-latch composition) に関する論文 は、電子情報通信学会の Electronics Express (ELEX) 論文誌に掲載されています。オープンアクセスの電子ジャーナルなので、...