20Q4.04A

20Q4.04ABRAM 達人への道 (3) FIFO に使ってみる-非同期型1

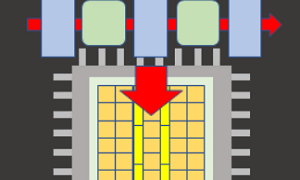

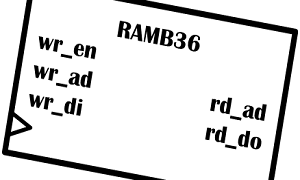

はじめに BRAM アプリケーションとして FIFO を扱っていますが、第2回では同期型 (書き込み側のクロックと読み出し側のクロックが同一の場合) を扱いました。今回は非同期型 (書き込み側のクロックと読み出し側のクロックが独立な場合) を扱います。 どうしたら非同期型の FIFO ができるか まず、前回の基本構成を図3-1に示します。 図3-1 同期型 FIFO のブロック図 書き込みアドレスカウンタ、読み出しアドレスカウンタは独立したクロックで動作し、互いに...