数年前、ある学会で「FPGA の基板を設計して実験装置を作ったけど、コンフィグがうまくいかなくて半年動いていない」というような話を聞きました。壮大な実験の中のメインとなる装置を作っているという研究報告的な発表だったのですが、よくそんな無駄な時間を過ごしているなと驚愕したものです。しかも周りで聞いている人たちも何も答えられない・・

今回は失敗しないためのコンフィギュレーション回路について説明します。なお、語呂や語感のためにコンフィグといったりコンフィギュレーションといったり表記が揺れますが、意味は同じです。

FPGA のコンフィギュレーション

コンフィギュレーションとは

電源が投入された直後では FPGA は起動していません。Xilinx FPGA は RAM ベースであるため、電源が切れると記憶している回路が消えてしまうからです。

まっさらな FPGA にユーザ回路を書きこんで、望みの動作ができるようにすることをコンフィギュレーションといいます。

コンフィギュレーションを行うデータ列をビットストリームといいます。Xilinx の FPGA ではビットストリームを与えるために大きく分けて7種類の方法が用意されています。

- マスターシリアル・コンフィギュレーション・モード

- スレーブシリアル・コンフィギュレーション・モード

- マスター SelectMAP (パラレル)・コンフィギュレーション・モード

- スレーブ SelectMAP (パラレル)・コンフィギュレーション・モード

- JTAG/バウンダリスキャンモード・コンフィギュレーション・モード

- マスター SPI フラッシュ・コンフィギュレーション・モード

- マスター BPI フラッシュ・コンフィギュレーション・モード

たくさんの方法があるのですが、実際に使われるのはマスター SPI フラッシュ・モードと、開発時に使う JTAG モードくらいです。それ以外の方法は旧世代からの互換性のためにあったり、FPGA にソフトコアの CPU を内蔵してシステム開発をしていた名残のようなものなので、あまり使いません。

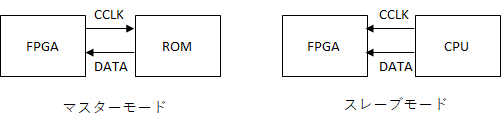

マスターとスレーブ

マスターというのは FPGA が CCLK (コンフィギュレーション・クロック) を出力して能動的に行うモードです。

スレーブというのは外部の CPU などから FPGA に CCLK とともにコンフィギュレーションデータを与えて受動的に行うモードです。

筆者は過去に一度だけスレーブコンフィギュレーションモードで動くユーザ機器をデバッグしたこと (ある計測装置が動かないから動くようにしてほしいという案件依頼) がありますが、外部の CPU にプログラムとともにコンフィギュレーションデータを格納しておいて、CPU のパラレル I/O から FPGA のコンフィギュレーションデータを書き込むというものでした。今では ZYNQ でできてしまうので、こういう回路設計はもうすることはないでしょう。

コンフィギュレーションモードの解説

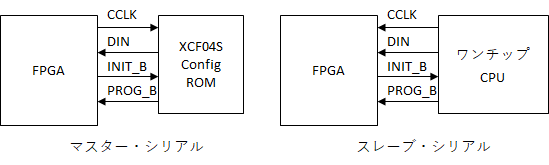

シリアル・コンフィギュレーション・モード

シリアルコンフィギュレーションモードとは、1bit のデータ入力端子を通じてビットストリームを流し込むモードです。

CCLK を FPGA が出すのがマスターシリアル、CCLK を FPGA が受け取るのがスレーブシリアルです。

マスタシリアルモードは、旧世代の XCF04S や XCF32P といった Xilinx 専用コンフィグROM でよく使われていたモードです。2020年現在ではコンフィグ ROM を使う必要はないと思いますので出番はあまり多くありません。

スレーブシリアルはワンチップマイコンなどを使ってコンフィグデータを送り込むのに便利なモードですが、あまり使う機会はないでしょう。

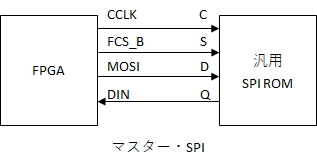

マスター SPI モード

マスターシリアルの弱点は Xilinx の専用コンフィグ ROM が高価であったことです。Spartan-3E から汎用の SPI ROM をコンフィグ ROM として使うためのマスター SPI モードが追加されました。

当時の ROM は4Mビットで1000円くらいしたと記憶している。噂に聞いた程度ではあるが絶対に書けないような事情もある。

マスター SPI モードは、FPGA がマスターとなって SPI ROM からビットストリームを読み出します。マスターシリアルとの違いは ROM の読み出しコマンドを操作することです。このため、DIN と CCLK だけでなく FCS_B と MOSI も使用します。

このマスター SPI モードが現在の主流です。

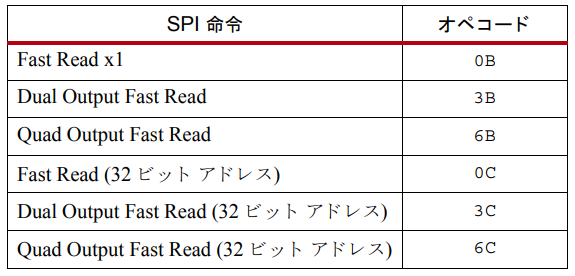

なお、SPI ROM は以下の表にある命令をサポートしている必要があります。

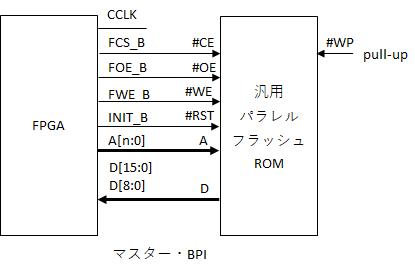

マスター BPI モード

マスター BPI モードは、FPGA マスターとなって BPI ROM (パラレルROM) からビットストリームを読み出すモードです。SelectMAP とは違い、ROM の読み出しのためのアドレス線やコントロール線の操作を行います。

8bitまたは16bitのデータ幅でコンフィグするので、SPI モードよりも高速です。

FPGA にソフトコアの CPU を入れた場合のプログラム ROM を共通化して部品点数を減らしたり、コンフィギュレーションを高速に行いたい場合に使います。

高速化が必要な場合とは、例えば PCI Express を使うデザインでは少なくとも電源投入後500ms 以内に PCI Express が動作開始できなければなりません。SPI ROM から x1 で起動すると小規模な FPGA であっても間に合わず、PC の BIOS が起動の最初では PCI Express が見えなかったのに OS が起動するときに出現することになり、不安定な動作になります。

多くの PC ではもう少し時間の余裕をみて起動してくれますが、相性が悪い FPGA ボードとして片づけられかねません。PCI Express の規定時間内に確実にコンフィグを終了させ BIOS に認識されるためには BPI ROM モードを使ってみてください。

SelectMAP (マスター/スレーブ)

SelectMAP は BPI と似ていますが、ROM を操作する制御信号はありません。ビットストリームデータのみを外部から入力します。

どういう用途で使うかというと、外部においた CPU の周辺回路コントローラを FPGA で作りたい場合に適しています。例えば、ネットワークに接続された機器において、CPU が最新ファームウェアをダウンロードしてきて、最新のデータで FPGA を動作させるといった機能を持たせることができます。

JTAG モード

JTAG モードは特別なモードというわけではなく、いつでも使うことができるコンフィギュレーションモードです。JTAG がつながってさえいればよいので、回路設計上は特別な配慮はいりません。

一般的に、SPI ROM に書き込むには2~3分かかりますが、JTAG を通じてコンフィギュレーションするには数秒しかかかりません。作った回路をすぐに書き込んで試すことができるのでデバッグ時には重宝します。ただし電源を OFF/ON すると消えてしまいます。

コンフィギュレーション用ピンの説明

コンフィ用にはいくつかのピンがあります。重要度の高いものから説明していきます。

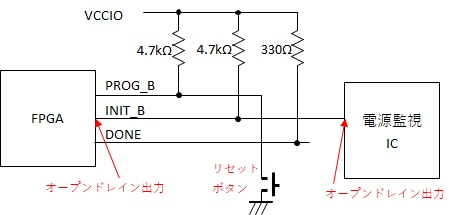

PROGRAM_B

このピンを L にすると、FPGA のすべてのコンフィギュレーションが消えます。いわば FPGA のマスターリセット的なピンです。4.7kΩ 以下の抵抗で VCC_0 にプルアップし、リセットをかけたい場合にLにします。

INIT_B

双方向の初期化ピンです。PROGRAM_B が L にされてコンフィギュレーションが開始した場合に L が出力されます。

この端子も 4.7kΩ 以下の抵抗で VCC0 にプルアップして使います。

最近知ったことなのですが、リセット IC などを使う場合には PROGRAM_B ではなく INIT_B につなぐべきだそうです。どうやら PROGRAM_B はエッジで動く機能も含まれているので、電源 ON 時にずっと L のままだと FPGA 内部が完全にリセットされないとのことがユーザガイドに書かれていました。下の図に正しいと思われる電源監視 IC の接続方法を示します。

DONE

コンフィギュレーションが完了したことを示すピンです。完了すると H になります。

このピンはオープンドレインの双方向ピンです。7シリーズ以前の FPGA では 330Ω のプルアップ抵抗で VCC0 につなぐことが求められていました。オープンドレインの双方向ピンであるがゆえ、立ち上がりのエッジがある程度鋭いことが求められていたため 330Ω という抵抗値だったのですが、7シリーズではデフォルトでレジスタが入るようになったためプルアップ抵抗は不要になりました。ただ、従来と同じように 330Ω を付けることも許されていますし、そうするべきだと思います。

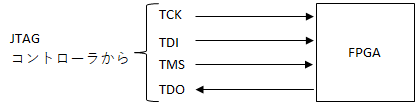

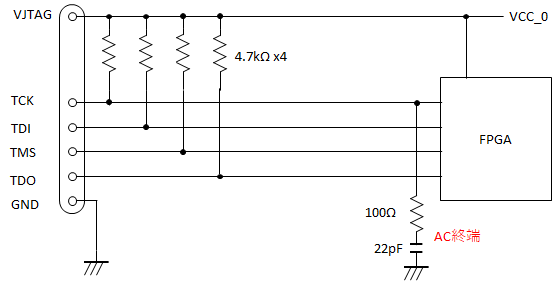

TCK, TDI, TMS, TDO

これら4つの端子は JTAG 端子で、開発時のコンフィグやデバッグに使います。コネクタに接続したままのオープンでも構わないのですが、ノイズでバタバタするとまずいので 4.7kΩ 程度のプルアップ抵抗をつけておきます。

TCK はノイズに弱いので、22pF~100pF くらいのコンデンサと 100Ω~220Ω くらいの抵抗を使って AC 終端しておきます。AC 終端によって劇的に信号波形が綺麗になり、JTAG でのトラブルは激減します。

JTAG の電源は VCC_0 であることに注意してください。間違っても VCC_0 が 1.8V のシステムに、3.3V の JTAG 信号を入れないようにしてください。

EMCCLK

この端子はユーザ I/O と兼用されていて気が付かない場合が多いでしょう。

マスターモードでのコンフィグクロックを、FPGA の内蔵オシレータではなく外部からクロックを与えたい場合に使います。通常は使わないでしょうから、ユーザ I/O のピンとして使います。

SPI モードで使うコンフィグピン

上で述べたように Xilinx FPGA にはたくさんのモードがありますが、最もよく使われるマスタ SPI モードです。本稿ではマスタ SPI モードおけるピンの使い方のみ説明します。

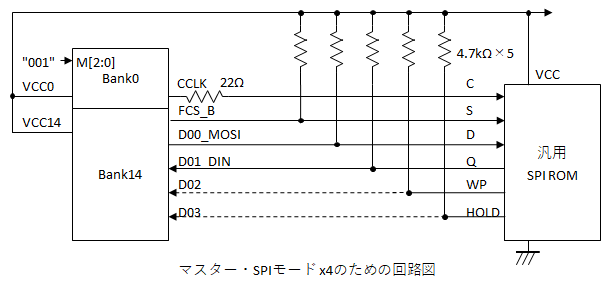

マスタ SPI モードでは、D01_DIN、D00_MOSI、D02、D03 の4つのデータピンと、FCS_B、CCLK があります。このうち CCLK は Bank0、それ以外は Bank14 の兼用ピンです。

4つのデータピン

Bank14 は通常のユーザ用 Bank でその電源電圧は VCCO14 で決まります。CCLK は Bank0 に属するので電源電圧は VCCO0 で決まります。それゆえ、VCCO0 と VCCO14 は等しい電圧でなければなりません。

D00_MOSI は SPI ROM のデータ入力に、D01_DIN は SPI ROM のデータ出力につなぎます。

D02 と D03 は、SPI ROM を x4 モードで接続する QSPI モードで使用する場合に使います。x2 モードや x1 モードで使う場合には D02 と D03 のピンはつなぐ必要はなく、FPGA はユーザ I/O として使えます。QSPI モードの場合 D02 は ROM の WP に、D03 は ROM の HOLD につなぎます。

x4 に対応させるにはコマンド 6C に対応した SPI ROM が必要なのですが、意外と対応していないものもあるのでオプション的に考えておいたほうがよいかもしれません。

CCLK

コンフィグ用のクロックは Bank0 にあります。CCLK は SPI ROM のクロック入力につなぎますが、可能なら 22Ω 程度のダンピング抵抗を入れるようにしてください。

チップセレクト

Bank14 のユーザ I/O との兼用ピンに FCS_B というピンがあり、このピンは ROM の CS につなぎます。

SPI ROM を使ったコンフィギュレーションは以上で述べたピンを接続するだけなので失敗のリスクは低くなります。オリジナル機器ではマスター SPI モードを選ぶのがおすすめです。

モードピンの設定

7種類のモードは M[2:0] ピンで設定します。これらの設定は VCC0 や GND に固定しても構いません。プルアップまたはプルダウン抵抗を使って設定するのであれば 1kΩ 以下にします。

| コンフィグモード | M[2:0] | バス幅 | CCLKの方向 | 備考 |

| マスターシリアル | 000 | x1 | 出力 | |

| マスターSPI | 001 | x1,x2,x4 | 出力 | 最もよく使われる |

| マスターBPI | 010 | x8,x16 | 出力 | FPGAにソフトコアのCPUを入れて、パラレルROMを使用するときに便利。 |

| マスターSelectMAP | 100 | x8,x16 | 出力 | |

| JTAG | 101 | x1 | デバッグ時に使う | |

| スレーブSelectMAP | 110 | x8,x16,x32 | 入力 | 外部CPUなどからコンフィグする。 |

| スレーブシリアル | 111 | x1 | 入力 | 旧世代のコンフィグROMで使う |

コンフィグ後のユーザリセットは必要か?

FPGA にユーザリセットが必要かというのは議論がわかれるところですが、筆者は FPGA にユーザリセットはいらないという主張です。

FPGA は汎用 TTL や ASIC と違い、電源 ON の後コンフィギュレーションというプロセスを経て起動します。その際にすべてのフリップフロップが0にクリアされることが保証されています。(もちろん開発時に明示的に指定することによりフリップフロップの初期値は変えられる)

ユーザ回路の起動時に不定になっているフリップフロップはありません。時間差的にリセットを遅らせたい部分がある場合は、FPGA 内部でタイマカウンタを持てばよいのです。

コンフィグのまとめ

Xilinx FPGA にはここでは紹介しきれていないほど様々なコンフィギュレーションのバリエーションが存在しています。

その多くは CPU を組み込んだシステムでの部品の共通化や、複数の FPGA を1個の ROM からコンフィグするなどといったコスト削減のためのものです。

少数の特別に設計された実験用計測機器を作りたいという読者を想定していますので、微々たるコストは考えずに、確実に動く SPI ROM モードを使用するのが賢明です。

ZYNQ のコンフィギュレーション

上でみてきたように、普通の FPGA は電源 ON と同時にコンフィグして回路が書き込まれ、ユーザ回路が動作を開始します。

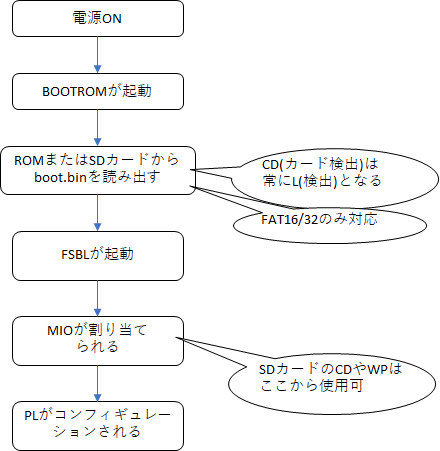

ZYNQ はそうではなく、リセット後に「BOOTROM」と言われる内蔵プログラムが動き出して SPI ROM または SD カードを読みだして FSBL を起動し、FSBL の中からコンフィグ用のビットストリームを特別な I/O ポート (DEVCFG) に送り込むことで FPGA 部分 (PL) をコンフィグするようになっています。

BOOTROM と FSBL で MIO の割り当てが変わるため、注意が必要となります。

ZYNQ のコンフィグ関連ピン

ZYNQ にも PROGRAM_B、INIT_B、DONE といったコンフィグ関連ピンがあります。これらは通常の FPGA と同様に 4.7kΩ の抵抗でプルアップし、DONE は 330Ω でプルアップします。

PROGRAM_B や INIT_B を L にすると FPGA のコンフィグデータは消えますが PS は動き続けます。ZYNQ ではこれらのピンは使いみちはないのですが、プルアップしておきます。

より重要なコンフィグ関連ピンは MIO にあります。

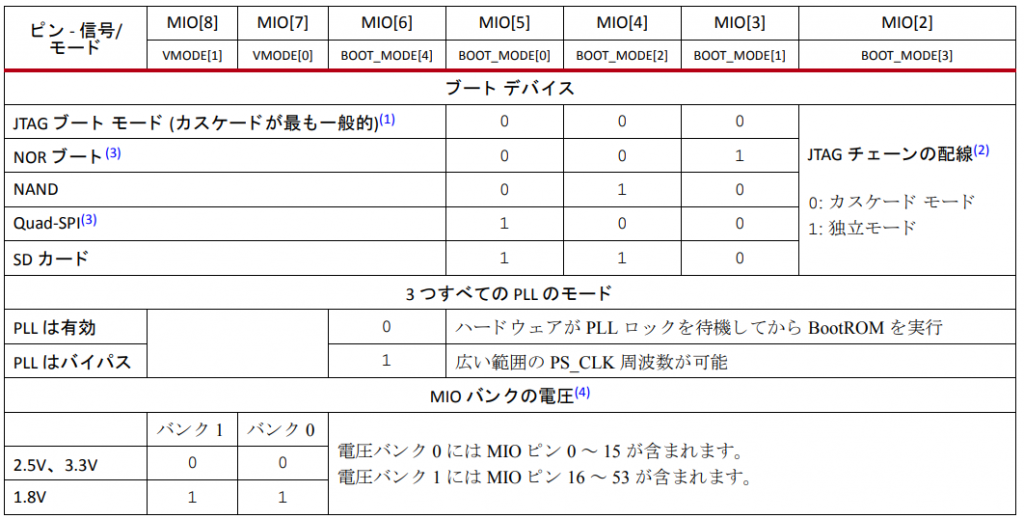

MIO の設定

ZYNQ のコンフィギュレーションモードは MIO[2:8] で設定します。詳しいことは Xilinx のユーザガイド UG585 に書かれています。

ZYNQ のブートモードというのはすなわち、PS のプログラムをどこから起動するかということです。通常は SD カードモードか、Quad-SPI モードを選びます。それに合わせて MIO[5:3] を設定してください。

MIO2 は動作上どちらでもよいのですが、わからなければ L のカスケードモードにしてください。MIO6 も L にします。

MIO[7:8] は MIO バンクの電源電圧を設定します。両方とも 1.8V ならば “11” にします。

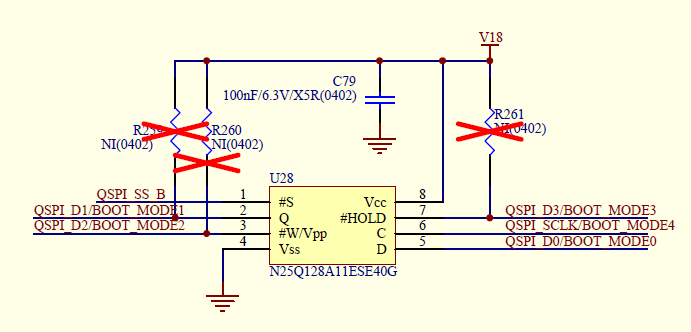

MIO の設定と SPI のプルアップのどちらを優先すべきか

ZYNQ の QuadSPI ROM を使う際には、D1、D2、D3 をプルアップしないようにしてください。QSPI の D2 と D3 は #WP と #HOLD なのでプルアップしたくなりますが MIO の設定と被ってしまっています。ここは MIO を優先します。

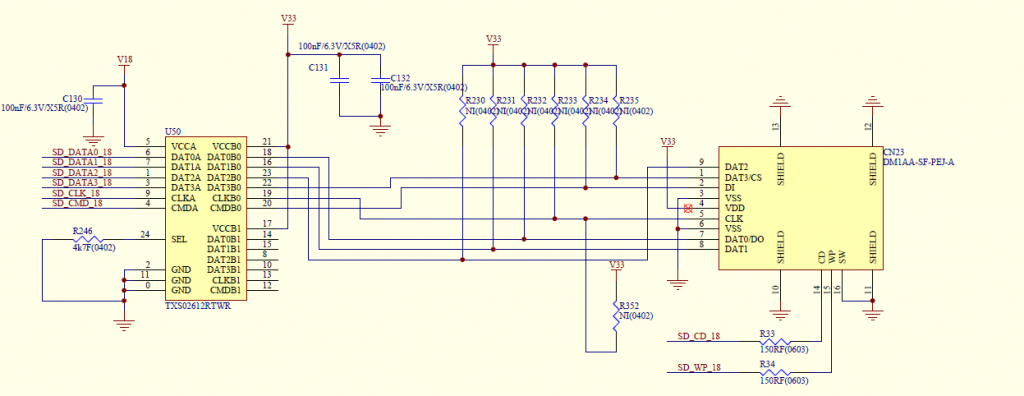

下の図はプルアップしたけどうまく起動しなかったため後から削除された回路図です。

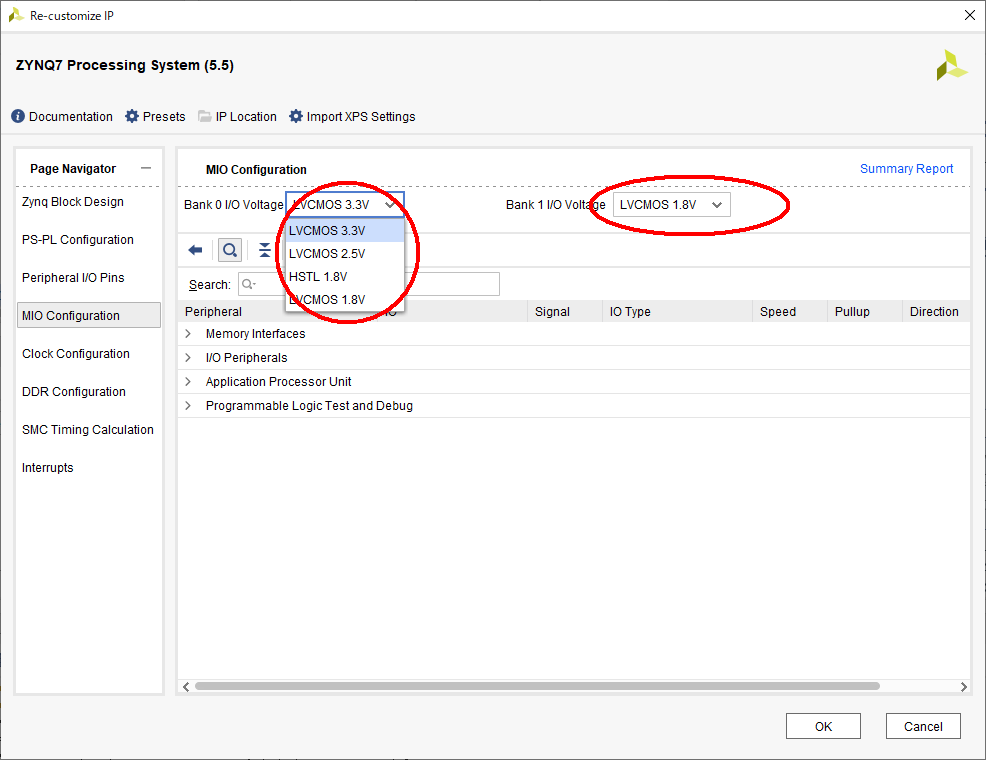

MIO の電圧設定を忘れずに

ZYNQ の2つある MIO バンクの電源電圧は個別に設定できますが、この MIO ピンで設定するだけではなく、Vivado の中から ZYNQ の MIO の設定をする際にソフト的に設定する必要もあることを忘れないでください。この設定が効いてくるのは FSBL 以降です。

SD カードブートの注意点

SD カードからブートする最の注意点がいくつかあります。

- XC7Z010 の CLG225 ピンデバイスでは、SD カードブートをサポートしていません。

- 使用できる最大の SD カードのサイズは 32GB です。FAT16/FAT32 でフォーマットされる必要があります。64GB 以上の SD カードは exFAT になるので使用できません。

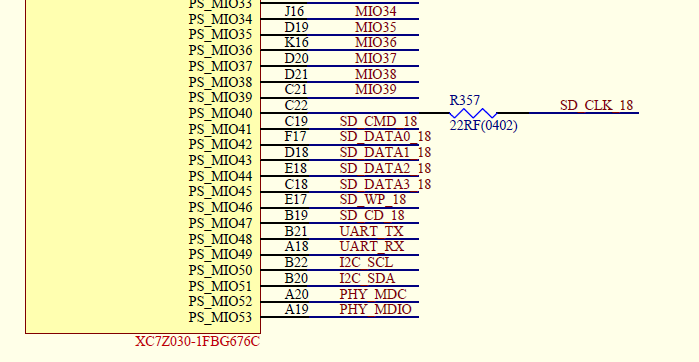

- ZYNQ の SD0 のポートは MIO40..45 以外に MIO16 や MIO28 を使用することもできますが、ブート可能な SD0 のポートは MIO40..45 のみです。

- SD カードの端子には CD (カード検出) と WP (ライトプロテクト) という端子がありますが、製品版 ZYNQ ではブート時に CD を検出せず「常にカードあり」として動作します。

- CD と WP は SD カードソケットでスイッチになっていますが、1kΩ でプルアップしても認識されません。プルアップは 100Ω 程度で行うようにしてください。

- MIO40 は通常は 1.8V に設定されていますが、通常の SD カードは 3.3V 仕様です。このため、双方向のレベル変換 IC が必要です。

- CCLK には 22Ω 程度のダンピング抵抗を必ず入れること。CCLK はドライブが強く、波形が反射しやすいためです。

SD カードの電圧レベル変換は TXS02612 などを使うといいでしょう。

カード検出信号についての補足

ZYNQ の SD カードの検出は CD という端子をLにするとカードあり、H ならばカードなしとして認識します。

また、ZYNQ は最初に BOOTROM という内蔵 ROM が起動し、BOOTROM から SD カードを読み出し、FSBL を起動しています。

ES 品の ZYNQ (2015年ごろ) では BOOTOM は MIO0 を CD として使用していましたが、BOOTROM から FSBL に制御を移したあとは、ユーザが設定した端子を CD として使用していました。そのため、BOOTROM と FSBL 以降で CD 端子が異なるという事態が起きていました。現在の製品版 ZYNQ では BOOTROM では CD 端子を見ません。

SD カード用クロックのダンピング抵抗の必要性

SD カードのクロックは ZYNQ から直接つなぐのではなく、ダンピング抵抗をはさんでください。

ダンピング抵抗をいれずに直接 SD カードまでつないだ場合、SD_CLK の配線長が 135mm の場合の SD カード端で反射して大きく乱れます。

誤動作はしませんでしたが、リンギングが多く、いつ誤動作してもおかしくありません。

次の図は 22Ω のダンピング抵抗をいれた場合の波形です。

反射もおさまり、これならば誤動作の心配はありません。

QSPI ブートの注意点

ZYNQ を QSPI でブートする場合は、サポートされている QSPI ROM かどうかを確認してください。QSPI ROM はベンダによって少しずつプロトコルが違います。Micron や Numonyx、SST などの SPI ROM は使えないようです。

JTAG ブートとは

ZYNQ のコンフィグはいつでも JTAG からできると思われるかもしれませんが、そうではありません。例えば、BOOTROM が SD カードを読んで失敗した場合などでは JTAG も受け付けない状態でループしてしまいます。

JTAG ブートというのは、そういう「JTAG コンフィグ不可能」な状態にならないように PS を安全に止めているモードです。JTAG から起動したいのであれば、SD カードを抜いたり、QSPI ROM を消去したりして起動しない状態にするのではなく、JTAG モードを使います。

最後のまとめ

計測や制御の目的で1台や2台の FPGA ボードを作ることを前提として、FPGA を回路設計の面から使い方を解説してきました。

この5回の連載記事が皆様の実験や研究においてオリジナルな回路を設計する際の参考になり、「作った回路の FPGA が動かない」というトラブルが少しでも減れば幸いです。