みなさん、はじめまして。

筆者は大学の研究室(主に物理系)や独立行政法人〇〇研究機構といった顧客に「計測用カスタム FPGA 基板」を作るという仕事をしています。大学以外にも一般の企業向けに産業用カメラを作ったり、計測器を作ったり、あるときは自社製品として FPGA 評価ボードを作ったりと、とりとめもなくいろいろなことをやっています。

実際には基板を作るだけではなく、ADC や DAC まわりのアナログ設計や、FPGA の回路設計、カスタムファームウェアから PC 側のソフトウェアの開発まで要望に応じて幅広くサポートしています。大学の研究室で新しい仕組みの「センサ」が開発されて、そのセンサを使うために FPGA を利用したデータ計測収集装置(DAQ:Data Aquisition)を作るというのが多いですね。

計測に FPGA を使うとは?

計測に FPGA を使うのはどのようなときでしょうか。

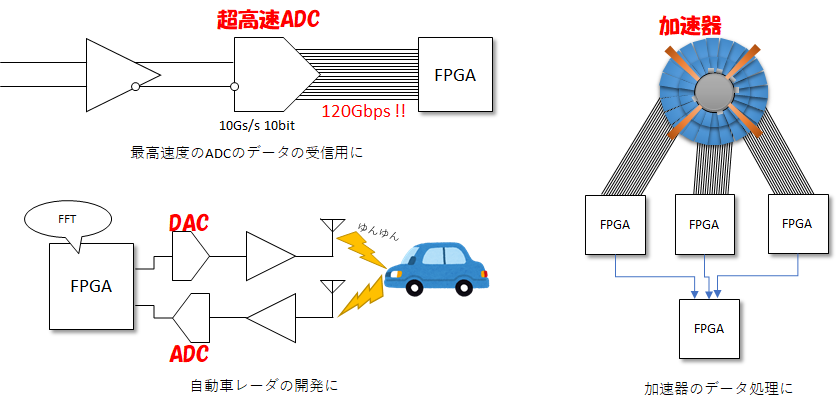

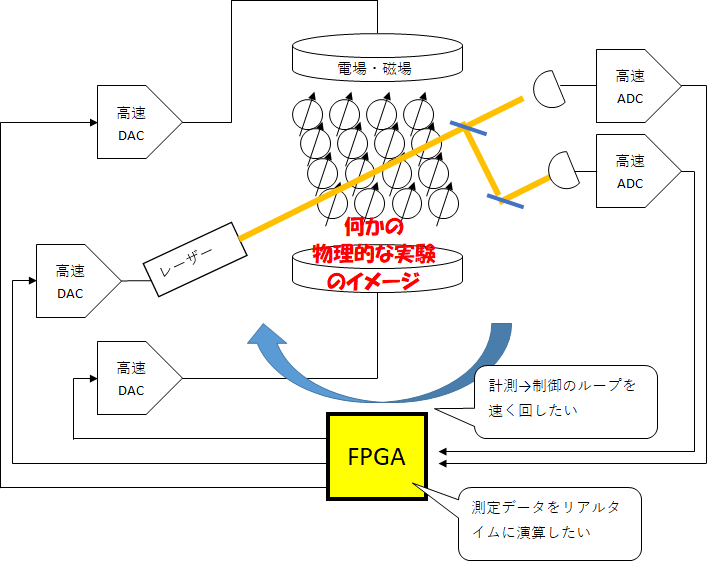

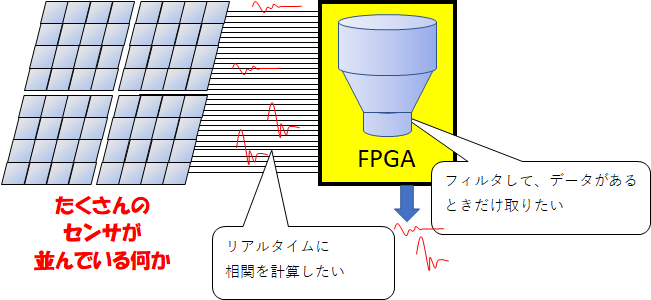

例えば高速な ADC を扱う測定や、膨大なデータを扱う測定、計測した結果を低遅延でフィードバックしたり、レーダの開発のように DAC から信号を出して計測対象から戻ってくる波形を ADC でキャプチャして信号処理するなどという分野が挙げられます。

超高速 ADC のインタフェースのために ASIC を作るとコストが合わないし、加速器や車レーダの開発のようにアルゴリズムを試行錯誤する場合は書き換えられる必要があるので、FPGA がぴったりです。

FPGA を使えば、パソコンで処理するよりもはるかに速くフィードバックしたり、膨大なデータをフィルタしながらデータ量を削減したり特徴量だけを抽出して計測できるのではないかという「夢」があります。

まぁ、上の絵に描いたようなことが実際に動けば理想的なのですが、大学の研究室で FPGA を使った装置を開発しようとすると一筋縄ではいかないことが多くあります。その理由は、

- ハイレベルな計測をするには評価ボードではだめで、自分で基板を作らなければならない

- FPGA が複雑になりすぎていて、回路や基板を設計できる人がいない

- 計測したデータを FPGA で処理する方法がわからない

- 計測したデータをパソコンに取り込む方法がわからない

- それらがわかったころに卒業してしまう

こういった課題があるため、なかなか思い通りに進んでいない研究もあるかと思います。

そこで、私のブログでは FPGA を計測に応用することをテーマとして、基板の設計から実際のデータ処理までゆっくりと解説していきたいと思います。この ACRi への寄稿が、カスタム FPGA ボードを作って実験や計測をしようとする人の役に立てば幸いです。

自分で FPGA ボードを作る理由

自分で FPGA ボードを作る意味ってなんでしょうか?

パソコンに装着する AI アクセラレータを作ったり、FPGAってなんだろうと試してみたいならば、既存の評価ボードが良いでしょう。

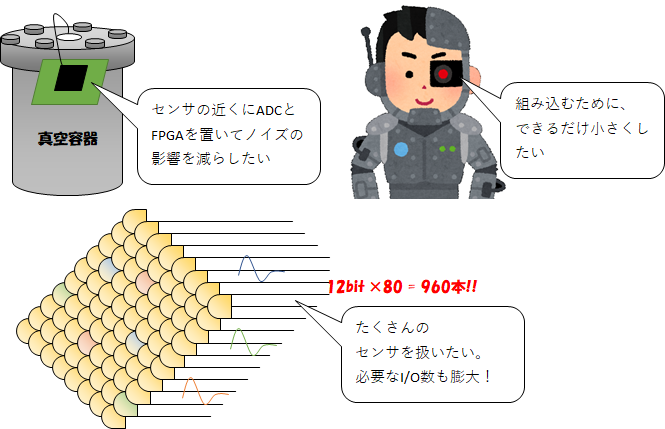

ですが、外部の物理的な世界とインタフェースする場合はそうではありません。実験対象にとても近いところにセンサを置きたい場合や、小型にしなければならない場合、非常にたくさんのセンサを並べる場合、他の装置をコントロールしたい場合など、評価ボードではできないことがたくさん出てきます。

他にも、ロボットに乗せたり、服と一緒に身に着けたり、物に埋め込む IoT 機器を作る場合もあるでしょう。そういう場合は小さく軽く作らなければなりません。消費電力やコストを抑えたいという要求もあるでしょう。

本当に汎用の評価ボードは計測に使えないのか?

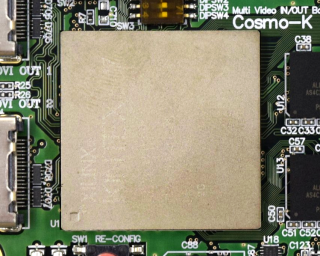

それでも、評価ボードを計測に使えるんじゃないかという方もいるかもしれません。写真1は ZED ボードという評価ボードと、ZED ボードに装着する40MHzサンプリング8chの AD コンバータ基板の図です。ZED ボードには FMC (メザニン) というコネクタがついていて、そこに LVDS の信号をたくさん通せるのでやろうと思えば拡張はできます。

ですが、実際に出来上がったものは写真1のとおりです。

2つのボードをコネクタで接続すると段差ができ、接触不良も心配になります。そもそもメザニンコネクタを使って拡張ボードを作るなら、どうせ基板を作るわけですから1枚の板にしたいと思いませんか?

FPGA ボードを自作しなければならない場合とは

具体的には、

- I/O ポートの数が足りない

- 評価ボードが大きすぎて装置に入らない

- ノイズが多くてまともに計測できない

- 既存の装置のラック (NIM/CAMAC、VMEバスなど) に組み込まなければならない

- 多数のアナログ信号や高速な信号を使う

- 評価ボードにおまけ程度についている ADC や DAC では力不足

- 評価ボードの拡張コネクタや FMC (メザニン) なので、結局、自分で基板を作らなければならない

こういう場合、自分で基板を作らざるを得なくなります。

FPGA ボードの設計は何が難しいのか?

7シリーズ以降の FPGA はすべて BGA (Ball Grid Array) というパッケージになっています。裏面に丸い足がびっしりと正方形に配列していて、手作業ではんだ付けができません。

BGA の変換基板やソケットというのは一般的ではないので、FPGA の基板を自分で作るには BGA のパッケージを扱わなければなりません。

BGA の基板を作るには最低でも4層の多層基板(普通は6層以上)が必要で、基板だけでも20万円程度、業者に実装を依頼すると10万円くらいはかかります。部品代もあるので、1回の試作に40万円くらいは軽くかかりますし、1か月くらいの期間がかかります。そのため、失敗したらはんだごてで修正するというカット&トライができません。

まさに一発勝負です。FPGA の基板設計をギャンブルにしないためには、ノウハウや知識、経験が必要になってくるのです。

回路設計の流れ

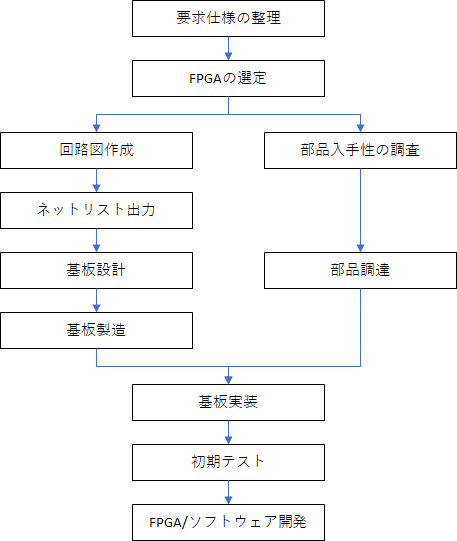

図4に基板設計の流れを示します。

FPGA の選定

最初のステップは FPGA の選定です。今回の記事では FPGA の選定方法について解説し、次回から順に基板設計に必要な知識を紹介していきます。

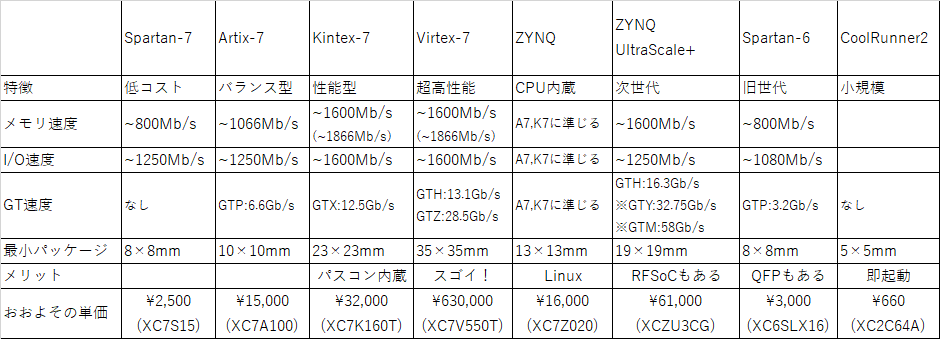

2020年現在の Xilinx 社の主な製品を表1に示します。

デバイスの価格

価格は重要な要素です。表1は2020年4月現在の価格を Digikey で調べたものです。もちろん FPGA のロジック規模や速度によって大きく変わってきますが、ファミリと金額の桁の関係はこのくらいだと思ってください。

例えば FPGA にかけるコストが1万円以下なら Spartan-7。1万から3万なら Artix-7。3万~10万円かけてもよいなら Kintex-7です。Virex-7 は最小のデバイスでも30万円以上、最高で400万円以上するので使うだけで自慢できそうですね。

ZYNQ は Artix-7 や Kintex-7 に CPU が乗ったものですが価格はあまり変わらないので、CPU を乗せたコントローラを作るなら FPGA + CPU の構成にするよりも ZYNQ を強く推奨します。

I/O とパッケージでほぼ決まる

コストは重要な要素ですが、実験機器などで1台から数台作りたい場合にはあまり重要でないこともあります。それよりも、作りたいものが実現できるかどうかを決めるのは、I/O 性能とパッケージサイズです。

実際には規模 (LUT 数や内蔵メモリのサイズ) が問題になることはあまりありません。それよりも、 I/O ピンの要求、パッケージサイズの要求、コスト、電力の順に決めていくことになるでしょう。

I/O の性能

普通に I/O からロジック信号を出すだけでは100MHzかせいぜい200MHzどまりですが、Xilinx の FPGA は、I/O に OSERDES や ISERDES といったプリミティブを使うことで飛躍的に性能を向上させることができ、800MHzや1GHzといったクロック速度で信号を入出力できるようになります。

DDR メモリや I/O の速度が1250Mb/sを超える場合は Artix-7 は使えません。表1の数値は最高速度(-3)ランクの FPGA を使った場合なので、-1や-2の FPGA では当然遅くなります。詳しくは”7 series ac dc“でググってデータシートを見てください。

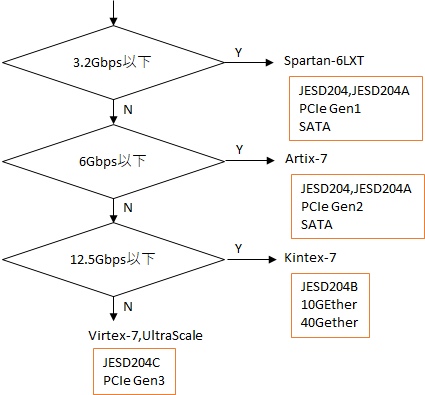

ギガビットトランシーバ

Xilinx 社の FPGA には、GTP、GTX、GTH、GTZ、GTY、GTM というギガビットトランシーバが搭載されています。GTP→GTX→GTH→GTZ→GTY→GTM の順に性能が良くなります。Artix-7 の GTP は6.6Gbpsまで、Spartan-6 の GTP は3.2Gbpsまでです。

通常の I/O でも ISERDES や OSERDES を使うことで1Gb/s超の速度で通信できますが、GT* を使うとさらに高速で高度な通信ができます。高度というのは K28.5 などのカンマでコントロールされるプロトコルが使えるという意味です。エラー検出や同期などが行えるというメリットがあり、さまざまな近代的インタフェースで使われています。

3Gbps程度でよいならば Artix-7 のトランシーバ搭載型で十分です。10Gイーサネットや40Gイーサネットなど、10Gbpsでの通信をしたいのであれば Kintex-7 以上が必要です。

なお、Spartan-7 には GTP はありません。

13Gbps以上が必要な場合 (JESD204C などの高速 ADC/DAC インタフェースを使用する場合)は、ZYNQ UltraScale+ の GTH を使う必要が出てきます。

GTY、Z、M は途方もない速度が出ますが、多値ロジックなので、Xilinx 社の FPGA 以外とインタフェースする場合には気を付けてください。

普通の AD コンバータや CMOS イメージセンサでは汎用 I/O ピンで十分ですが、SATA、PCIe、JESD204、SDI を使う場合は迷わず GT* が搭載されたデバイスを選びます。

ZYNQのギガビットトランシーバ

UltraScale ではない ZYNQ7000 シリーズは、元になるデバイスが Artix-7 か Kintex-7 かによって I/O 性能が決まります。XC7Z020 以下は Artix-7、030 以上は Kintex-7 が搭載されています。ZYNQ の型番が015のように5で終わっているものはトランシーバ搭載型です。

パッケージ

パッケージの選定は重要です。大きすぎても小さすぎても基板のコストに大きな影響を与えるからです。

例えば、小さいサイズの機器に組み込む場合を考えてみます。指先サイズのカメラを作りたいような場合は8x8mmの Spartan-7 や、10x10mmの Artix-7 を使うことになるでしょう。

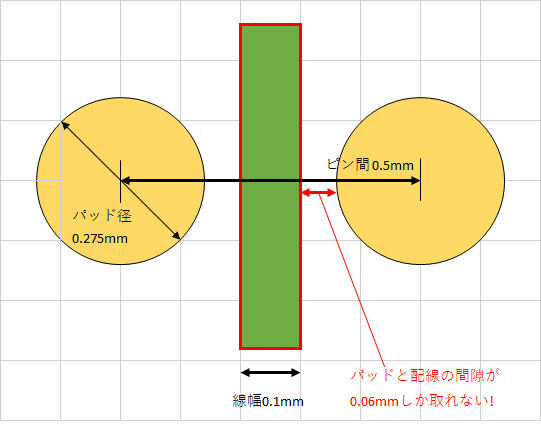

しかし、0.5mmピッチであるため、安価な6層基板のデザインルール (線幅/間隙=0.1mm/0.1mm) では BGA の端子間に引ける配線がなく、75μmのルールにするか、パッドオンビアを使う必要がでてきて、基板の製造コストが上がります。

図6は、0.5mmピッチのパッケージでは0.1mm/0.1mmルールでピン間の配線が引けないことを示しています。

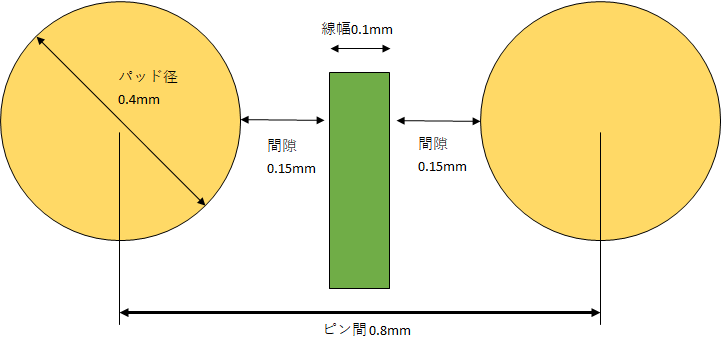

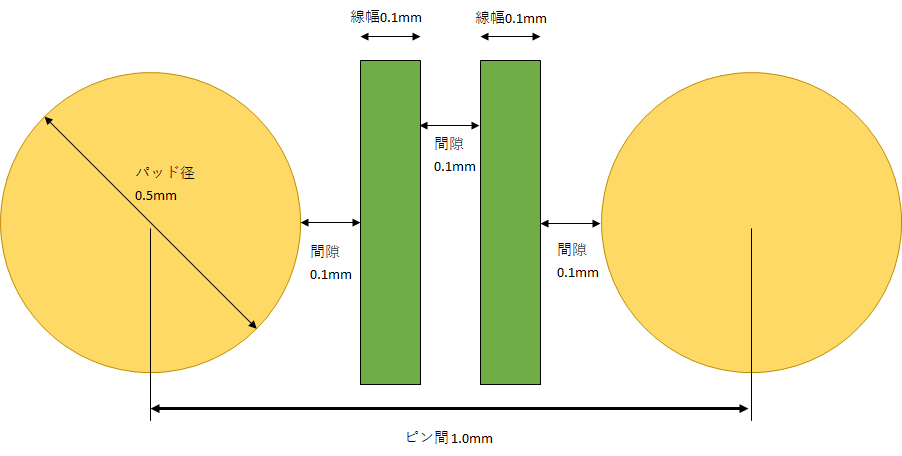

安価な6層基板のデザインルール(線幅/間隙=0.1mm/0.1mm)で設計できるのは、324ピンから676ピンの0.8mmまたは1.0mmピッチの FPGA です。具体的には

- 0.8mmピッチの CSG324/325 ピン 15×15mm

- 1.0mmピッチの FTG256 ピン 17×17mm

- 1.0mmピッチの FGG484 ピン 23×23mm

- 1.0mmピッチの FFG/FBG676 ピン 27×27mm

となりますが、0.8mmピッチであれば端子間に1本、1.0mmピッチであれば端子間に2本の配線が引けます。また、端子の斜めの隙間にビアが置けるので設計のしやすさとコストでメリットがあります。

デバイスのパッケージが大きくなると、6層基板では BGA の内側の配線が引き出せなくなってきて、層数が増やさざるを得なくなって基板のコストが上がります。具体的には900ピン以上になると内層が2層で足りなくなるので、8層以上の基板が必要になります。結論を言えば、最も安価に作れるのは FTG256 ~ FGG676 ピンで、900ピン以上だと層数が増え、CPG を使うと追加のオプションが必要になります。

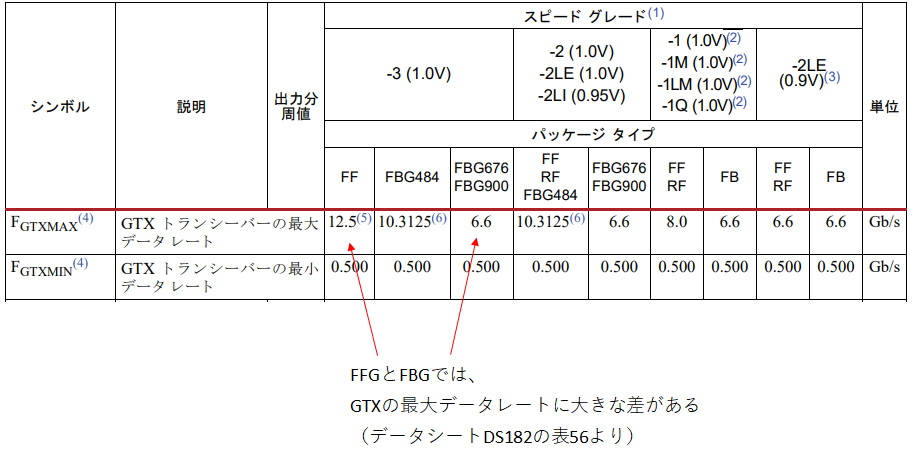

コラム FFG パッケージと FBG パッケージ

ZYNQ やKintex には FFG パッケージと FBG というパッケージがありますが、迷わず FFG を選んでください。

FFG は表面が平らなのでヒートシンクが貼り付けられますが、

FBG にヒートシンクを貼り付けるのはかなり難しいです。

また、FFG は GTX の性能が良く12.5Gbp/sまで行けますが、FBG では6.6Gb/sまでです。

ロジックリソースと、デバイス間の移行(マイグレーション)

今日ではロジックリソースが足りなくなるということはまずありませんので、LUT サイズを気にする必要はあまりないでしょう。内蔵メモリ (BRAM) が足りなくなることはあるかもしれませんが。

パッケージが決まったら、コストが許す範囲でロジック規模の一番大きなものを選んでおきます。Xilinx 社の FPGA は、同じファミリで同じパッケージであれば、ピン配置にも互換性があるので容易に移行できます。このことをマイグレーションとも言います。

大きなデバイスで作っておいて、もし量産するならば同じパッケージで小さなものに変更するというわけです。

個々のファミリの選択の指針

UltraScale+ について

表1では、ZYNQ UltraScale+ しか載せていませんが、実際には Kintex UltraScale、Kintex UltraScale+、ZYNQ UltraScale、ZYNQ UltraScale+、Virtex UltraScale、Virtex UltraScale+ の6種類があります。

また、ZYNQ UltraScale+ には RFSoC といって高速 ADC 内蔵のタイプもあります。安価な評価ボードは ZYNQ UltraScale+ のものなので、ZYNQ UltraScale+ が一番有名ですね。

Artix-7 と Kintex-7 の選択のポイント

Artix-7 にするか Kintex-7 にするかで迷ったら、以下の基準で考えてください。

- 外部の端子を1.25Gbps以上で動かす必要があるか?

- DDR メモリの速度が800Mb/sを超える必要があるか?

- 6.7Gbps以上のトランシーバが必要か?

- 電源のパスコンを省略したいか?

- ロジックリソースがたくさん必要か?

一つでも YES があれば、Kintex を選びます。

ZYNQ を選ぶのはどんなとき?

イーサネットや USB ホストを使いたいのであれば、どうしてもソフトウェアでプロトコルを処理する必要が出てきます。そのため、CPU と OS の補助が必要になります。

FPGA の隣に汎用の CPU を置くことができるのであれば、FPGA+CPU というシステム構成もありですが、データのやりとりが面倒になるので FPGA と CPU が一つのパッケージに入った「ZYNQ (ジンク) 」を使ったほうがはるかに楽にできます。

ZYNQ には3種類あって、XC7Z20 以下の Artix-7 型 ZYNQ と、XC7Z030 以上の Kintex-7 型 ZYNQ です。Artix-7 型 ZYNQ は PL が Artix-7 でできているので、I/O は HR ポートしかなく、GTX も6.6Gbpsまでしか出せませんが、Kintex-7 型 ZYNQ は PL が Kintex-7 でできているので、HR ポートのほか HP ポートも使えて GTX は12.5Gbpsまでいけます。

Spartan-7 の出番は?

Saprtan-7 は7シリーズの廉価版ですが、実験や研究で作りたいものは一点物の装置だと思います。1000円や2000円を削るようなコスト重視の量産品ではないので Spartan-7 を選ぶメリットはありません。

逆に、IoT 端末をばらまくような場合は Spartan-7 を検討してください。

Spartan-6、Spartan-3 の出番はあるか?

これらを選ぶメリットはほとんどありません。Spartan-6 を選択する唯一のメリットは、XC6SLX4 および LX9 に QFP144 ピンのデバイスがあることです。ただし、6シリーズでは Vivado は対応していないので ISE を使うことになるので、どうしてもという場合でなければ7シリーズを使ったほうがよいでしょう。

Spartan-3 には QFP パッケージが豊富にあるので、どうしても基板を作るコストとリスクが負担できない場合、つまり非常に小規模な FPGA 基板製作を初めて試したい場合にはありかもしれません。

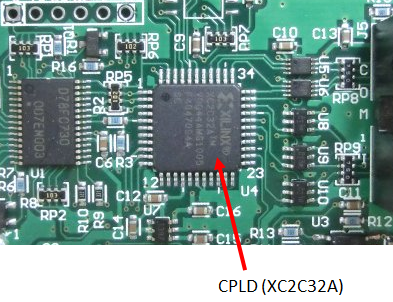

コラム CPLD とは

CPLD とは Complexed PLD の略で、複数の PLD を1つのパッケージにまとめたものがそもそもの始まりです。LUT ベースの FPGA と CPLD は本質的に違う構造で、100個程度の AND や OR やフリップフロップをまとめるいわゆる「グルーロジック」に使います。

CPLD のメリットは電源ONと同時にすぐに起動することです。そのため、電源ONですぐに正しいロジックを出さなければならない用途(モーターに危険な信号を与えないようにするなど)には使い道があるかもしれません。(本来はそういうところに使ってはいけないのだが)

なお、他社も CPLD を出していますが、他社の CPLD は FPGA と変わらない LUT 構造でコンフィグ ROM を内蔵したものです。Xilinx 社の XC95 や CoolRunner II とは本質的に構造が違い、中規模から大規模なロジックが入ります。

次回の予告

次回は FPGA の I/O ピンの使い方について解説します。

お楽しみに。