この記事では、ACRi ルームのコンピュータと FPGA を利用して、Verilog HDL で記述される簡単なカウンタ回路を動作させて、その挙動を確認する方法を説明します。

Verilog HDL で記述したハードウェアの内容や、論理合成、配置・配線といった処理の詳細は後回しにします。Vivado を活用して、FPGA を動かすこと、動かした FPGA の動作を確認することを目標にします。

FPGA の設計・開発に慣れていないみなさんを対象とする初級の内容です。ACRi ルームのコンピュータに接続して、手を動かしながら進めていきましょう。

ファイル (main.v, main.xdc) を準備する

ACRi ルームの Arty A7 が接続されているコンピュータにログインして、リモート デスクトップで接続します。ACRi ルームのコンピュータにリモート デスクトップで接続する方法については、こちらの記事を参考にしてください。

Arty A7 評価ボードで利用する制約ファイル (design constraint file) を準備します。次の内容で、main.xdc という名前のファイルを作成してください。作成したファイルは、ACRi ルームのコンピュータに保存してください。

set_property -dict {PACKAGE_PIN H5 IOSTANDARD LVCMOS33} [get_ports r_out];

set_property -dict {PACKAGE_PIN E3 IOSTANDARD LVCMOS33} [get_ports w_clk];

create_clock -add -name sys_clk -period 10.00 [get_ports w_clk];上のリンクからファイル main.xdc をダウンロードすると良いかもしれません。

次に、Verilog HDL のファイルを準備します。次の内容で、main.v という名前のファイルを作成しましょう。作成したファイルは、ACRi ルームのコンピュータに保存してください。

module m_main(w_clk, r_out);

input wire w_clk;

output reg r_out = 0;

reg [31:0] r_cnt = 0;

always @(posedge w_clk) r_cnt <= r_cnt + 1;

vio_0 m (w_clk, r_cnt);

always @(posedge w_clk) r_out <= ^r_cnt;

endmodule上のリンクからファイル main.v をダウンロードすると良いかもしれません。

main.xdc と main.v のファイルは、例えば、ACRi ルームのコンピュータのホームディレクトリに code というディレクトリを作って、その中に保存しておきます。

Vivado のプロジェクトを作成する

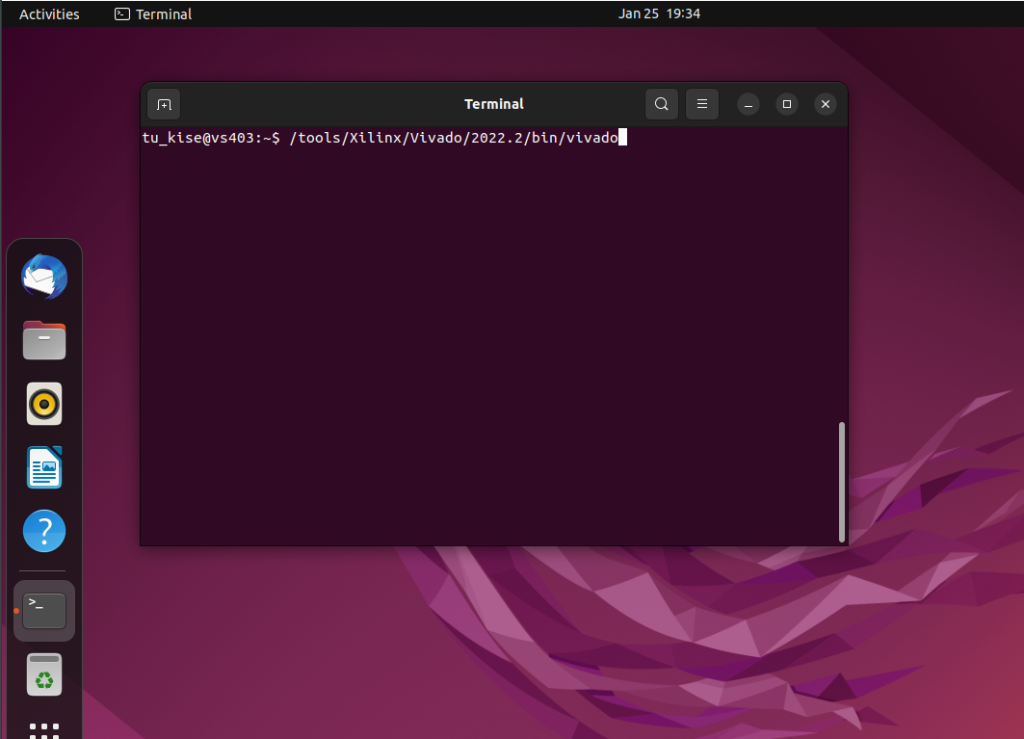

(1) Vivado 2022.2 を立ち上げましょう。

ターミナルから、次のコマンドで、Vivado 2022.2 を立ち上げます。(リモート デスクトップで接続して「Control キーと Alt キーを押しながら t を押す」とターミナルが起動します。)

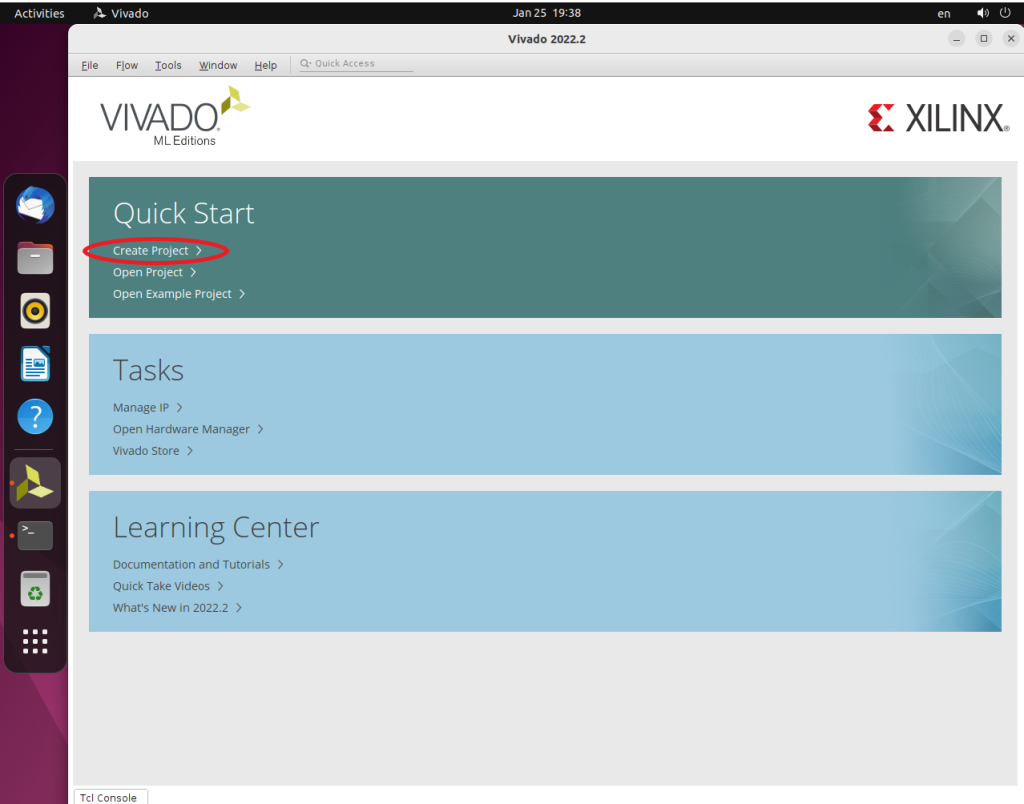

$ /tools/Xilinx/Vivado/2022.2/bin/vivado上に、コマンドを実行する直前の画面を示します。コマンドを実行すると、次の Vivado の画面が表示されます。

(2) 上の Vivado の画面で、赤色の丸でハイライトした Create Project をクリックします。

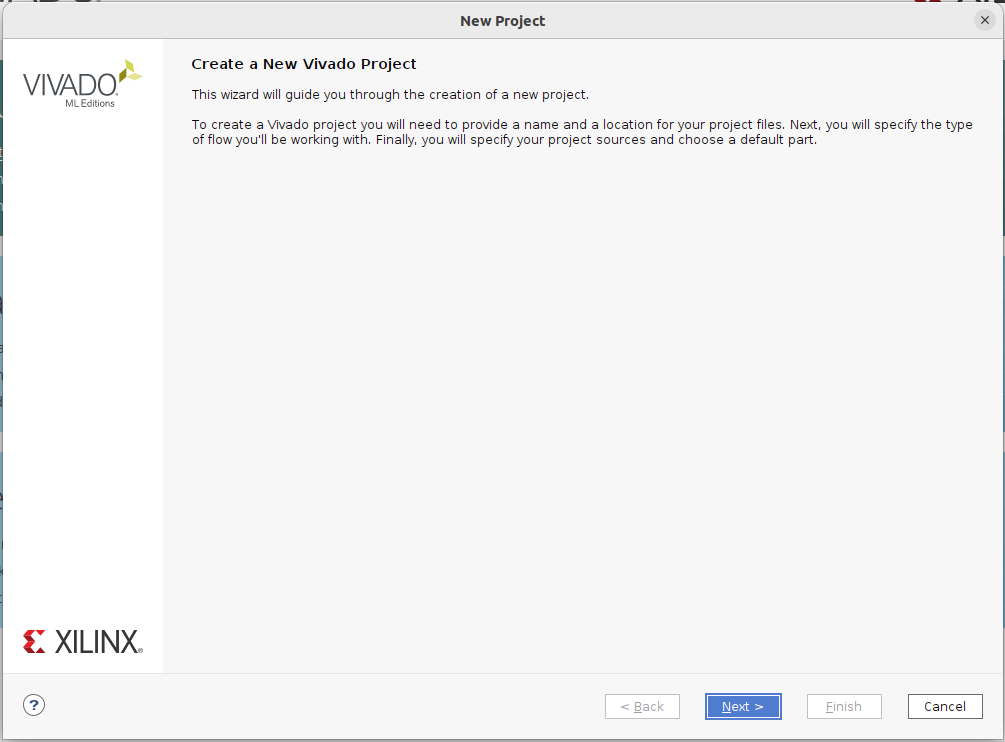

(3) 上の New Project ウィンドウで、青色になっている Next をクリックします。

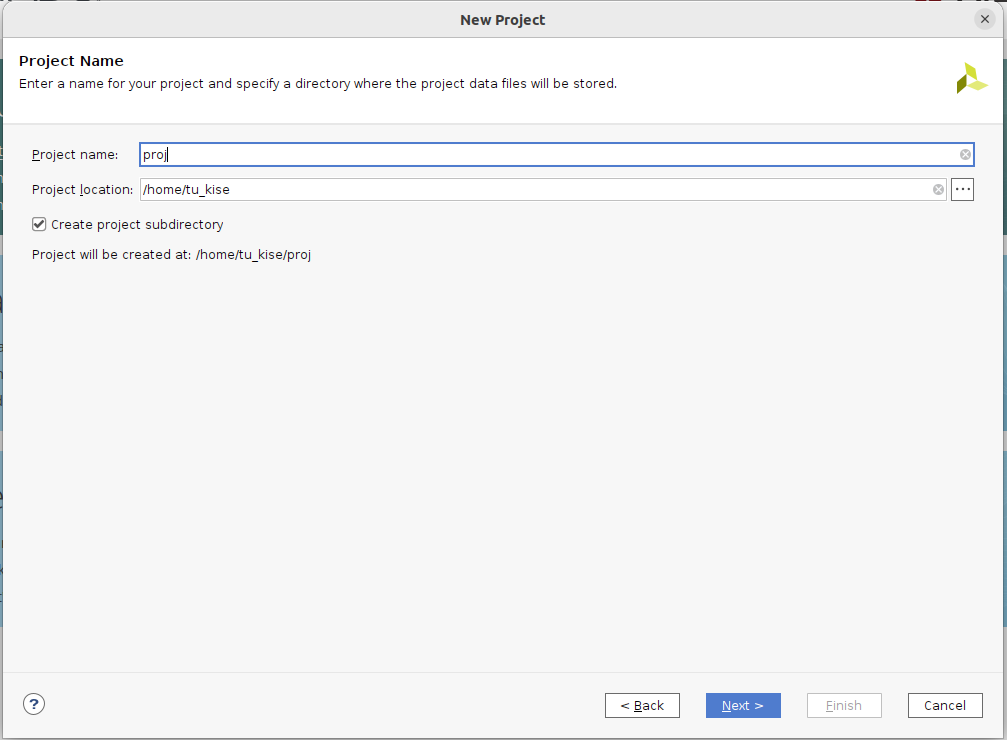

(4) 上のウィンドウの Project name: に適切なプロジェクト名を入力して、Project location: で適切なフォルダを選択して、青色になっている Next をクリックします。例えば、プロジェクト名は proj にすると良いでしょう。標準で指定されている project_1 を利用しても大丈夫です。

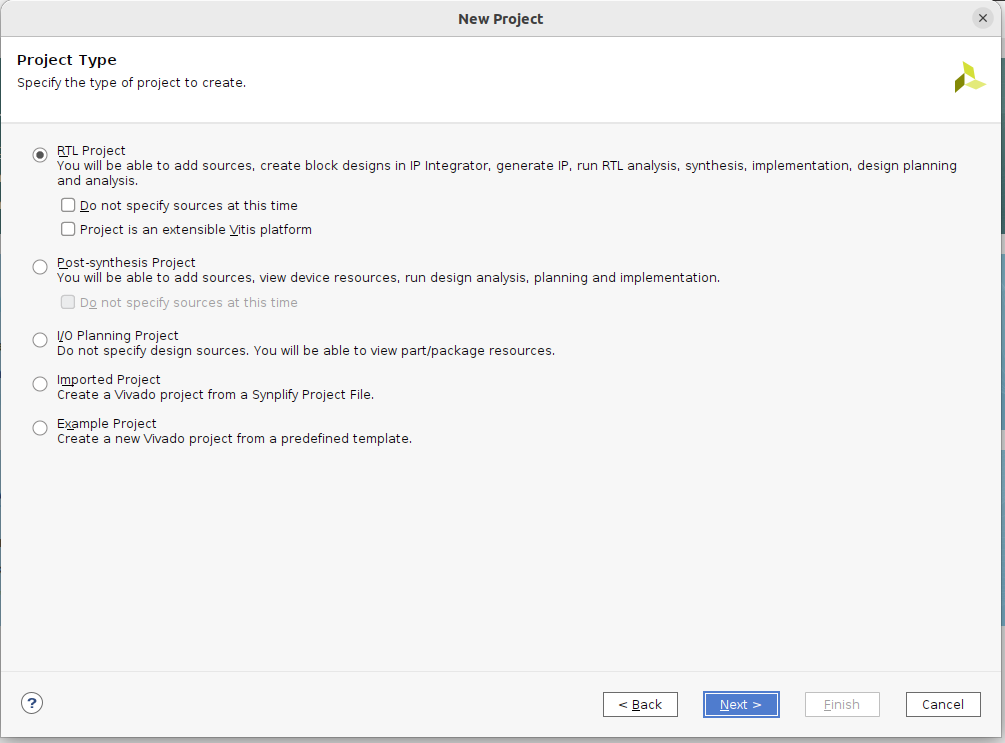

(5) 上の Project Type のウィンドウで、RTL Project を選択して、青色の Next をクリックします。

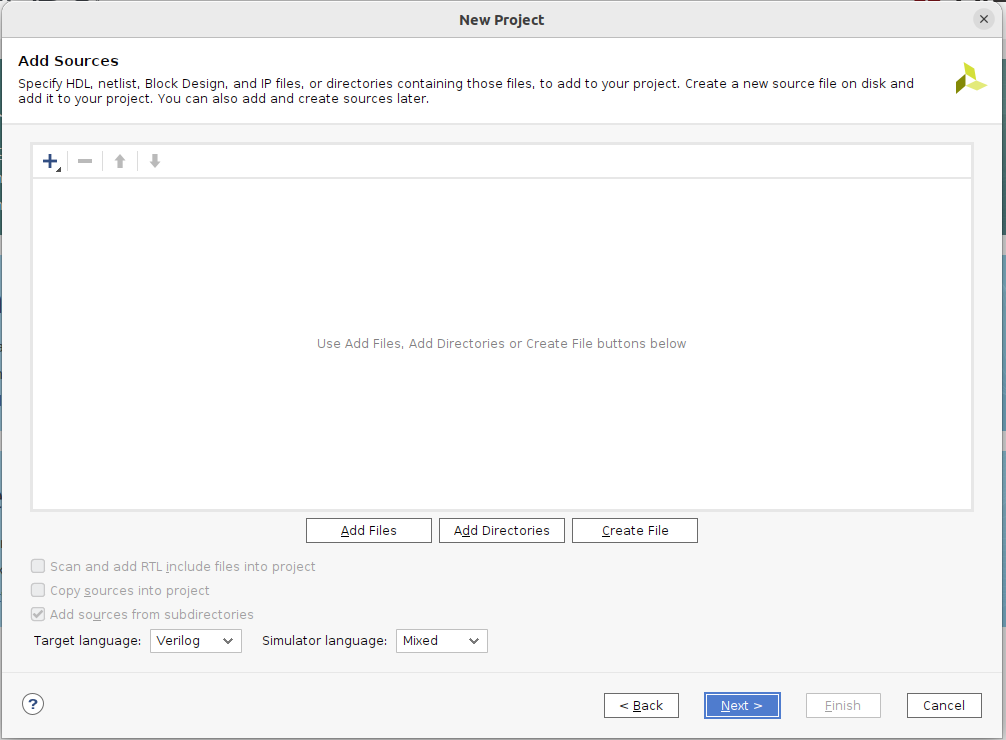

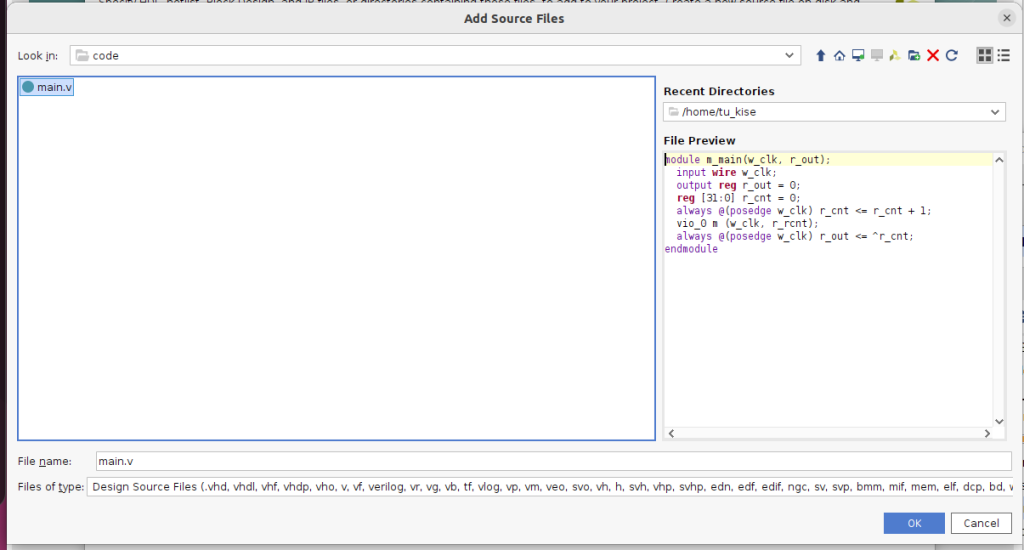

(6) 先に保存した main.v の追加。

次の Add Sources のウィンドウで、Add Files ボタンをクリックします。

表示される Add Source Files ウィンドウで、先に保存した main.v を選択して、青色の OK をクリックします。

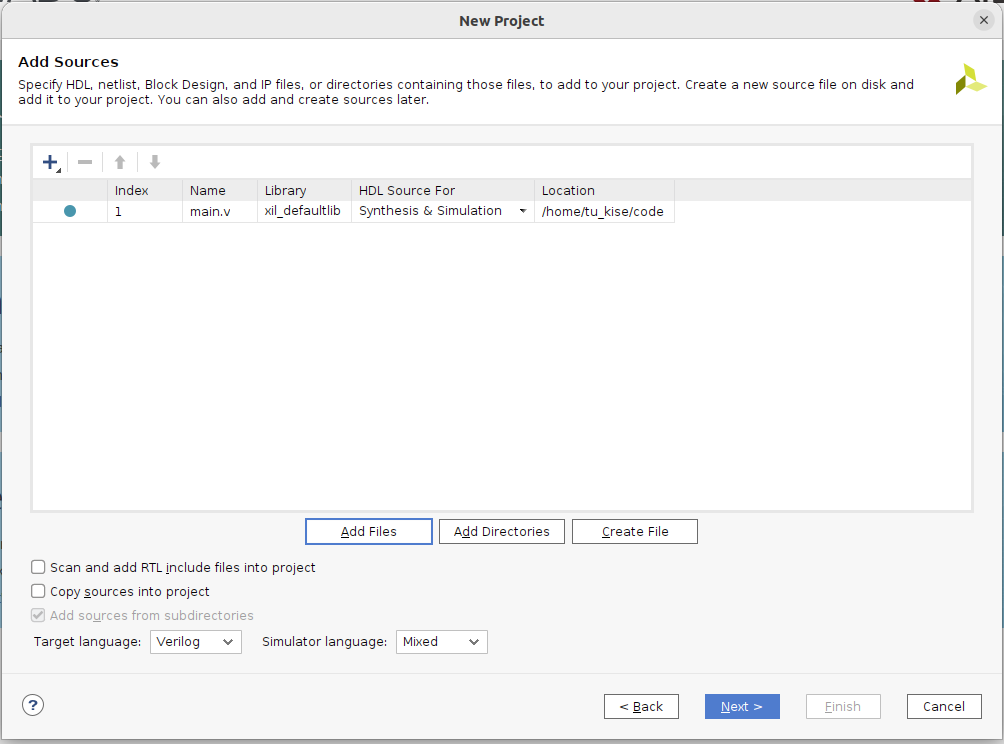

次の画面の通り、Add Sources ウィンドウで、main.v が追加されることを確認して、青色の Next をクリックします。

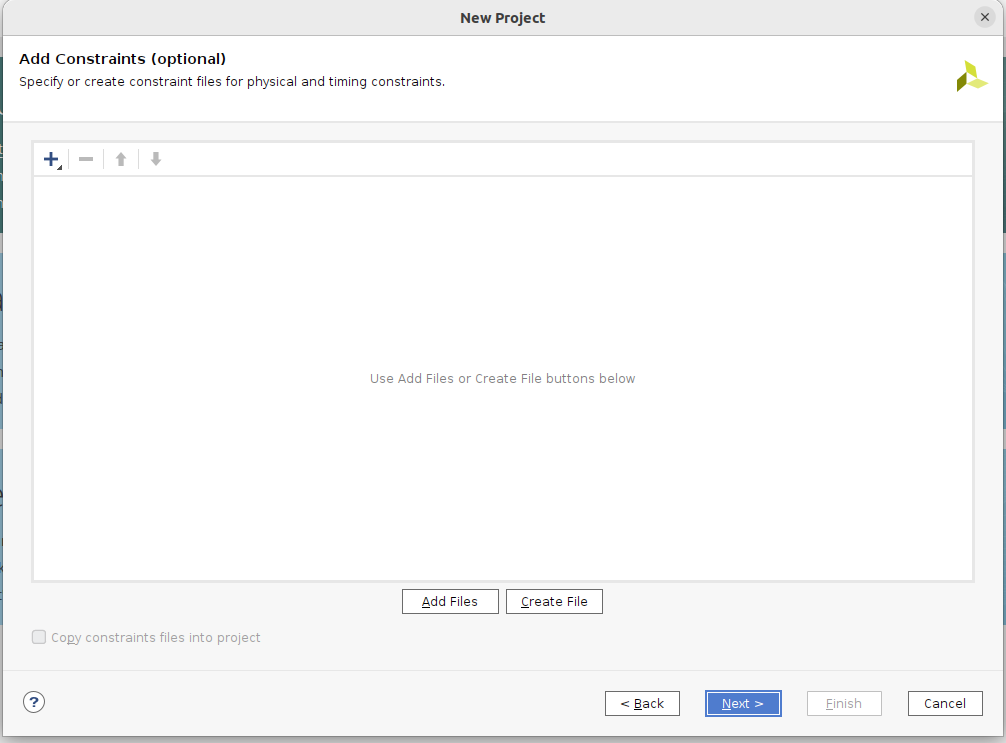

(7) 先に保存した main.xdc の追加。

次の Add Constraints (optional) のウィンドウで、Add Files ボタンをクリックします。

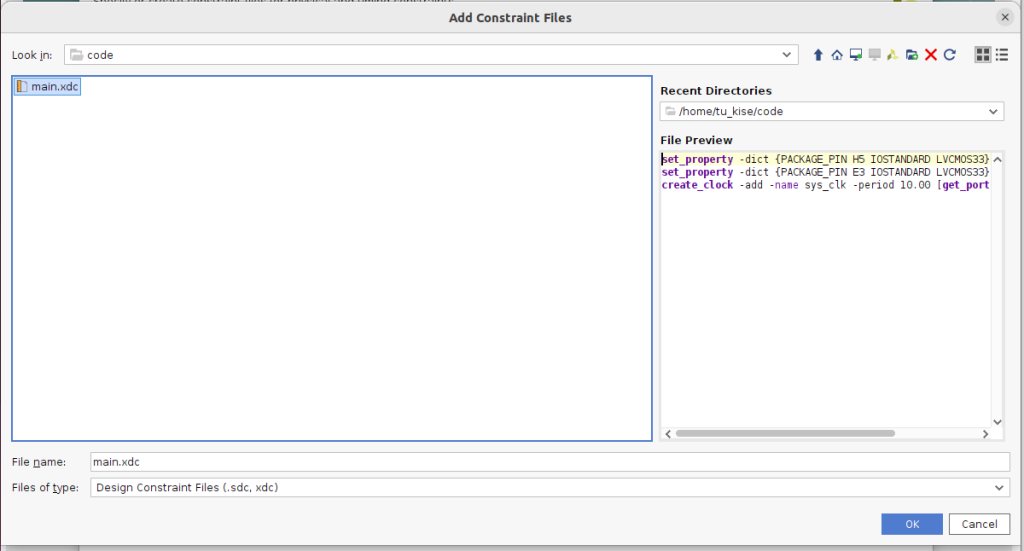

表示される Add Constraint Files ウィンドウで、先に保存した main.xdc を選択して、青色の OK をクリックします。

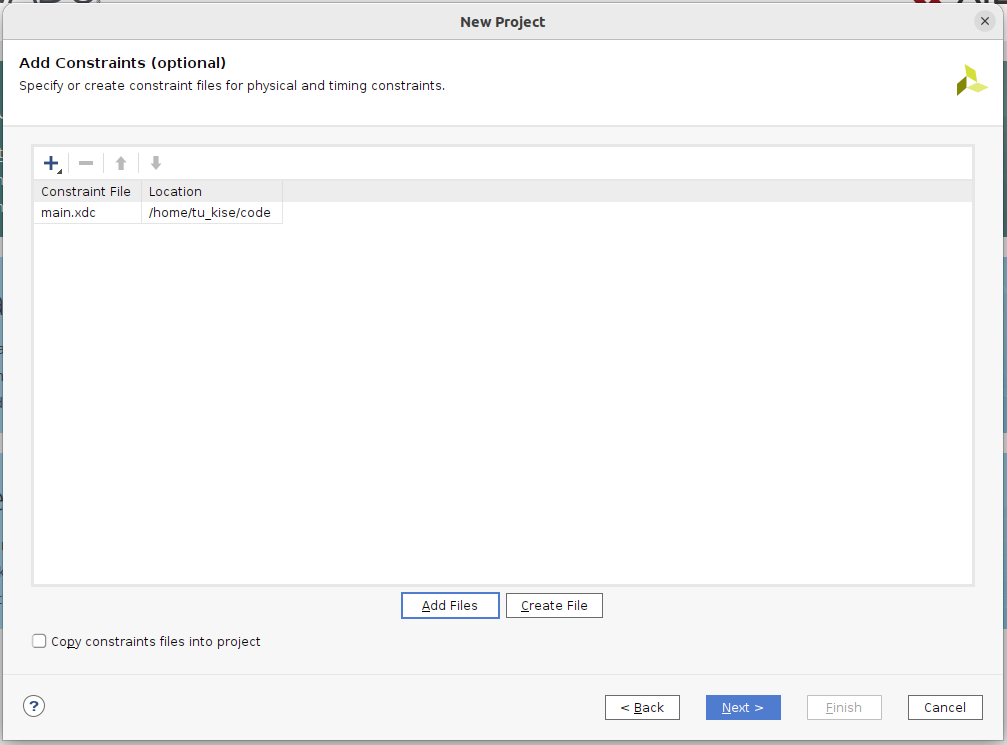

次の画面の通り、Add Constraints (optional) のウィンドウで、main.xdc が追加されることを確認して、青色の Next をクリックします。

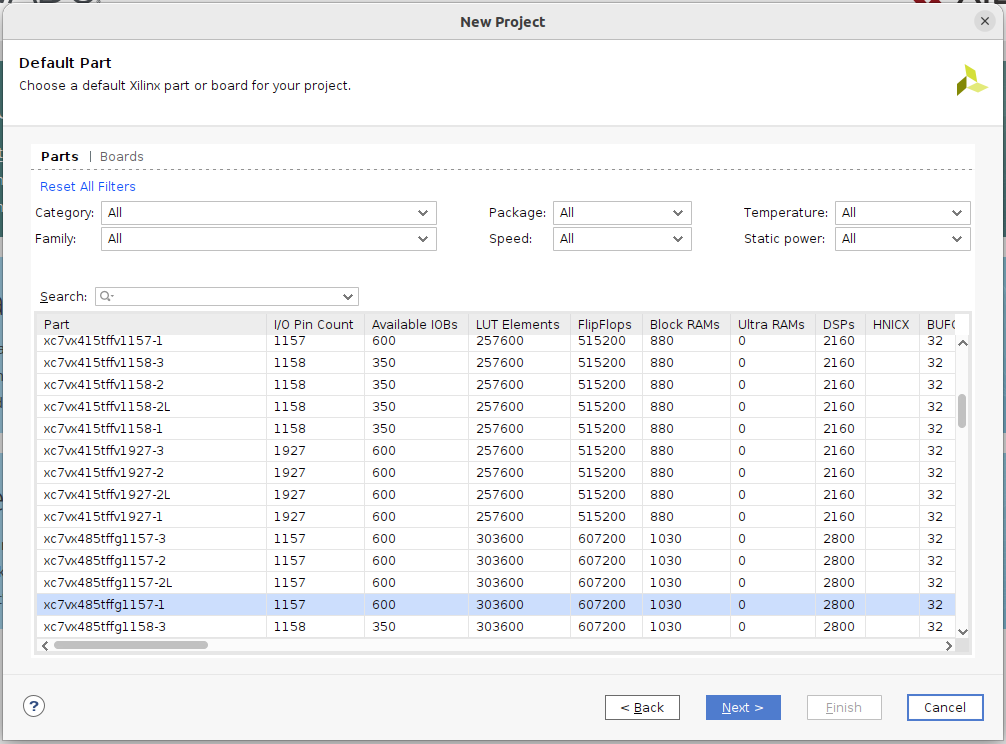

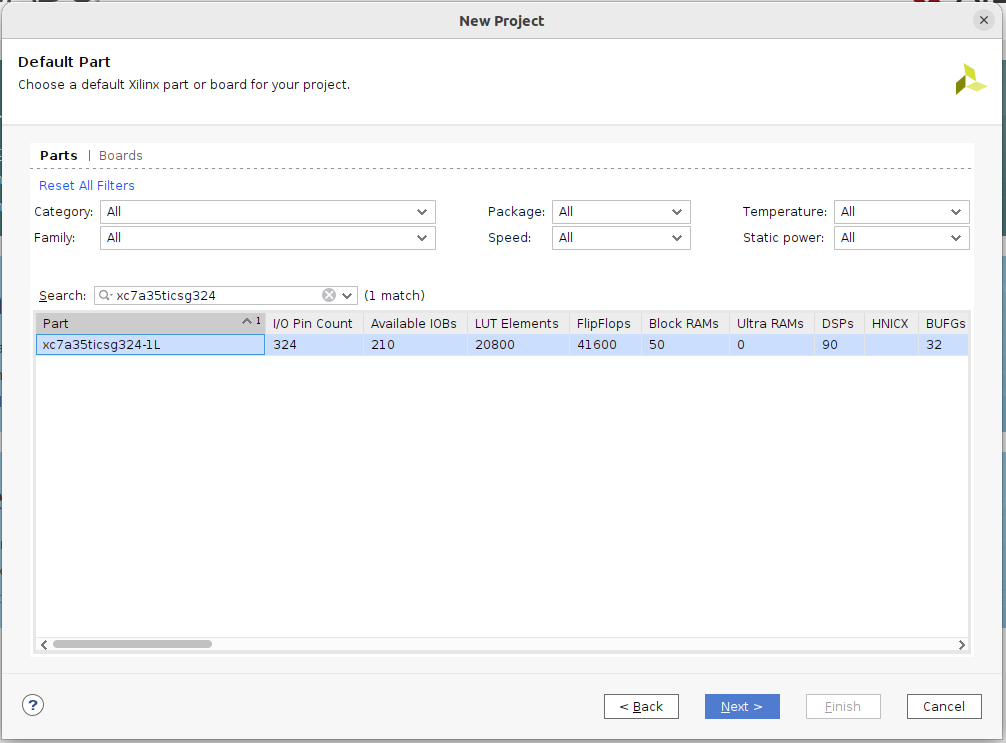

(8) FPGAの選択。

次の Default Part のウィンドウで、利用する FPGA を選択します。Arty A7評価ボードを利用する場合には、xc7a35ticsg324-1L を選択したいので、Search: のボックスに、xc7a35ticsg324と入力しましょう。

Search: のボックスに、xc7a35ticsg324と入力すると、次の画面のように、灰色の Part の下に、xc7a35ticsg324-1L が表示されます。これをクリックして選択すると、Next が青色になるので、この青色の Next をクリックします。

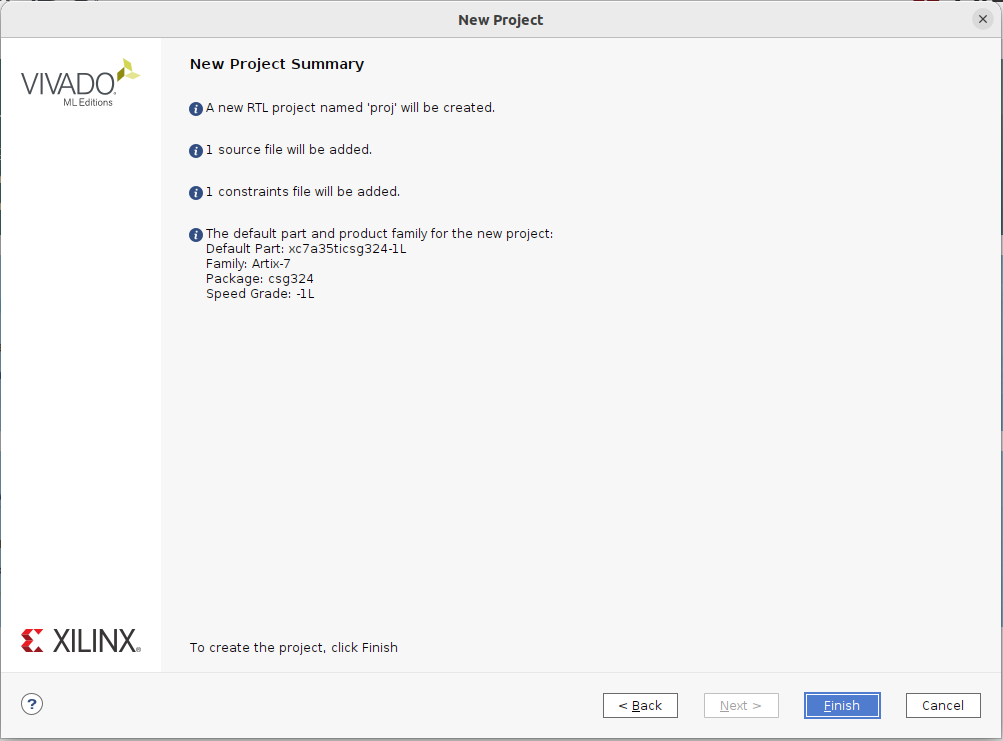

(9) 次の画面のように、New Project Summary として設定が表示されます。内容を確認して、青色の Finish をクリックします。

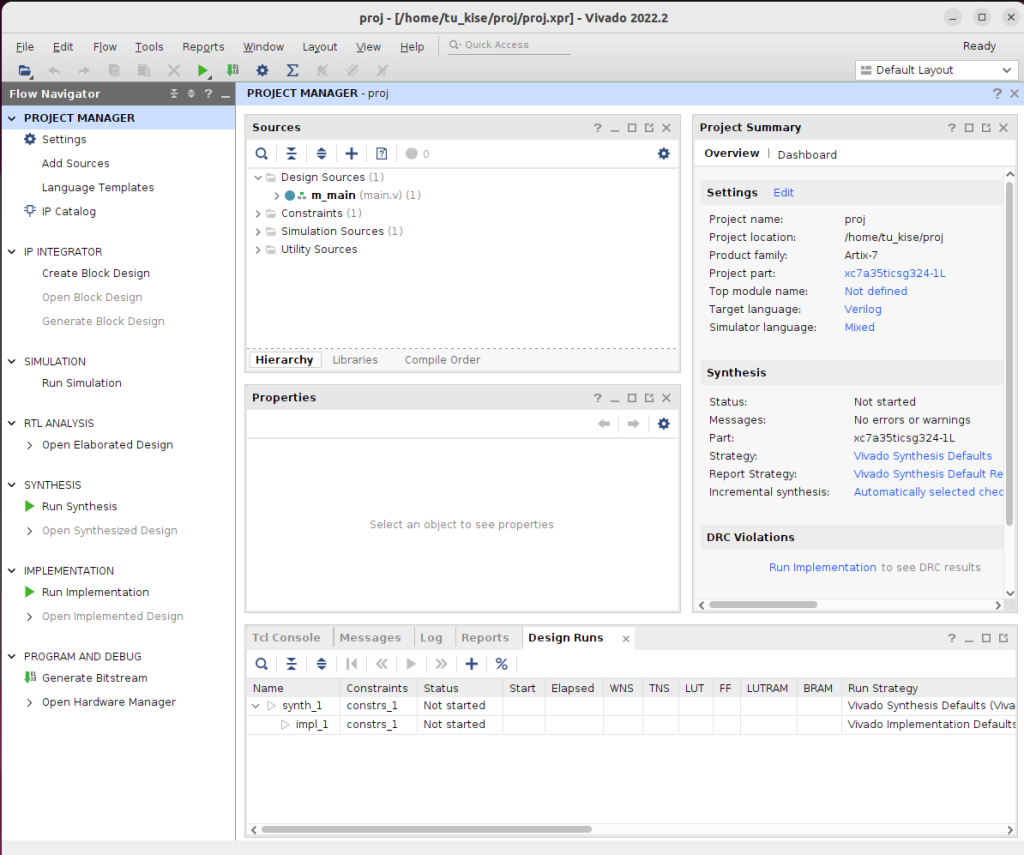

これで新しいプロジェクトが作成されました。次の、Vivado の画面が表示されます。

提供される IP の VIO (virtual input/output) を生成する

ACRi ルームのコンピュータに接続されている FPGA ボードの LED の状態を見ることは難しいので、FPGA の内部の値を読み書きする機能を持つ VIO (virtual input / output) とよばれるモジュールを利用することにします。

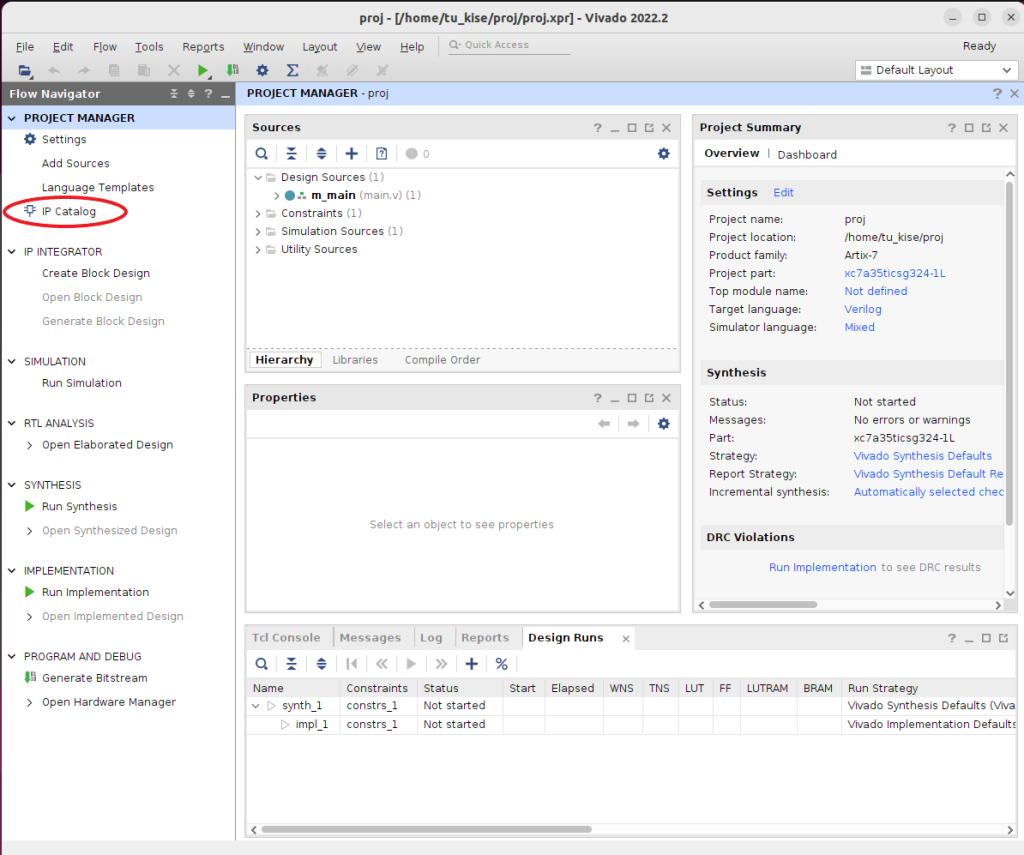

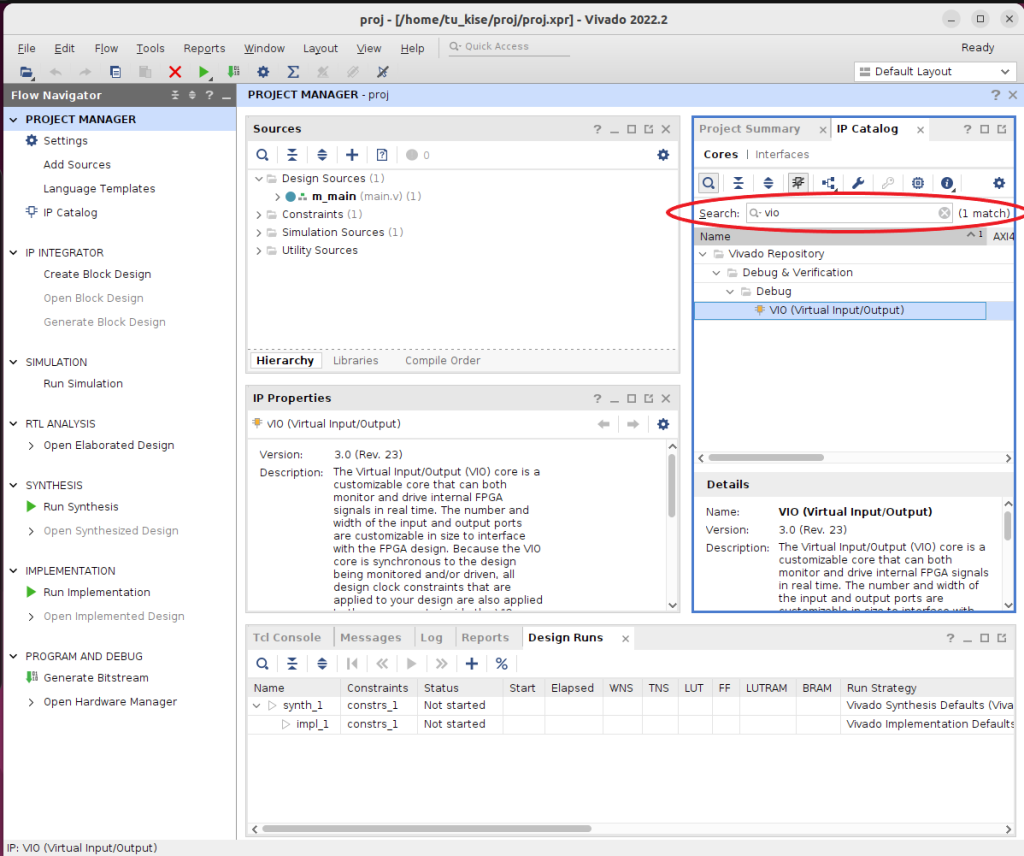

(10) 次の Vivado の画面の Flow Navigatorから、赤色でハイライトした IP Catalog をクリックします。

(11) 次の画面の赤色でハイライトしたように、右側の Search: の ボックスが現れるので、そこにvioと入力します。出てくる青色の VIO (Virtual Input/Output) をダブルクリックします。

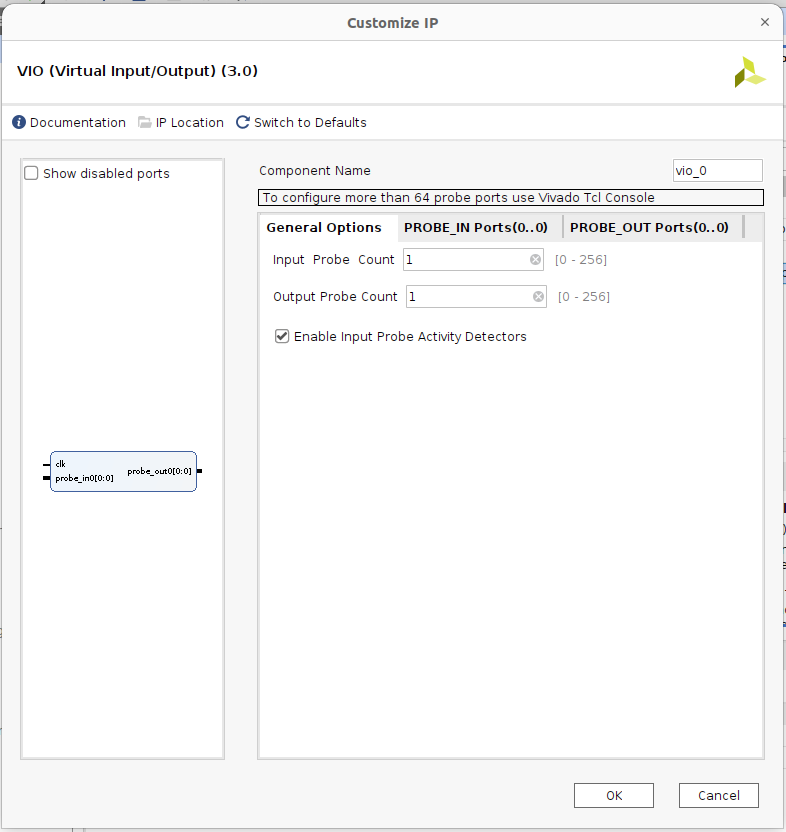

(12) 次のが図の Customize IP, VIO (Virtual Input/Output) (3.0) というウィンドウが表示されます。

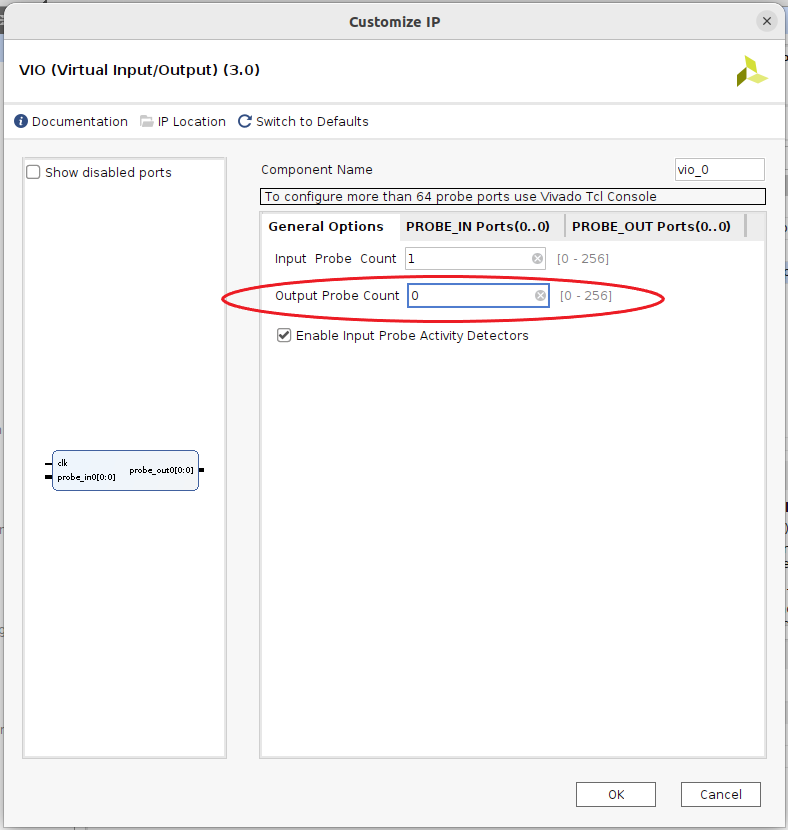

次の図のように、 Input Probe Count は 1 のままで変更せず、赤色でハイライトしたOutput Probe Count を 0 に変更します。

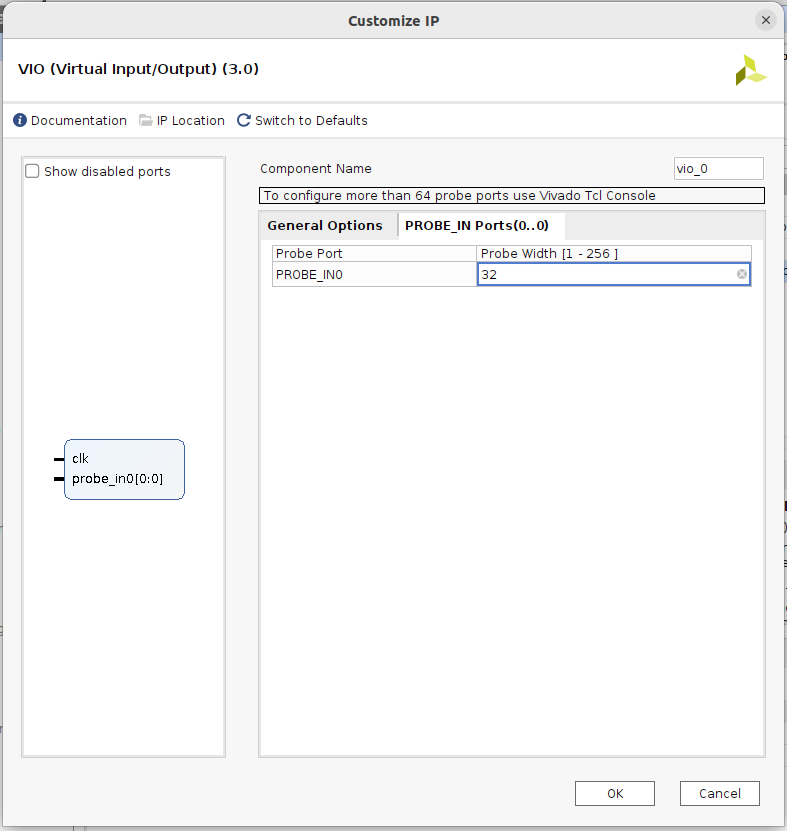

(13) 同じウィンドウの PROBE_IN Ports(0..0)をクリックして表示される PROBE_IN0 の Probe Width[1 – 256] を、標準で表示される 1 から 32 に変更して、ウィンドウ下側の OK をクリックします。次の図は、値を 32 に変更した後のものです。この状態で、OK をクリックします。

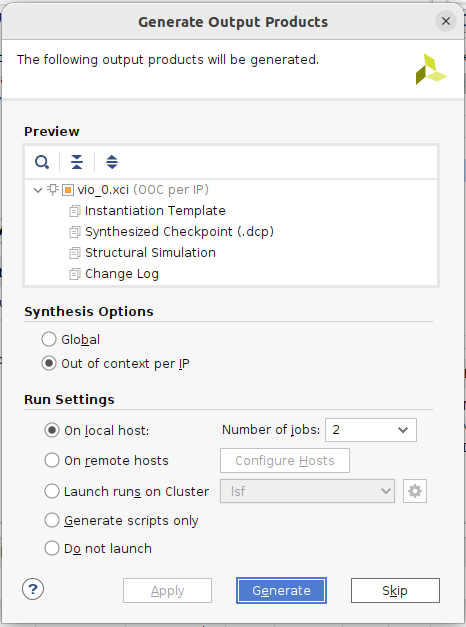

(14) 次の図の Generate Output Products のウィンドウが現れるので、表示されている設定を修正しないで、青色の Generate をクリックします。

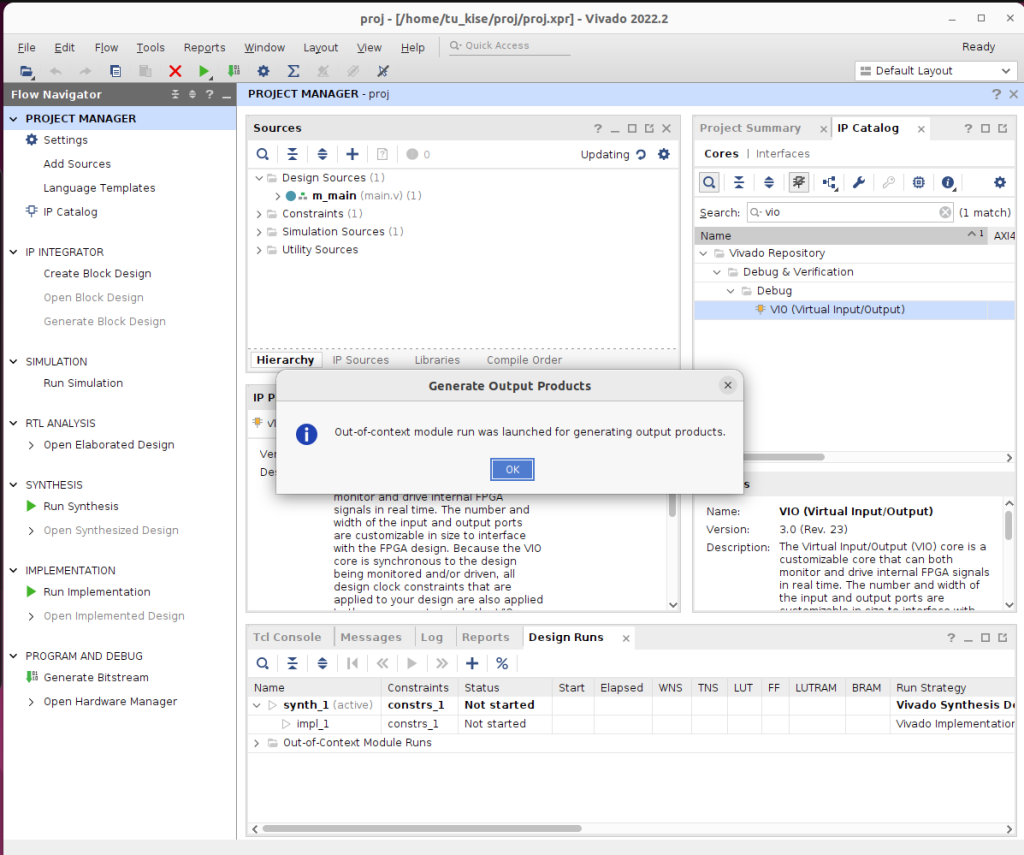

(15) 少し待つと、Generate Output Products の ウィンドウが現れて、Out-of-context module run was … というメッセージが表示されるので、青色の OK をクリックします。

これで、FPGA の内部の値を読み書きする機能を持つ VIO の IP が生成されました。

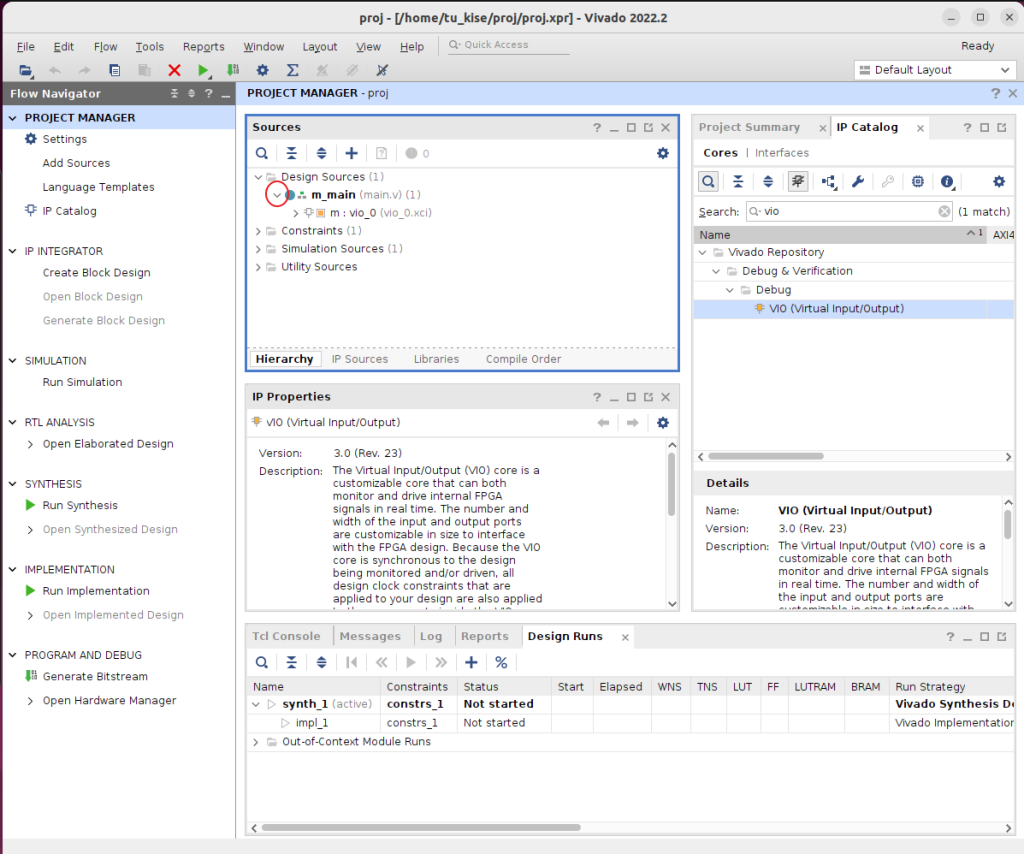

次の図のように、トップモジュールの m_main の左側の、赤でハイライトした部分をクリックしてください。m_main に含まれるインスタンス名が m の vio_0 が表示されます。この図のように、その m : vio_o (vio_0.xcl) の左のアイコンがオレンジ色になっていれば、IP の生成は成功しています。(このアイコンが赤色の ? になっていると、IP の生成に問題があることになります。)

論理合成、配置・配線、ビットストリームファイルの生成を行う

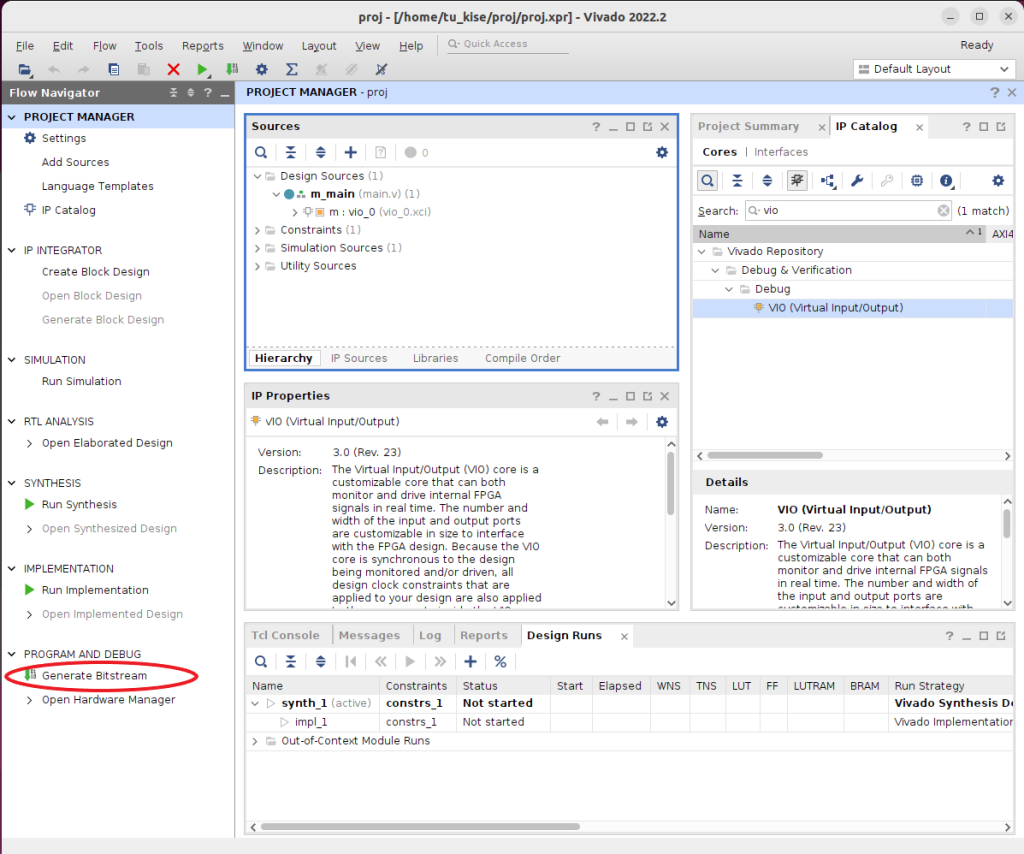

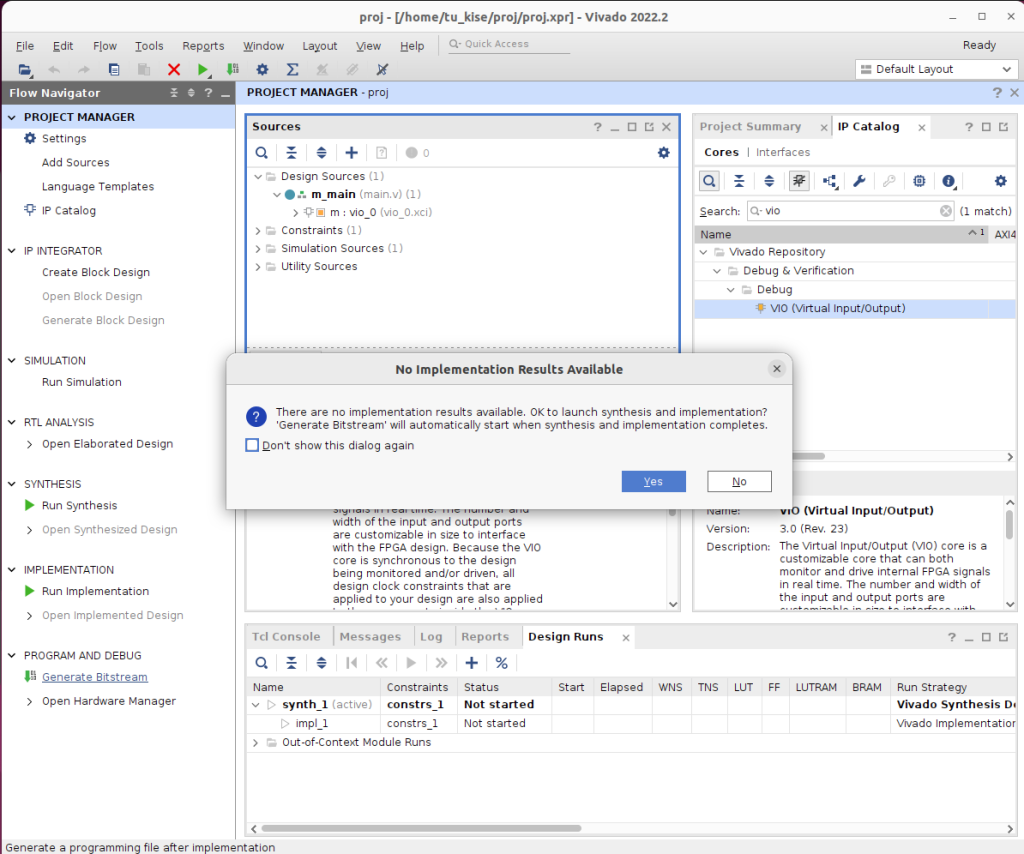

(16) 次の図の Flow Navigator の下部にある PROGRAM AND DEGUG の下の、赤色でハイライトした Generate Bitstream をクリックします。

(17) 次の図のように、現れる No Implementation Results Available のウィンドウのメッセージを確認して、青色の Yes をクリックします。

その後、Launch Runs ウィンドウが表示されることがあります。その場合には、設定を変更しないで、OK をクリックしてください。

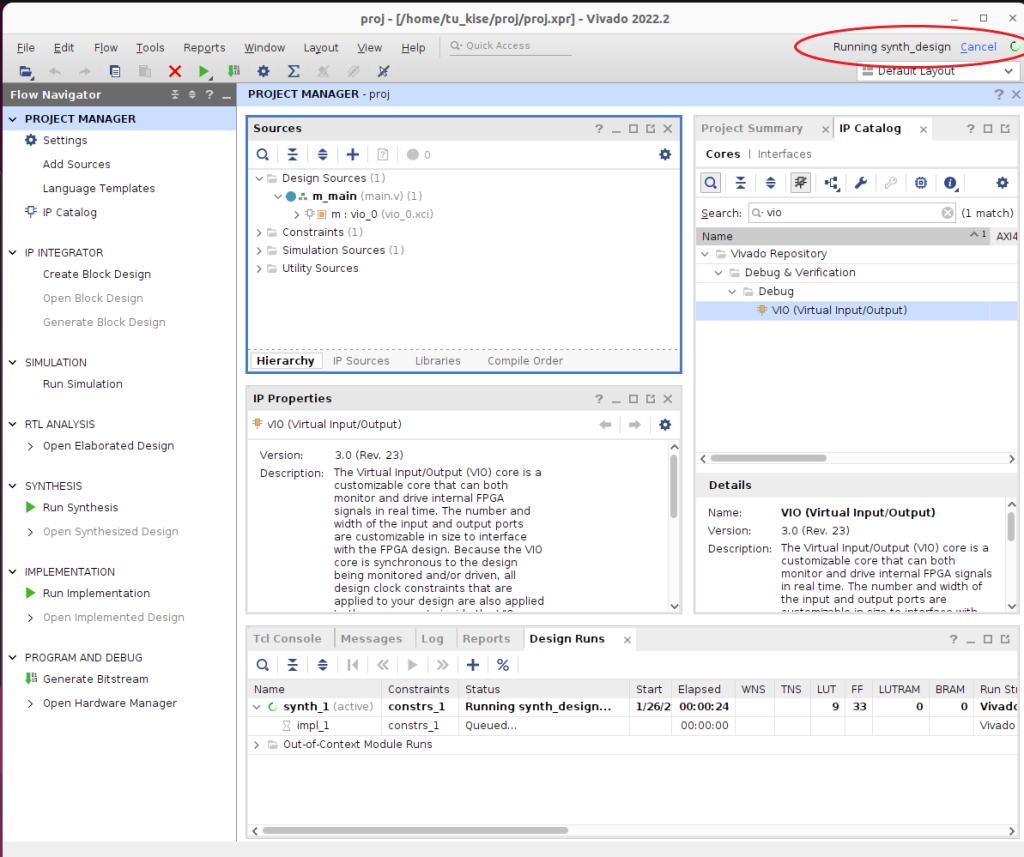

(18) 論理合成、配置・配線、ビットストリームファイルの生成の処理が始まるので、終わるまで待ちましょう。次の図の赤色でハイライトしたように、Vivadoの右上の緑の丸が回転しているときは、作業が進んでいる状態です。

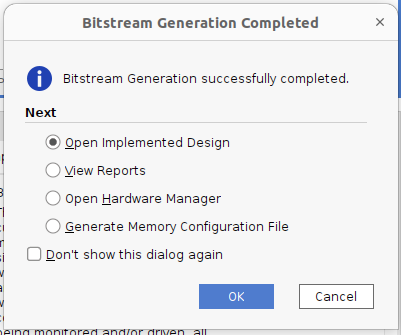

次の図の Bitstream Generation Completed ウィンドウが表示されることがあります。その場合には、白色の Cancel をクリックします。

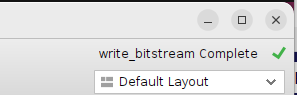

次の図のように、Vivado の画面の右上に write_bitstream_Complete と表示され、その右に緑色の✓が表示されていれば、ここまでの作業に成功しています。

FPGA をコンフィギュレーションする

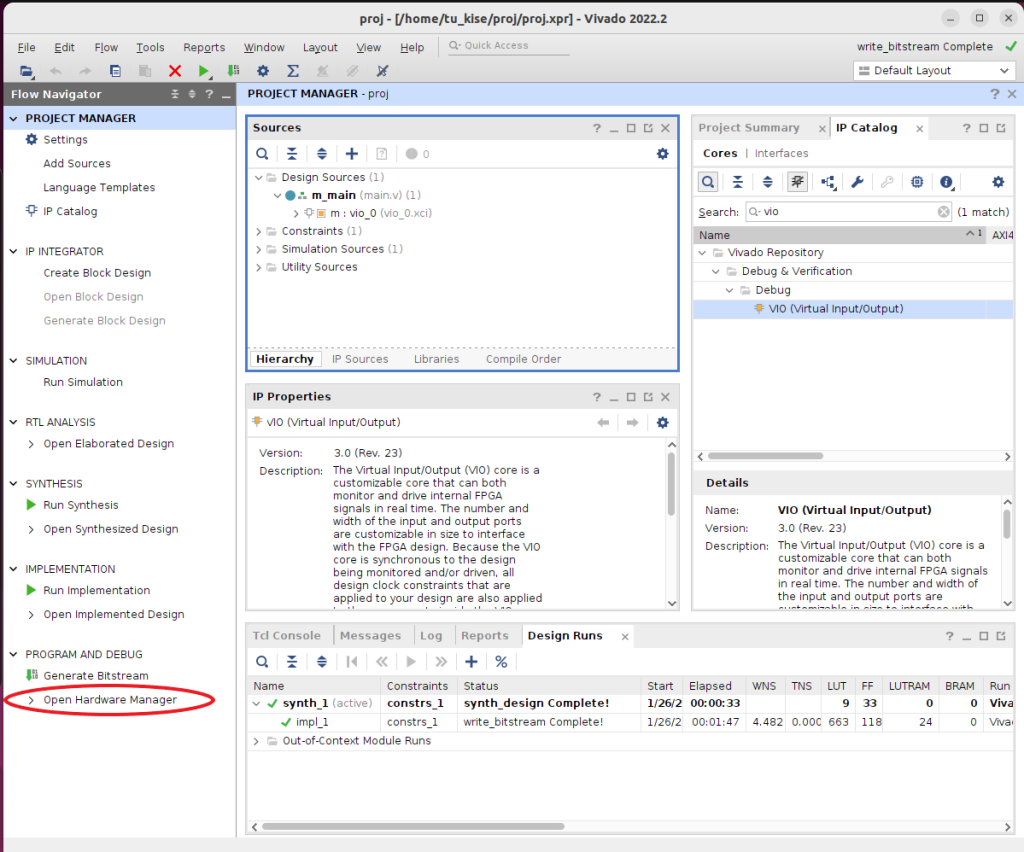

(21) 次の図の Flow Navigator の下部にある PROGRAM AND DEGUG の下の、赤色でハイライトした Open Hardware Manager をクリックします。

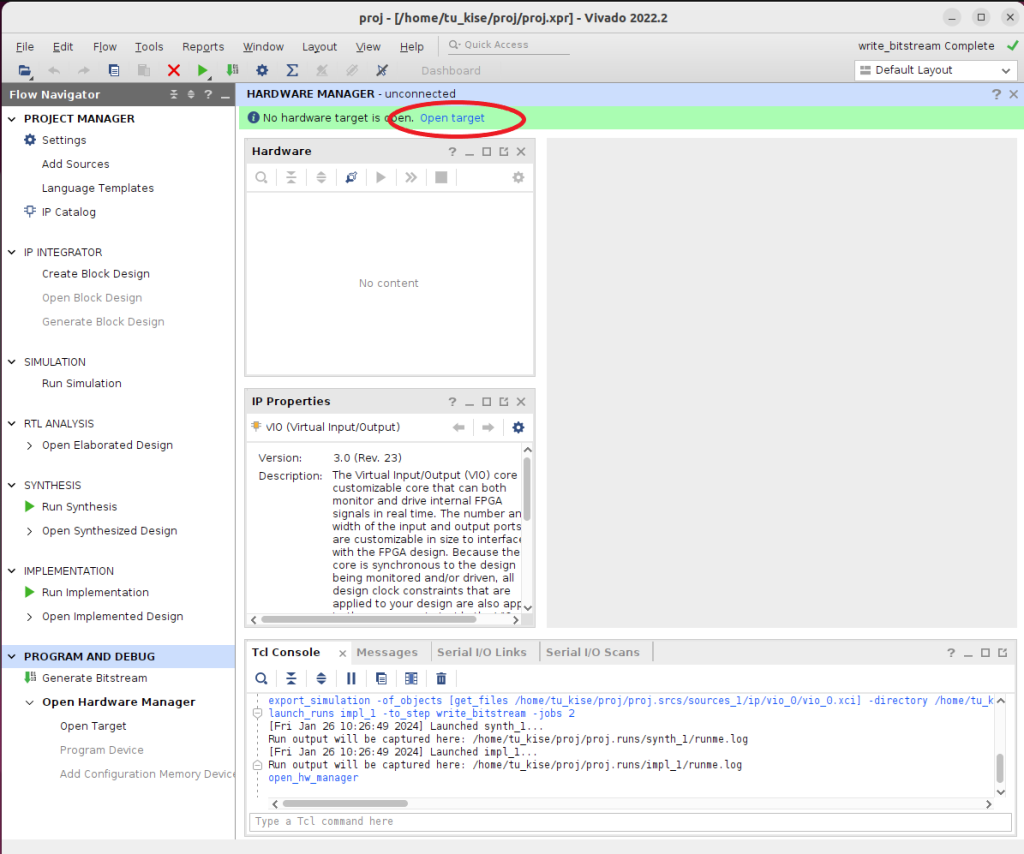

(22) 次の図の赤色でハイライトした、HARDWARE MANAGER の緑色のバーの Open target をクリックします。

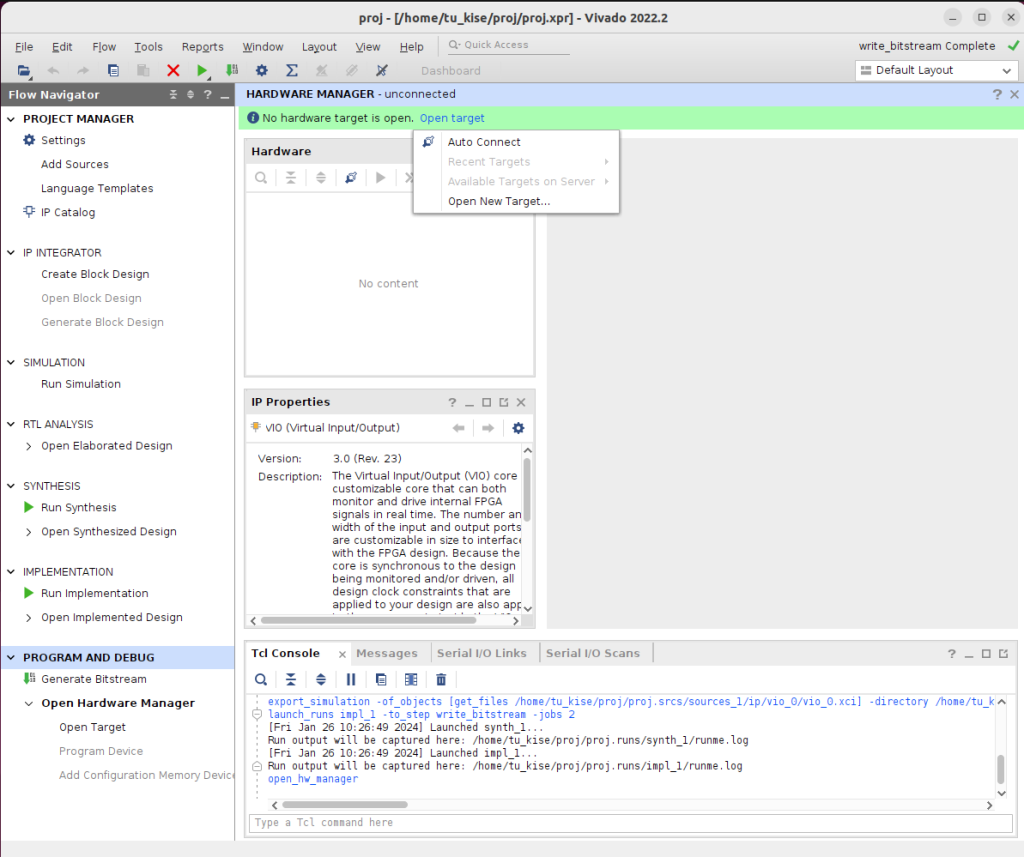

Open target をクリックすると、次の図のように、Auto Connect などが表示されるので、その Auto Connect を選択してクリックします。

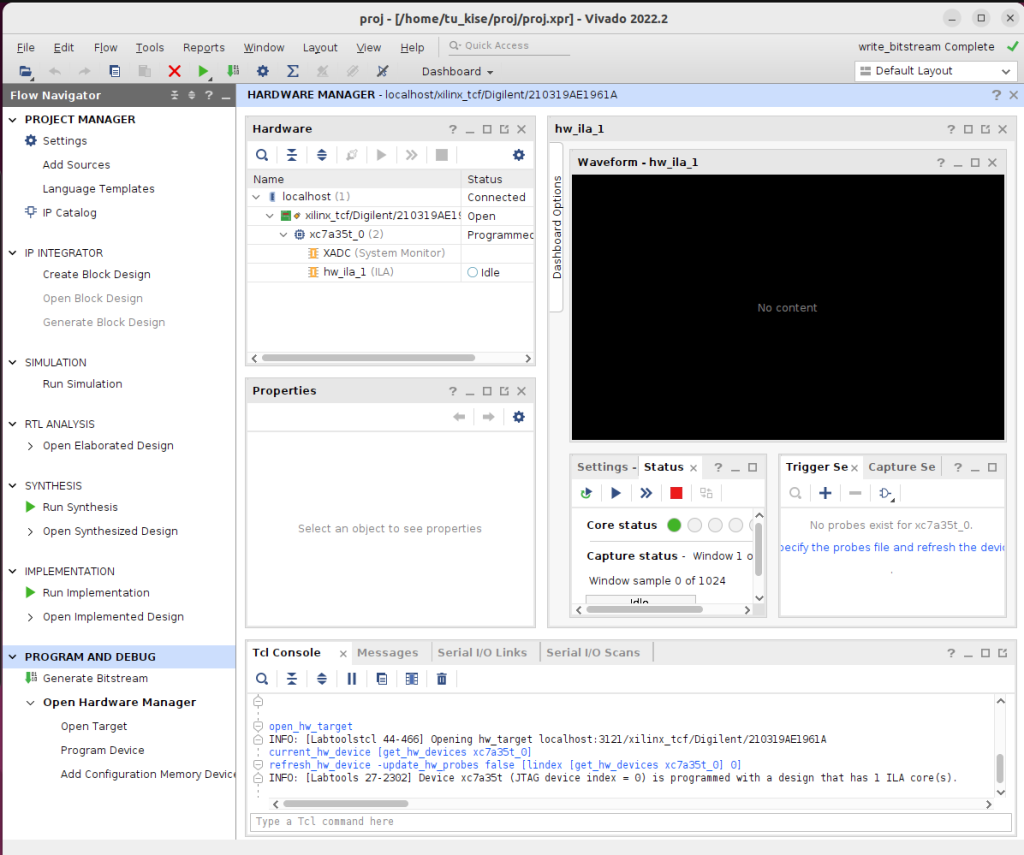

(23) 次の図のように、FPGAに接続して、Hardware ウィンドウに xc7a35t が表示されます。

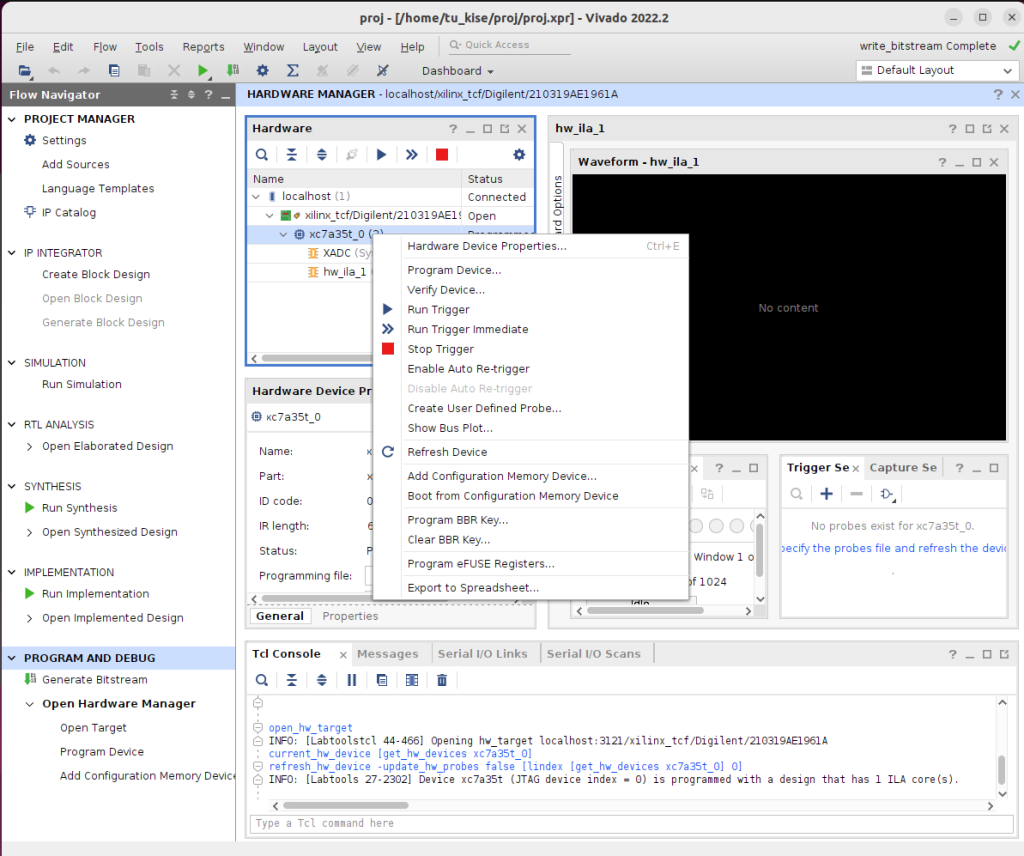

(24) Hardware ウィンドウで、xc7a35t_0 の部分をクリックすると、次の図のように、メニューが表示されます。そこから、Program device をクリックします。

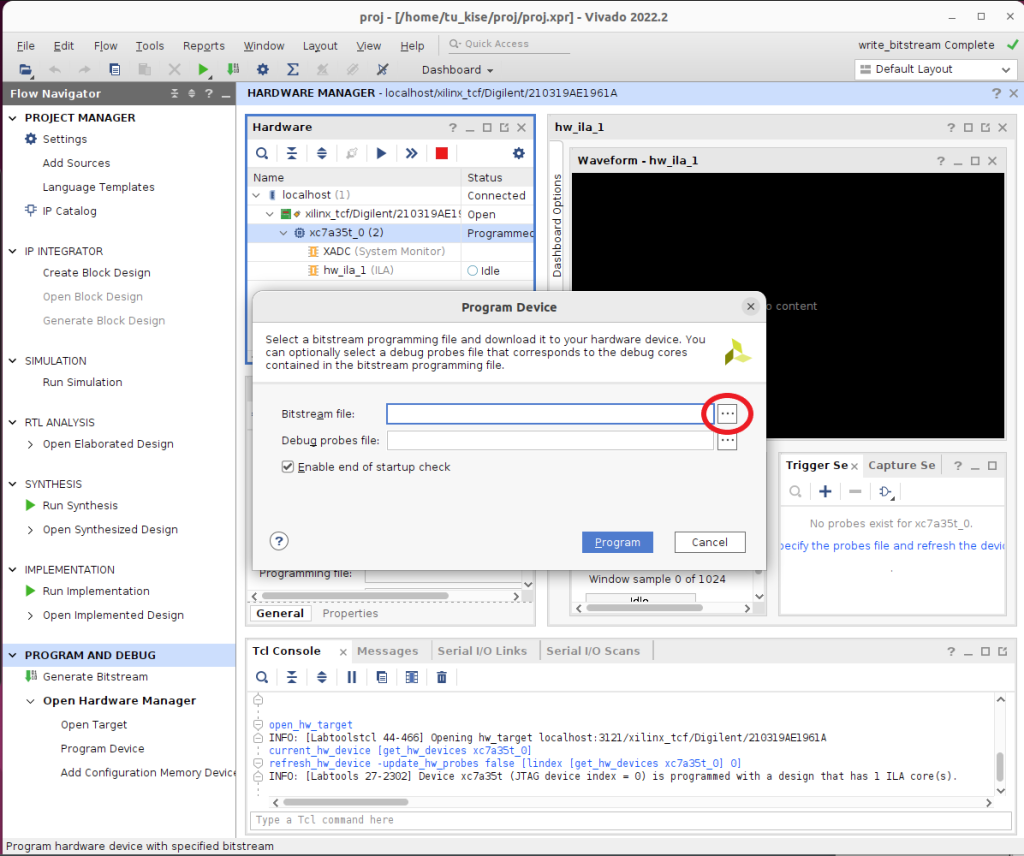

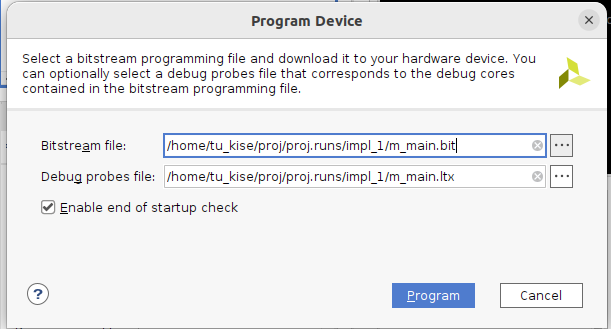

(25) 次の図の Program Device のウィンドウが表示されるので、赤色でハイライトした、Bitstream file: の右の … をクリックして、Specify Bitstream File のウィンドウを開きます。

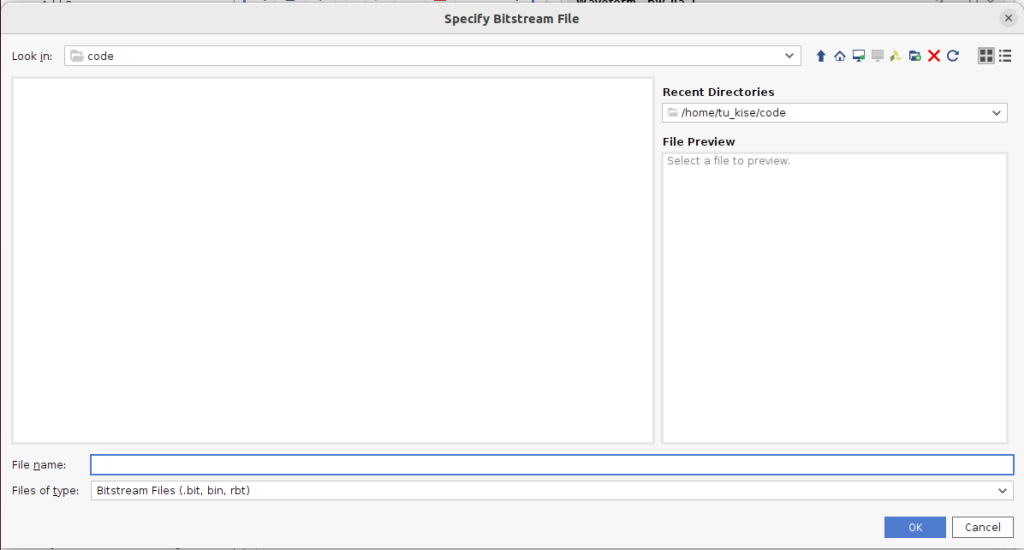

次の図は、表示される Specify Bitstream File のウィンドウです。

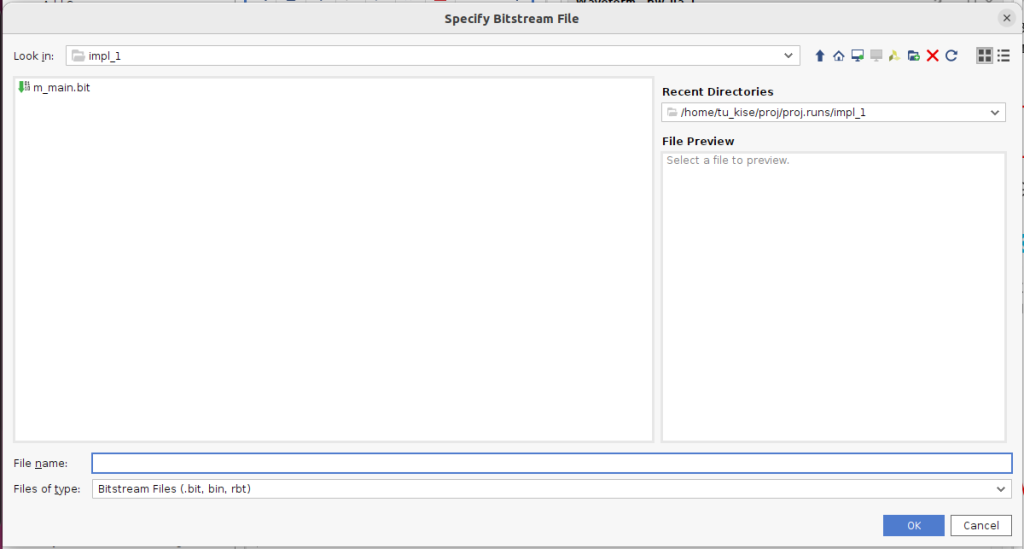

(26) Specify Bitstream File のウィンドウで、指定したフォルダのなかの、プロジェクト名.runs というフォルダ(プロジェクト名を proj とした場合には、proj.runs というフォルダ)のなかの、impl_1 というフォルダのなかの m_main.bit というファイルを選択して、青色の OK をクリックします。ここは難しいかもしれません、次の図のように、なんとか、m_main.bitというファイルを見つけましょう。

(27) 次の図のように、Program Device のウィンドウの Bitstream File: と Debug probes files: にファイル名が記入されます。青色の Program をクリックします。

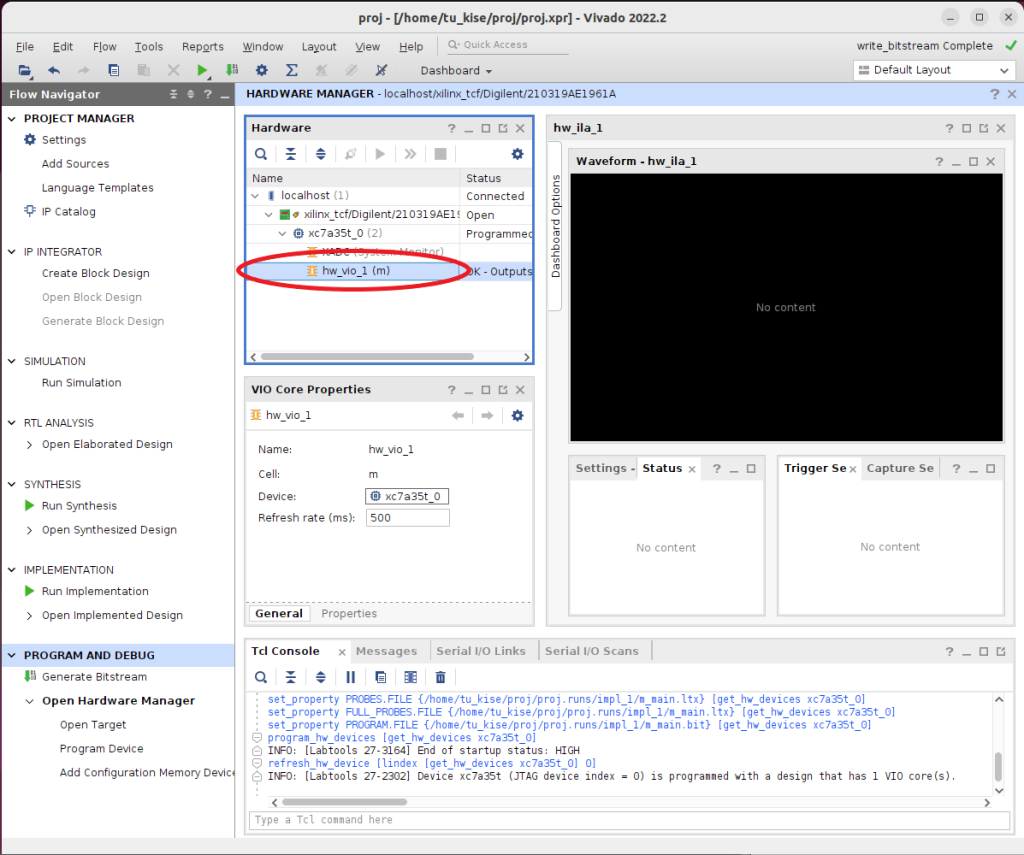

(28) コンフィギュレーションが始まり、数秒後に、コンフィギュレーションが終了します。また、FPGA が動き始めます。

(29) FPGA が動き出したので、FPGA ボードの LED のひとつが点灯しているはずです。ACRi ルームで利用している場合には、この動作をみることはできません。手元の FPGA ボードを利用している場合には、FPGA ボードの LED を確認しましょう。

VIO を用いて FPGA の動作を確認する

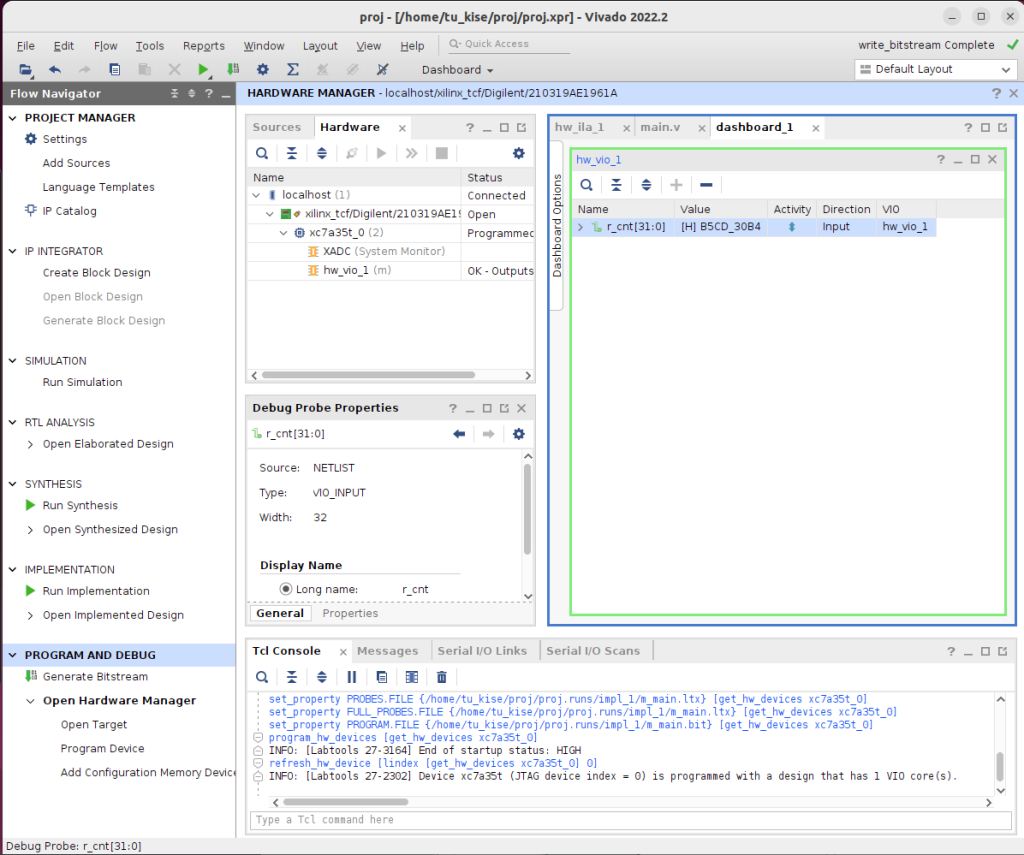

(30) 次の図の赤色でハイライトする Hardware ウィンドウの hw_vio_1 (m) をダブルクリックします。

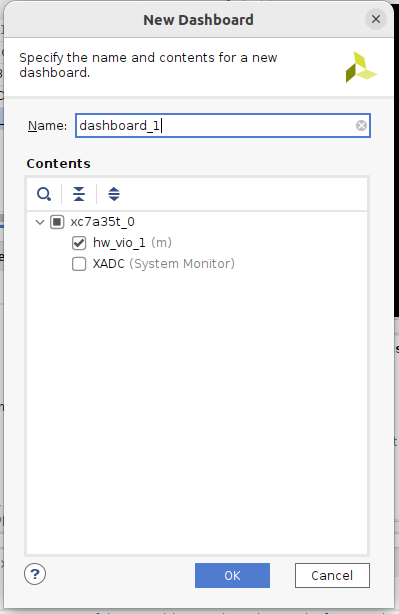

次の図の New Dashboard ウィンドウが表示されるので、青色の OK をクリックします。

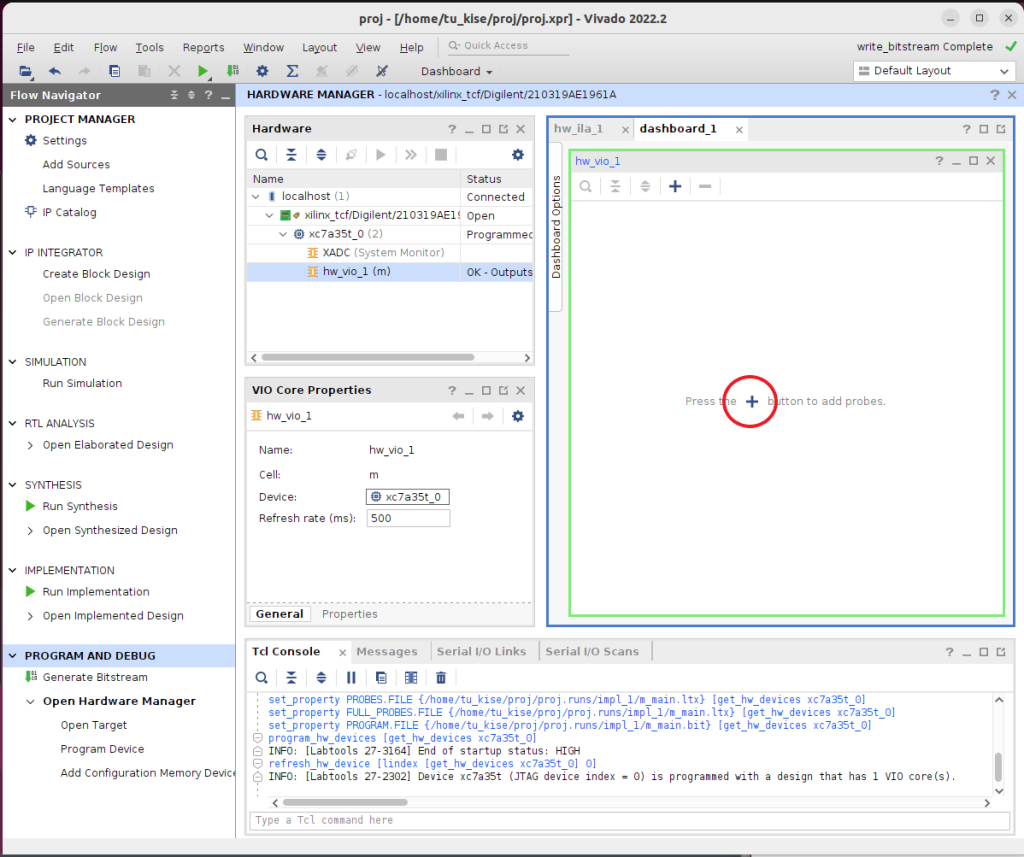

次の図のように、hw_vio1 のウィンドウが表示されるので、赤色でハイライトした + をクリックします。

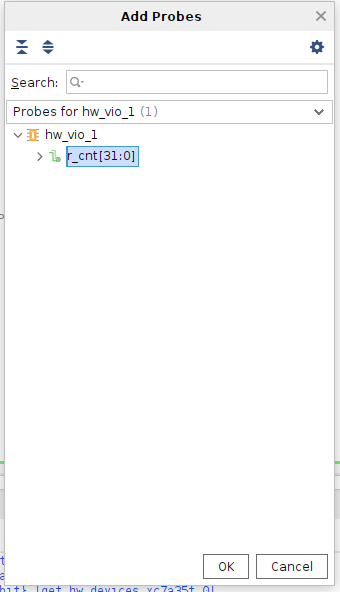

(31) 次の図のように、表示される Add Probes のウィンドウで、r_cnt[31:0] を選択して、白色の OK をクリックします。

(32) 次の図のように、dashboard_1 の hw_vio_1 に表示される r_cnt[31:0] の値が時間とともに増えていく様子を確認できます。

これで、設計したハードウェアを FPGA で動作させて、その動作の様子を確認することができました。

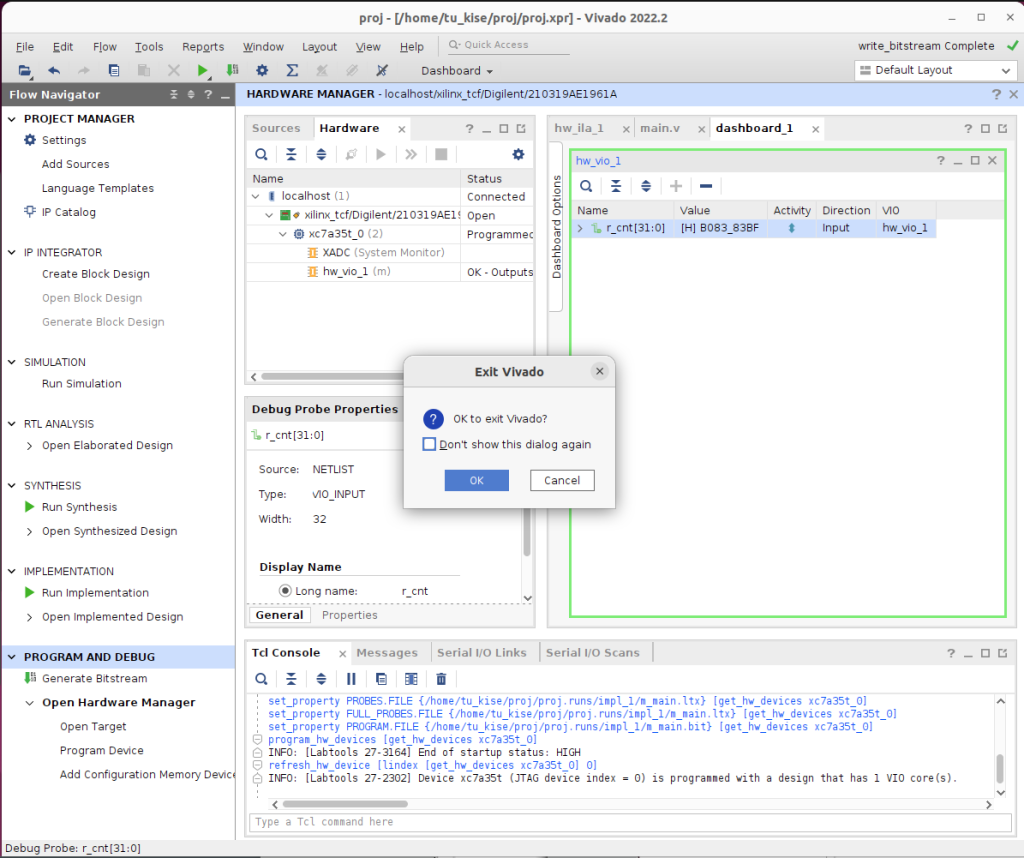

Vivado の画面の右上の × をクリックすると、Exit Vivado ウィンドウが表示されます。青色の OK をクリックして、Vivado を終了させます。

まとめ

この記事では、ACRi ルームのコンピュータと FPGA を利用して、簡単なカウンタ回路を動作させて、その挙動を確認する方法を説明しました。

Verilog HDL で記述したハードウェアの内容や、論理合成、配置・配線といった処理の詳細は後回しにして、Vivado を活用して、FPGA を動かすこと、動かした FPGA の動作を確認することを目標にしました。

次のステップとして、ここで利用した Verilog HDL のファイル main.v を少し修正して、この記事を参考に FPGA で動作させて、その挙動を確認してみましょう。

東工大 吉瀬謙二