みなさんこんにちは。本シリーズ「 FPGA で作る暗号は危険 ? 」では、FPGA で暗号機能を実現する方法とその危険性を解説しています。

前回は共通鍵暗号として最も使用されている AES 暗号について、その動作と FPGA に実装する方法を解説しました。AES 暗号はデータの置換と排他的論理和 (XOR) のみで実現することができるので、処理を把握すれば FPGA 内に機能を実装することは比較的簡単です。

しかし、安易に FPGA に暗号機能を実装してしまうと「サイドチャネル攻撃」と呼ばれる攻撃に対して弱くなり、非常に危険です。 今回は、AES 暗号に対するサイドチャネル攻撃について解説します。

本来であれば、攻撃の危険性と共に対策について解説するところですが、対策については余り詳しく触れません。現在も対策を研究中であり、発表していない内容などには触れることができないため、その点はご了承下さい。

暗号への攻撃

暗号の安全を確保するために漏洩してはいけないのが暗号に使用する鍵です。攻撃者はどうにかして鍵を手に入れようと様々な手法を繰り出してきます。

夜中にオフィスへ侵入し、パソコンの中に保存された鍵を盗むという方法もありますが、暗号に対する攻撃は物理的に鍵を盗むのとは異なり、手に入る情報を元に鍵を見つけ出すことです。

ブルート・フォース攻撃

最も単純な攻撃方法は全ての鍵を試すことであり、この総当たり攻撃は「ブルート・フォース攻撃」と呼ばれています。自転車やスーツケースに使われている4桁の鍵だと 0000~9999 の1万通りなので、1秒に1回試すことができれば1万秒 = 約 2.7 時間で全ての鍵を試すことができます。

しかし、AES 暗号の鍵は128ビット以上です。つまり、2128 通りの組み合わせが存在することになり、1GHz クロックで1クロックあたり一つのパターンを試せるとしても、2128/109 秒 ( 約 1022 年 ) 掛かり現実的ではありません。AES 暗号が安全とされる根拠は、このように現実的な時間でブルート・フォース攻撃ができないことです。

サイドチャネル攻撃

ブルート・フォース攻撃やアルゴリズムの脆弱な部分を使用する攻撃のように暗号化されたデータ (メインチャネル) を元に行う攻撃に対して、漏れ出す (サイドチャネル) 情報を使用した攻撃がサイドチャネル攻撃と呼ばれています。

サイドチャネル攻撃には使用するサイドチャネル情報によってさまざまな攻撃があります。2018年1月にサイドチャネル攻撃に対する脆弱性があることが判明して世間を賑わせた Spectre や Meltdown を覚えている方も多いかもしれません。これらの攻撃は、CPU が投機的実行やアウトオブオーダ処理した後に残っているキャッシュ内の情報を使う攻撃です。つまり、この場合のサイドチャネル情報はキャッシュ内に残った情報です。

ここで紹介する攻撃で使用するサイドチャネル情報はノイズであり、暗号処理の実行中に発生する消費電力の変化を測定して鍵を特定しようとする攻撃です。消費電流の変化は電源に重畳するノイズや電磁界ノイズとして現れるため、オシロスコープや近磁界プローブを使って測定することができます。

ノイズ対策で大丈夫 ?

ノイズを使用するサイドチャネル攻撃の場合、暗号化 / 復号を実行するボードを直接観測する必要があります。つまり、暗号化されたデータを用いる攻撃などと異なり、攻撃者の目の前にボードがあること (攻撃者がボードを入手できること) が攻撃の前提になります。

電源に乗るノイズを観測する攻撃と聞くと、ハードウェアの技術者であれば「ちゃんとバイパスコンデンサを入れて、何ならフィルタを追加しておけば、そんなにノイズなんか出ないだろ」と思われるかもしれません。しかし、ノイズを測定することによるサイドチャネル攻撃では攻撃者の手元にボードがあることが前提であるため、攻撃者はバイパスコンデンサなどのノイズ対策品を取り外すことでハードウェアによる対策を無効にできてしまいます。

以前は、FPGA を搭載したボードは産業用であることが多く、攻撃者がボードを入手して攻撃することは余り想定されていませんでした。しかし、家電製品や自動車など民生品にも FPGA を使用するケースが増え、攻撃対象のボードを攻撃者が入手できるケースが出てきました。また、IoT のエッジコンピューティングが増えていくに従って、FPGA を搭載したボードがユーザ (= 攻撃者) の近くに置かれる場合も多いため、サイドチャネル攻撃が現実味を帯びてきました。

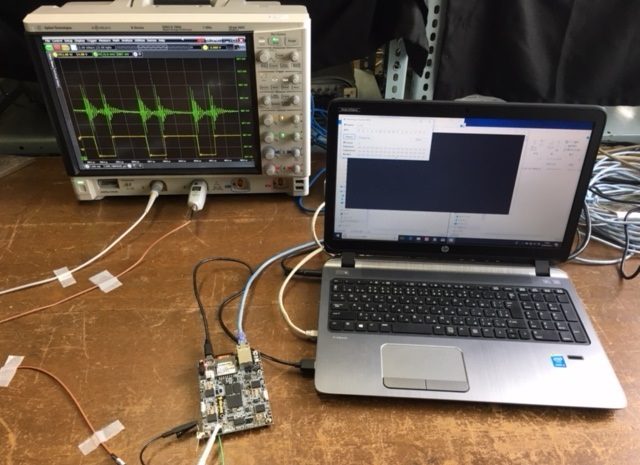

手前味噌になりますが、写真のボードはサイドチャネル攻撃の研究に使用できるように電源観測ポート (黄色で囲んだ SMA コネクタは FPGA のコア電圧に接続) を設けたゴフェルテック社製の FPGA 搭載ボードです。

このボードを使用してサイドチャネル攻撃を行う場合、FPGA コア電源のバイパスコンデンサを全て取り外して暗号動作中の電源を測定します。FPGA の電源にバイパスコンデンサが無い状態で動作させることは余りないと思いますが、バイパスコンデンサが無くても正常に動作し、暗号動作中の電源波形を取得することができます。

このボードには研究用として SMA コネクタを電源観測用に設けていますが、こういったコネクタが無くても取り外したバイパスコンデンサのパッドで電源を測定することでサイドチャネル攻撃は可能です。

AES 暗号に対するサイドチャネル攻撃

ノイズを元に鍵を見つけ出すサイドチャネル攻撃といっても、ターゲットとする暗号によって方法が異なります。今回は共通鍵暗号の AES 暗号に対する攻撃を紹介します。公開鍵暗号のサイドチャネル攻撃については次回以降で触れていく予定です。

ノイズとハミング距離

ノイズを観測することによって、どんな情報が得られるかを考えてみます。

IC 内部のゲート出力には配線や接続先ゲートといった容量成分が接続されています。そのため、出力が Low から High に変化すると容量成分への充電電流が流れ、逆に High から Low に変化すると放電電流が流れます。つまり、データが遷移すると電流が流れて消費電流が変化し、その変化がノイズとして現れます。遷移するデータの数によって消費電流の変化量も変わるため、遷移するデータ数と消費電流の変化には関連があります。

遷移するデータの数はハミング距離 (Hamming Distance, HD) と呼ばれ、例えば、0x12 (0b00010010) が 0xFE (0b11111110) に変化する場合のハミング距離は5です。

スイッチング電流はハミング距離が大きいほど大きくなる関係にあるため、電源の変動 (ノイズ) を観測することでハミング距離を推測することができます。

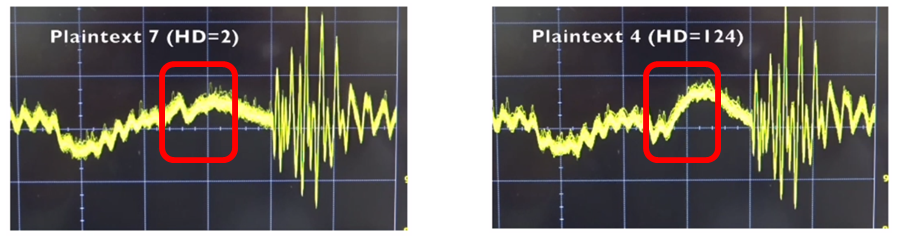

上の図は AES 暗号化中の FPGA コア電源を測定した波形ですが、HD=2 の場合に比べ、HD=124 では電圧が低下 (電流が増加) していることが分かると思います。AES 暗号に対するサイドチャネル攻撃は、このハミング距離によるノイズの違いを利用して鍵を特定していきます。

選択平文攻撃

暗号に対する攻撃を行う際、鍵が分からない状態で攻撃しますが、攻撃のネタとして何が使えるかによって攻撃方法が分類されています。今回紹介する AES 暗号に対するサイドチャネル攻撃は「選択平文攻撃」と呼ばれる攻撃方法です。

選択平文攻撃とは、任意の平文に対する暗号文を攻撃者が手に入れることができる前提で行う攻撃です。他の攻撃には、暗号文のみしか入手できない状態で行う暗号文単独攻撃や任意の暗号文に対して平文を手に入れることができる選択暗号文攻撃があります。

AES 暗号に対するサイドチャネル攻撃の場合、暗号化動作中に発生するノイズを使用するため暗号文自体は使いませんが、任意の平文を設定して暗号化機能を動作させることができる環境が必要です。

パワーモデル

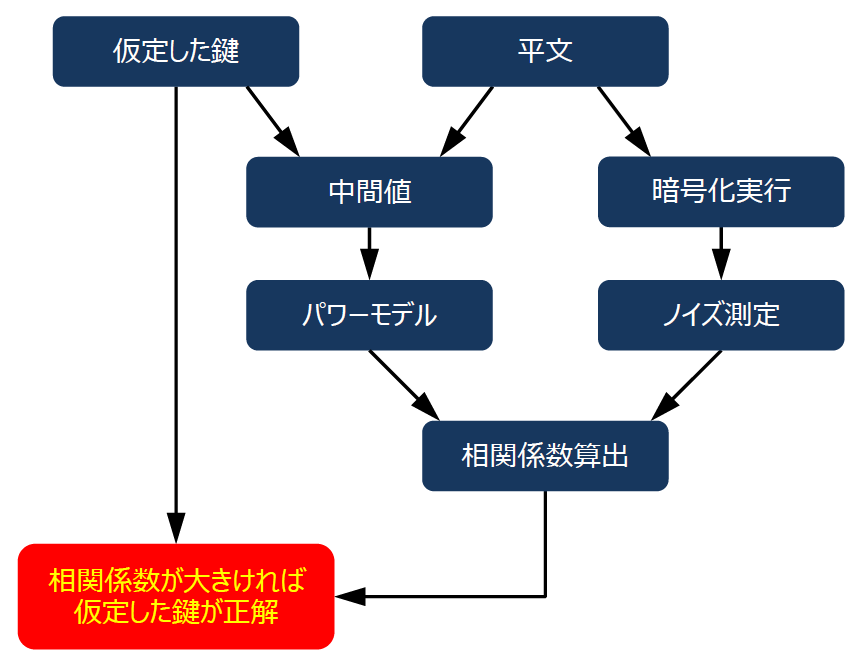

AES 暗号に対するサイドチャネル攻撃はデータの遷移量 (ハミング距離) に応じて変化するノイズを観測して鍵を特定します。具体的には、鍵を仮定して暗号化動作中 ( 中間値 ) のハミング距離を算出し、算出したハミング距離と測定したノイズに相関があれば、「仮定した鍵は正解」であったと判断します。測定したノイズ波形と比較するために作成する仮定した鍵のハミング距離から算出した波形モデルをパワーモデルと呼びます。

攻撃対象が FPGA の場合、スイッチング電流の変化を狙うためハミング距離を用いたパワーモデルを使用します。それに対して、攻撃対象がマイコンや CPU の場合は IC 内部のデータバスで発生する消費電流変化の方がノイズとして漏れ出し易いことがあり、この場合はハミング重み (データ中にある1の数) を元に算出したパワーモデル使用します。

攻撃方法

選択平文攻撃ができる環境 (= 任意の平文を暗号化できる環境) が手に入り、パワーモデルの算出ができれば、サイドチャネル攻撃の準備が整ったことになります。

この写真は実際にサイドチャネル攻撃としてノイズを観測している様子です。パソコンから平文を設定して暗号化を行い、FPGA コア電源に発生するノイズをオシロスコープで観測しています。

平文を変えながらノイズを測定し、「得られたノイズ波形」と「鍵を仮定して算出したパワーモデル」を比較して鍵を特定していきます。測定波形とパワーモデルの比較は相関係数を算出して評価します。算出された相関係数が高いほど測定波形とパワーモデルの関連性が高いことを示します。

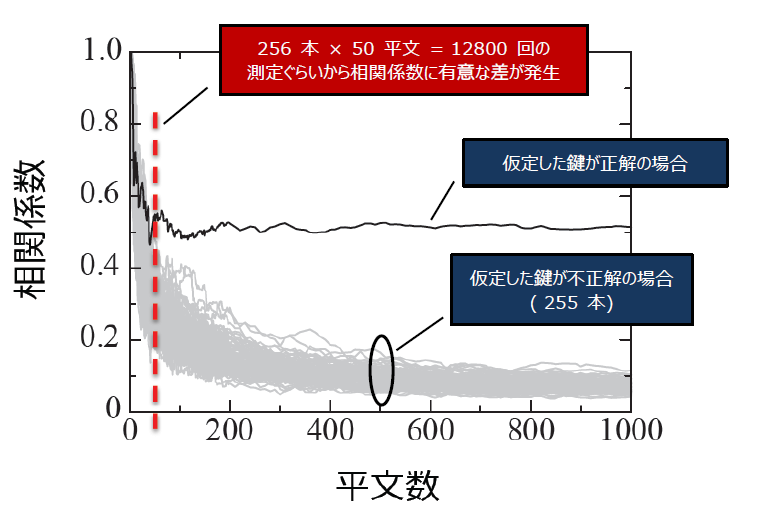

上のグラフは測定する平文の数と算出された相関係数の関係を示したものです。測定する平文の数が増えていくと、明らかに他とは異なる相関係数を持つモデルが現れています。この相関係数が高いモデルの作成に使用した鍵が暗号化に使用されている鍵であり、暗号鍵を特定することができます。

サイドチャネル攻撃の脅威

ここまでの解説で、「で、なんでサイドチャネル攻撃が怖いの ? 」と思われている方もいらっしゃると思います。

サイドチャネルの攻撃フローを見ると、鍵を仮定したパワーモデルと測定値の比較を繰り返しているので、試行する回数はブルート・フォース攻撃と同じではないかと思えます。

つまり、鍵の候補は 2128 個あるわけですから、全ての候補についてパワーモデルを作成して測定するにはブルート・フォース攻撃よりも長い時間が必要なので現実的には不可能な攻撃と考えることができそうです。

しかし、AES 暗号に対して行うサイドチャネル攻撃はブルート・フォース攻撃よりもはるかに短い時間で行うことができます。というのも、実はサイドチャネル攻撃には、ブルート・フォース攻撃のように全ての鍵候補を試す必要がないからです。

前回解説したように、AES 暗号はデータの入れ替えと XOR のみで構成できるため、鍵の違いによって変化するハミング距離は一定の範囲に限定されます。

具体的に言えば、1 バイト毎に鍵を試すことが可能であり、128 ビットある鍵の中で特定の 1 バイトに狙いを定めて攻撃を行うことができます。バイト単位で鍵を試すことができるということは、1 バイト = 256 通りを試すと狙ったバイト部分の鍵を特定できるということです。

上で紹介した相関係数のグラフで相関係数が小さい波形が複数ありましたが、実はこの波形数は256から正解を除いた255本です。

バイト単位で鍵を試すことができることから、128 ビット = 16 バイトの鍵全てを特定するまでに必要な観測波形の数は以下になります。

[ 鍵特定に必要な測定波形数 = 16 バイト × 256 = 4,096 波形 ]

但し、サイドチャネル情報としてノイズに漏れ出す鍵情報が小さい場合には相関係数に有意な差が出てくるまで平文を変えながらノイズを観測する必要があり、上のグラフでは一つの鍵候補あたり約50パターンの平文を測定したぐらいから相関係数に有意な差が見られ始めています。この場合に必要な波形測定数は 256 × 50 = 12,800 であり、鍵全体 (16バイト) でも 12,800 × 16 = 204,800 です。

測定を自動で行えば、一つの波形を取得するために必要な時間は数十 ms 程度ですが、仮に1秒掛かるとしても56時間程度で必要な数の波形を取得することできます。

但し、図の測定に使用した暗号機能は攻撃がやり易い実装にしているため、通常の実装であれば 50 パターン程度で有意な差は発生せず、数千以上のパターンが必要です。

いずれにしても、この時間はブルート・フォースト攻撃と比較して劇的に少なく、これがサイドチャネル攻撃が脅威となる理由です。

対策

サイドチャネル情報がノイズとして漏れ出さないような対策が施された AES 暗号機能にサイドチャネル攻撃を行った場合、測定する平文の数をいくら多くしても相関係数に有意な差が認められるモデルが現れてきません。

ここでは、サイドチャネル情報の漏洩を抑える代表的な対策を紹介します。

2線プリチャージロジック方式

ロジックで発生するノイズを均一化することで漏れ出すサイドチャネル情報を抑える代表的な対策が2線プリチャージロジック方式です。

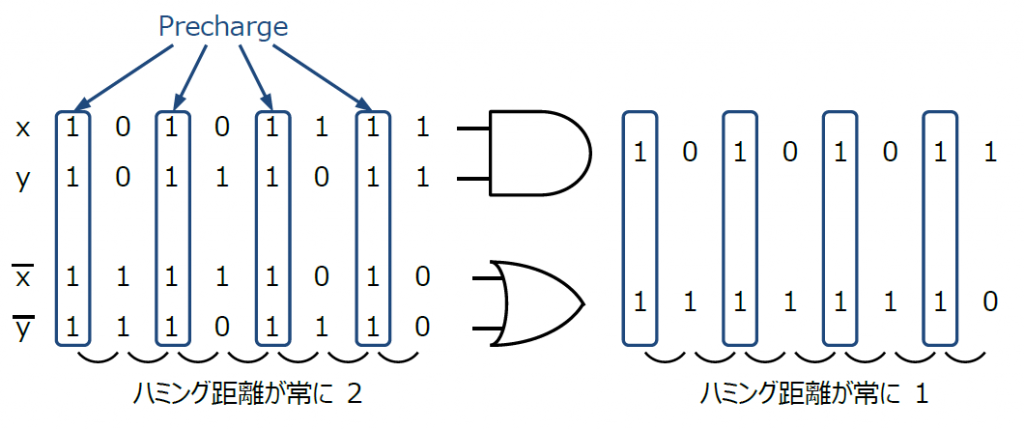

この図は 2 線プリチャージロジック方式による AND 回路の例です。本来のデータは x と y であり、OR は対策として追加されている部分です。

データの間にプリチャージ ( 値を1に設定 ) を挿入すると共に AND 入力の反転値を OR 回路にも入力します。これにより、入出力共にハミング距離が一定になり、ハミング距離の変動によるノイズ発生を抑えることができます。

この対策によって漏れ出すサイドチャネル情報を抑えることはできますが、プリチャージを挿入することによって演算時間が増加し、ロジック回路の追加 (上の例では OR 回路) によって使用するロジック数が増えてしまいます。

FPGA へ適用する場合の問題

2線プリチャージロジック方式を FPGA に適用することも可能ですが、FPGA の場合は難しい問題があります。

発生するノイズの量は IC 内部のゲート出力に接続される容量成分に依存するので、うまく打ち消しあうためには、打ち消す対象になる信号と同じ容量にすることが重要です。また、信号が変化するタイミングも同じにする必要があるために信号の伝搬遅延も同じにする必要があります。

FPGA の配置・配線をツールに任せて行うと、各信号の遅延時間や配線ルートがバラバラになってしまい、うまく打ち消し合うことができません。これを避けるためには、設計者が制約を追加してロジックの配置や配線を決める必要がありますが、ロジックの配置や配線を制約で決めてしまうと、ツールによる最適化が行われません。

また、使用する FPGA のサイズやメーカ等が変わってしまうと制約を書き直す必要があり、大変です。

2線プリチャージロジック方式とは異なり、制約を必要としない対策も研究・開発されていますが、未発表の内容を含むため、残念ながらここでの紹介は控えさせて頂きます。

とはいえ、FPGA 設計者であれば、もっとノイズを出すことで本来の情報を隠すことやタイミングをずらして測定を行えなくする方法など色々と対策が思い当たるのではないかと思います。

まとめ

今回は、共通鍵暗号である AES 暗号に対するサイドチャネル攻撃がどのように行われているかを紹介しました。

次回は公開鍵暗号を FPGA へ実装するときに使う演算について解説する予定です。

株式会社ゴフェルテック 川西紀昭