作成する回路が大きくなってくると、回路を機能毎にモジュール化し、そのモジュール間の接続関係をブロック図で描くと分かりやすくなります。複数のモジュールを1つにまとめた階層構造にすることも可能です。

モジュール化する際のポイントは、その機能の中で後から変更したい機能をパラメータ化して、モジュールの外から入力できるようにすることです。例えば LED の点滅回路では、点滅周期を設定できるようにするなどが考えられます。

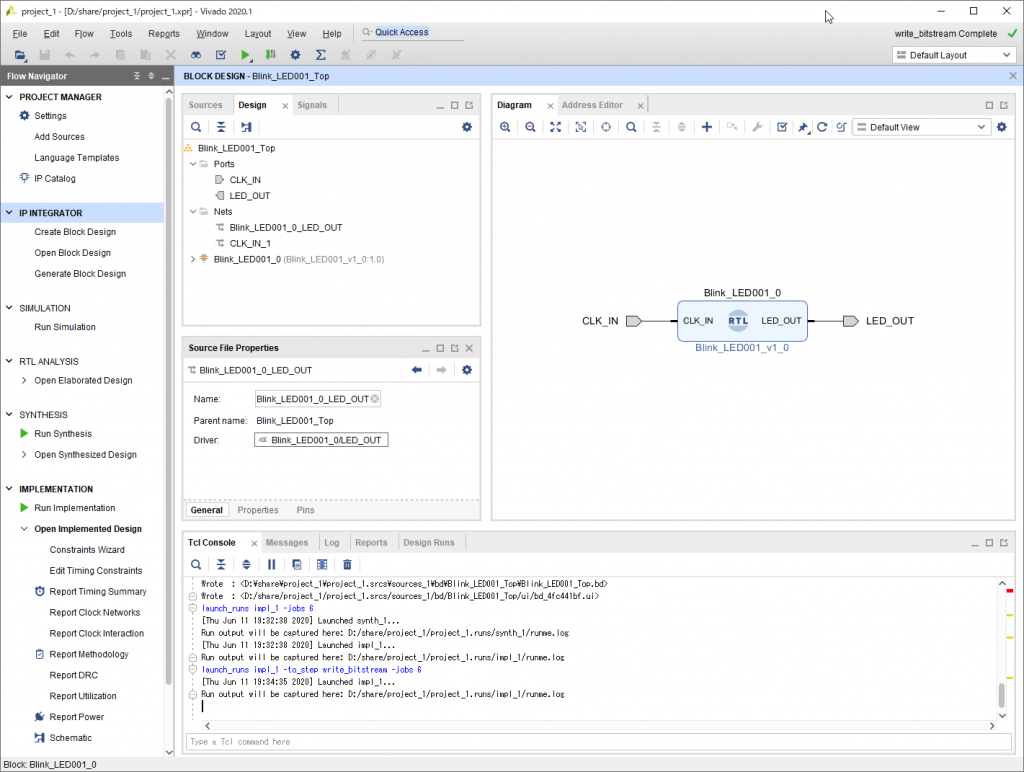

ここでは Vivado のインストールと使いかた (2) で作成した LED の点滅回路をモジュール化してみます。なお Xilinx の Vivado では、このブロック図の作成機能を IP インテグレータと呼んでいます。公式ドキュメントはこちら。

新規プロジェクトと既存のソースコードの追加

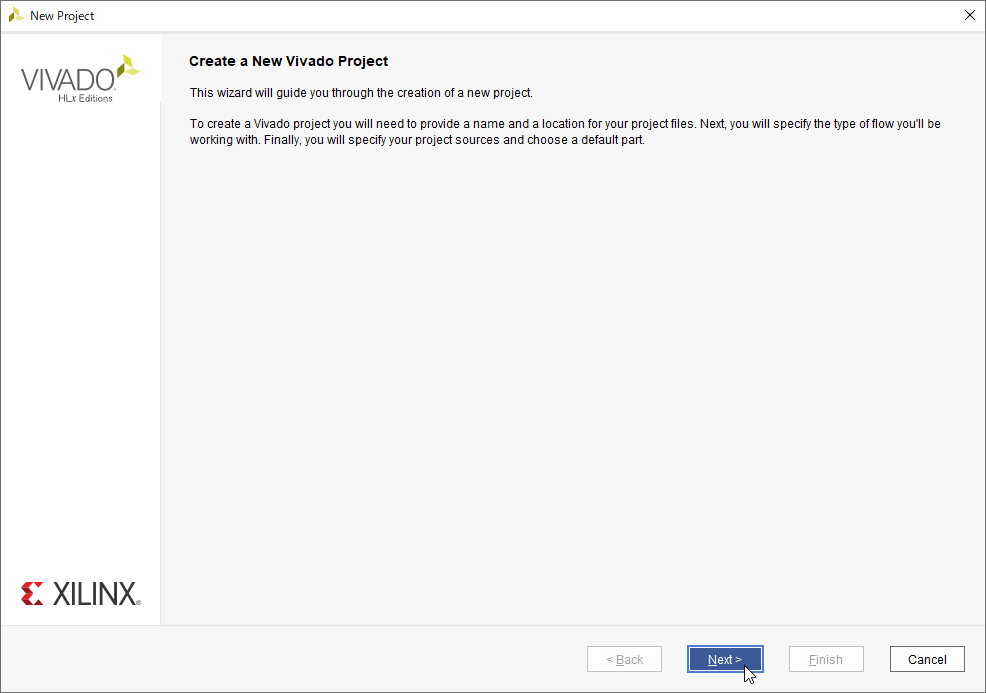

1.Vivado を起動したら、Quick Start の Create Project、もしくは File -> Project -> New からプロジェクトの新規作成を行います。

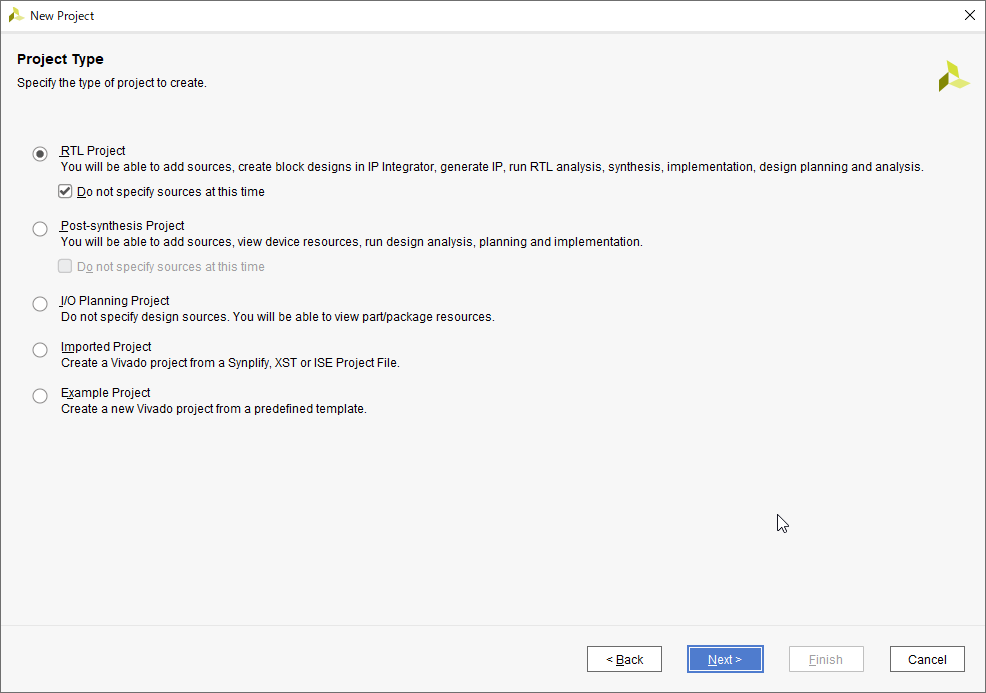

2.プロジェクト名とパスを入力した後、一番上の “RTL Project” を選択し、”Do not specify sources at this time” にチェックを入れて (既に作成した Blink_LED001.vhd を使用するため) 進みます。

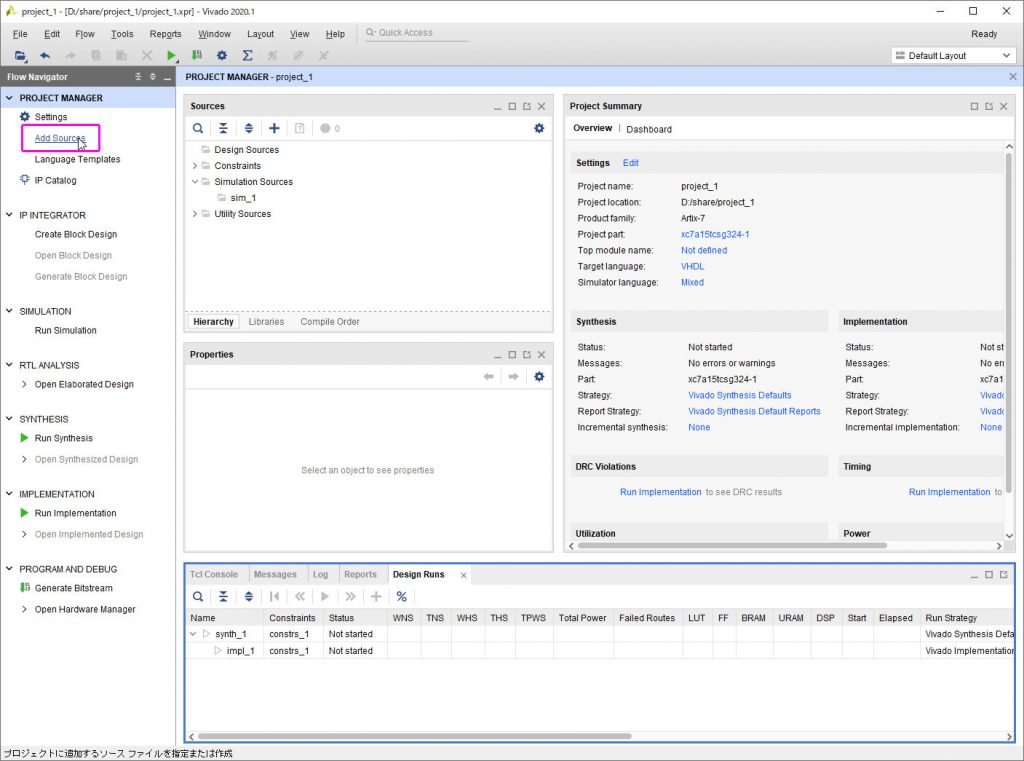

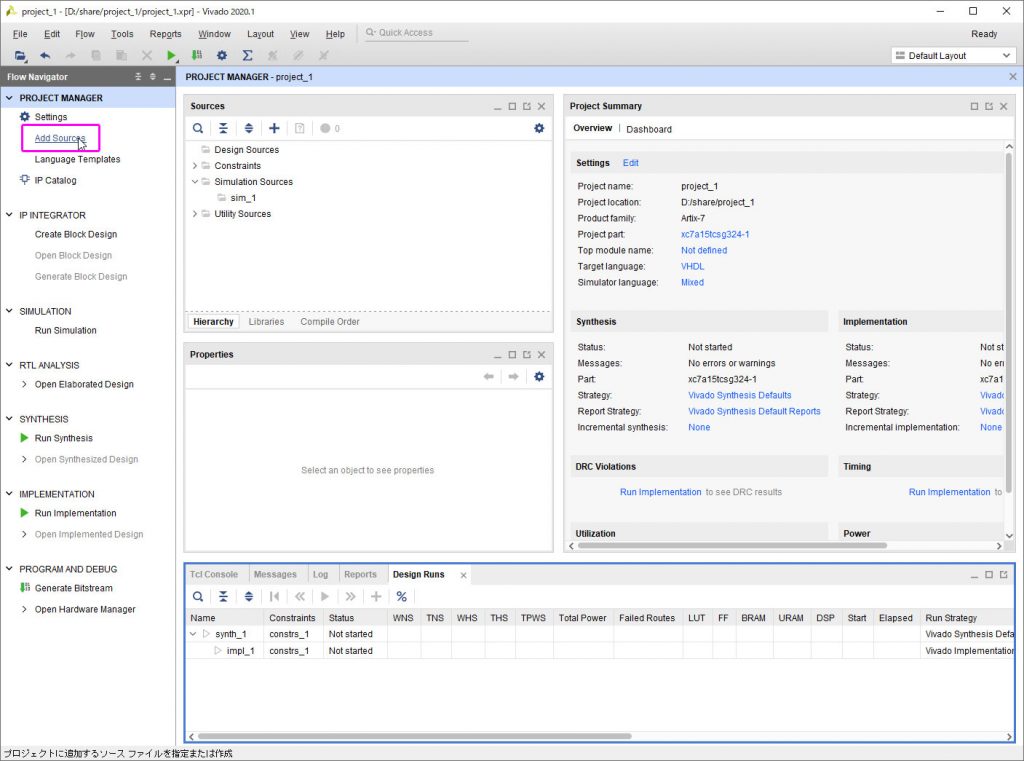

3.使用する FPGA を選択してプロジェクトを作成したら、以前に作成した “Blink_LED001.vhd” をプロジェクトマネージャの “Add Source” より追加します。

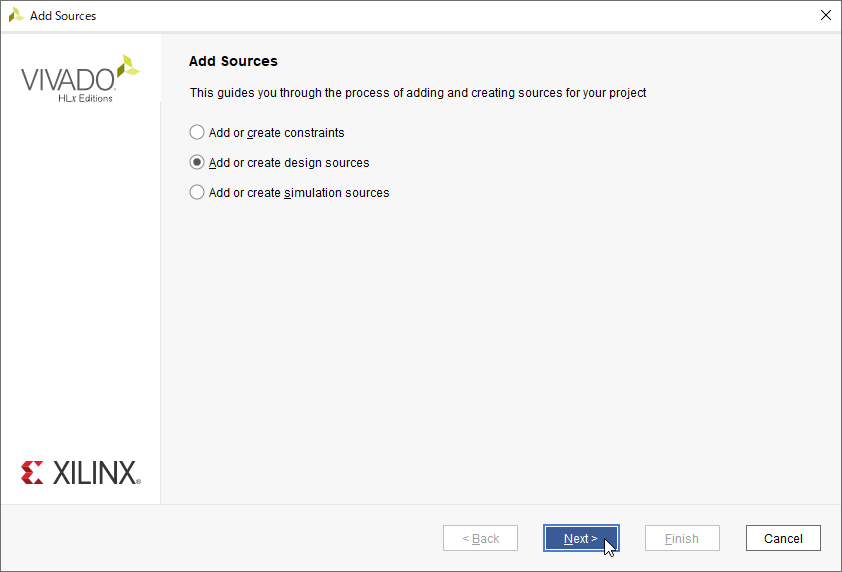

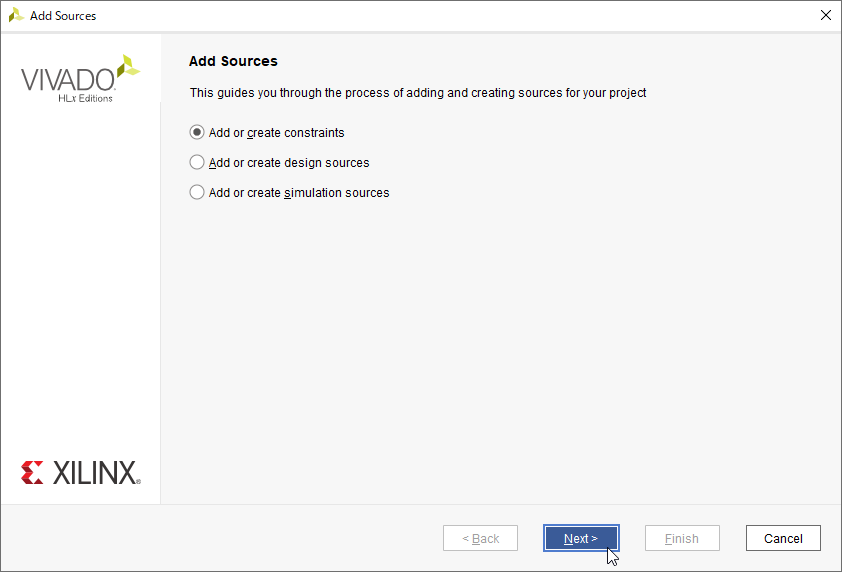

4.2番目の “Add or create design sources” を選択します。

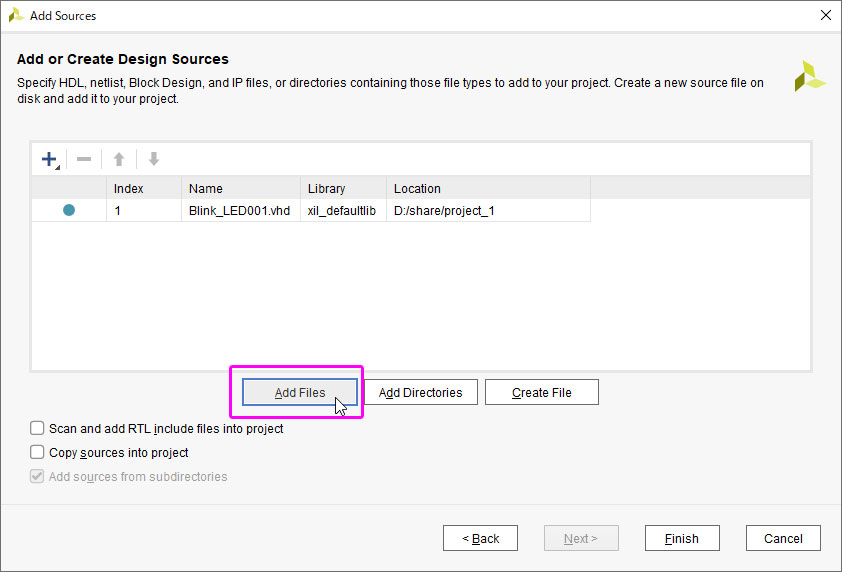

5.”Add Files” をクリックして、該当の VHD Lソース (Blink_LED001.vhd) を選択し、”Finish” をクリックします。

ブロック図の作成

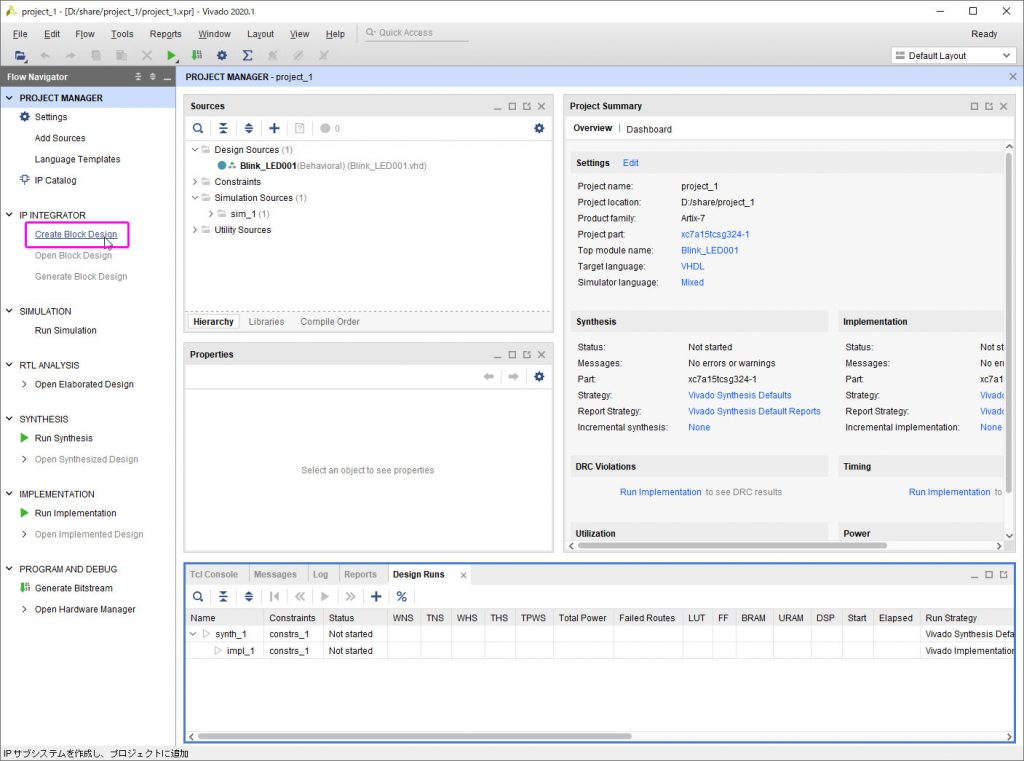

6.次に、プロジェクト・マネージャの “IP INTEGRATOR” にある “Create Block Design” をクリックしてブロック図を作成します。

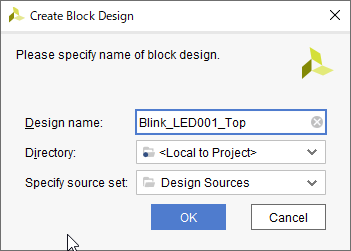

7.ブロック図の名前を入力します。ここでは、”Blink_LED001_Top” としました。

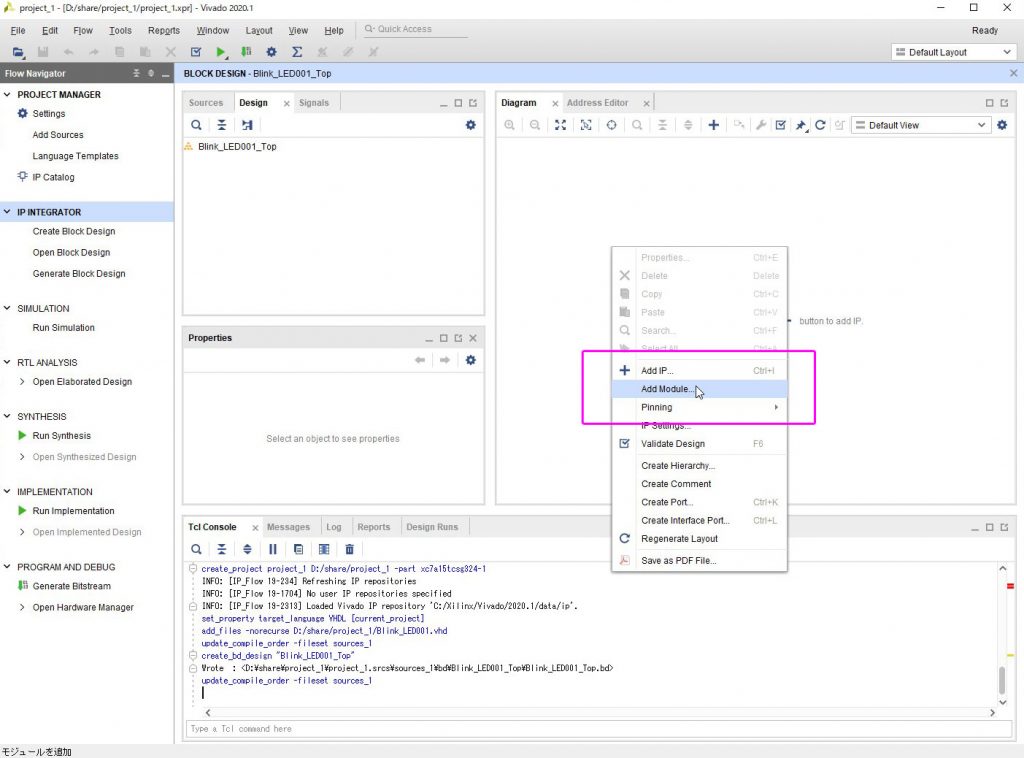

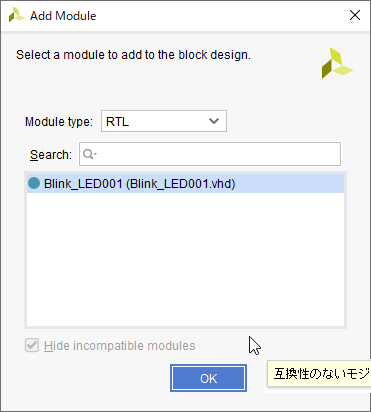

8.空のブロック図ができるので、ブロック図の上で右クリックして、”Add Module” を選択します。

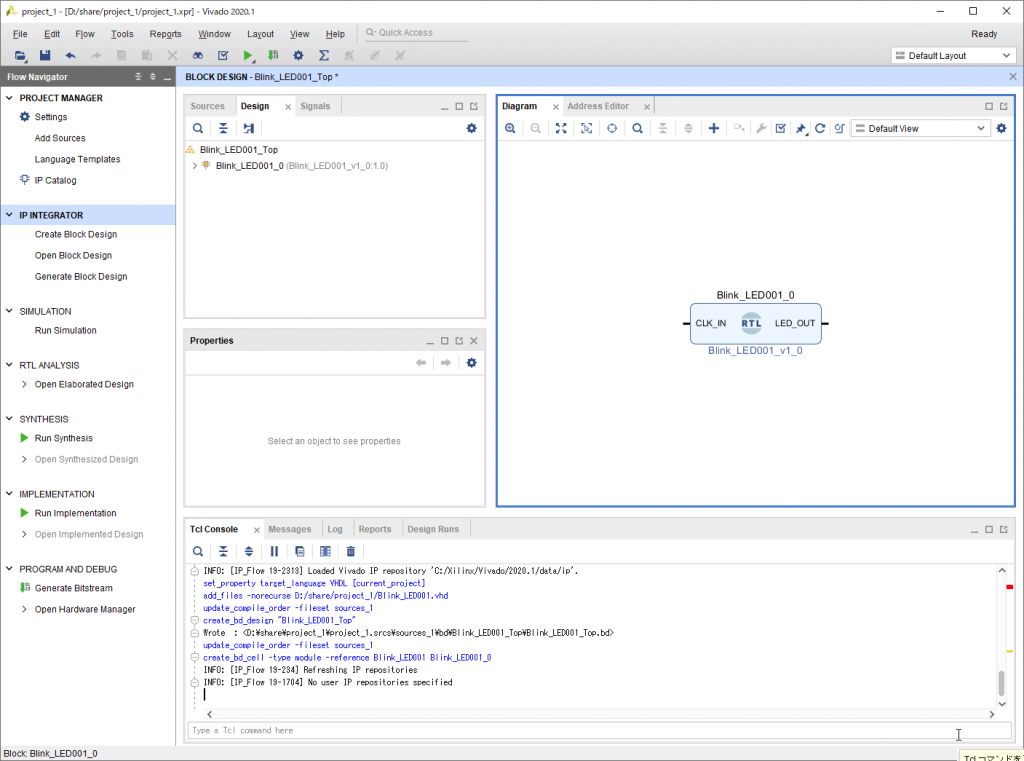

9.先ほど追加した VHDL ファイルを選択します。

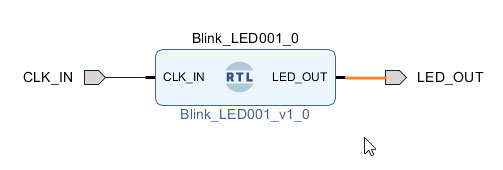

これで、VHDL ファイルのモジュール・シンボルが作成され、ブロック図へ追加されます。

外部ポートの接続

回路のモジュールができたので、これを外部ポートと接続します。

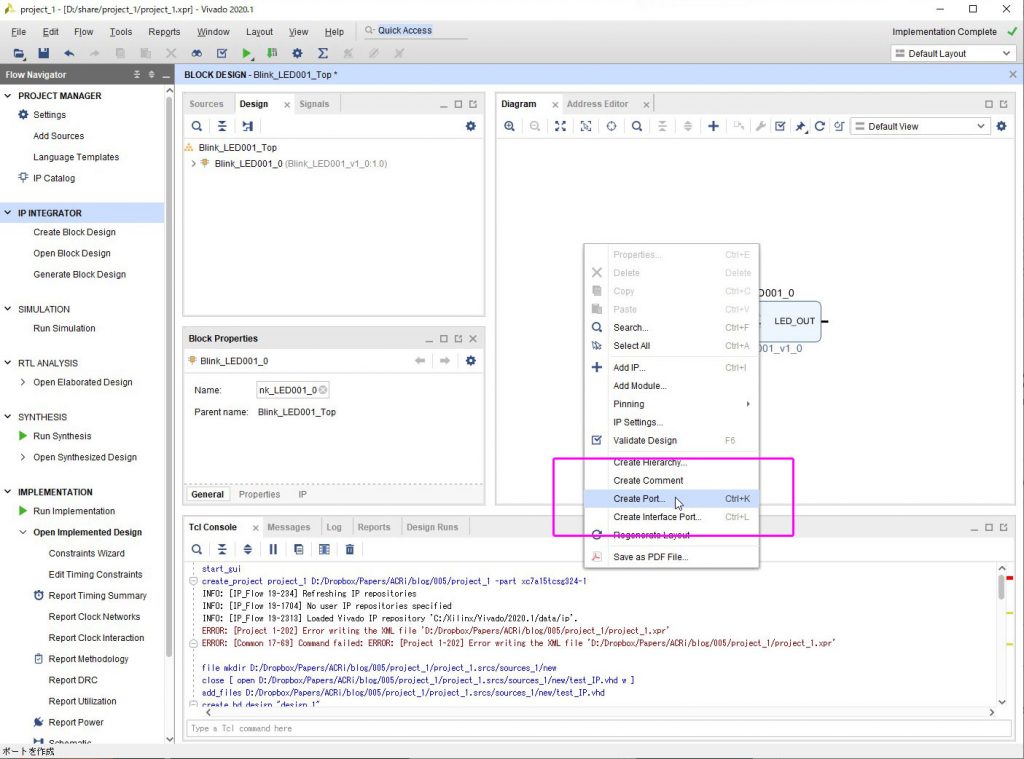

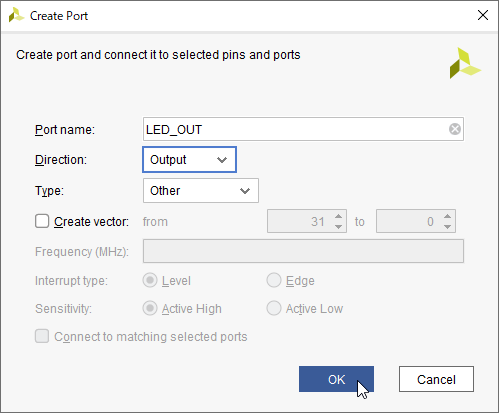

10.再びブロック図の上で右クリックして、”Create Port” を選択します。

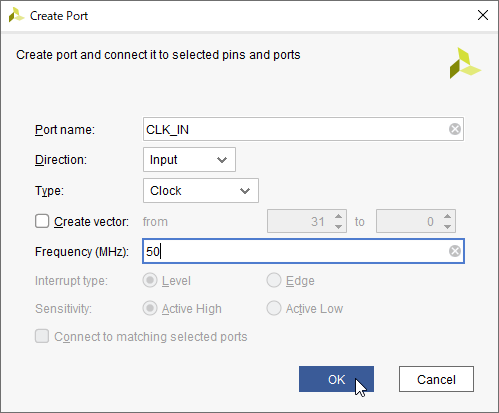

11.まずはクロック入力から作成します。各パラメータを下記のように入力します。クロックの場合は特別に Type: Clock として、動作周波数を入力します。それ以外の一般的な入力の場合は Type: Other とします。

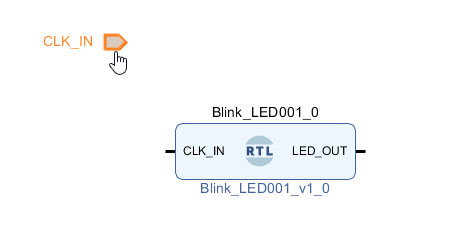

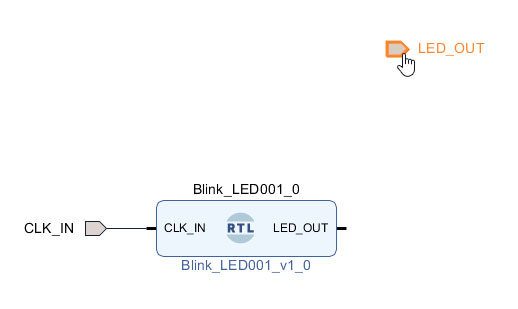

12.ブロック図上にポートのシンボルが作成されるので、これを任意の位置に移動して接続します。マウスカーソルをシンボルに合わせると下図のように指の形になるので、このときにドラッグすることで移動できます。

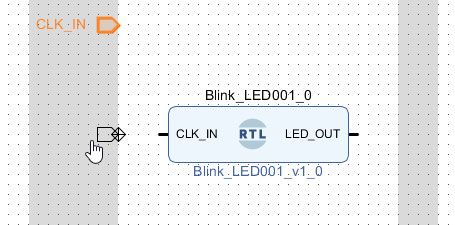

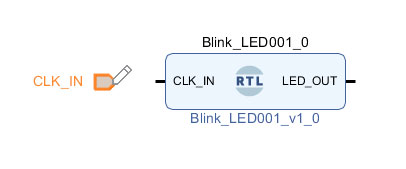

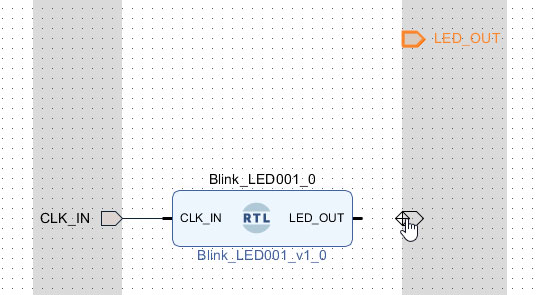

また、マウスカーソルをシンボルの尖った形状の上に持っていくと下図のように鉛筆の形のカーソルになるので、このときにドラッグすることで線を引くことができます。

13.出力側も作成します。出力側のパラメータは下記の通りです。

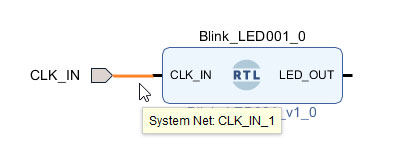

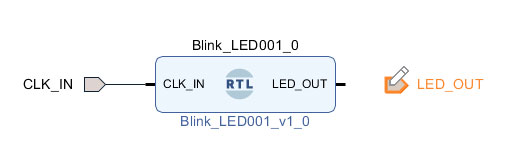

14.入力と同様に出力ポートのシンボルを適切な位置に配置し、配線します。

ブロック図はこれで完成です。

制約ファイルの追加とインプリメンテーション

この状態で論理合成とインプリメンテーションが可能ですが、最後に使用する FPGA ボードに合わせたピンアサインを行う必要があります。これも Vivado のインストールと使いかた (2) で作成したものを追加して使用します。

15.プロジェクト・マネージャの “Add Sources” をクリックします。

16.一番上の “Add or create constraints” を選択します。

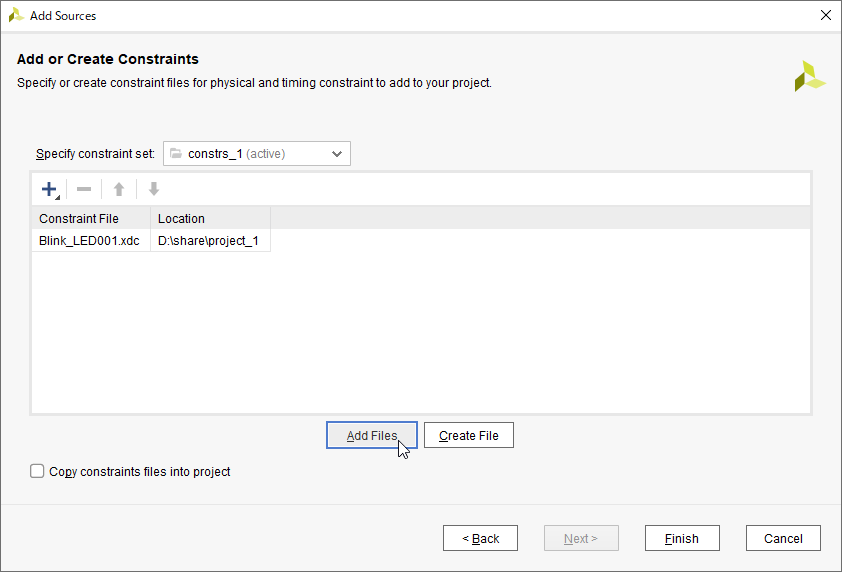

17.”Add Files” にて Blink_LED001.xdc を選択し、Finish をクリックします。

18.後は論理合成、インプリメンテーション、ビットストリーム・ファイルの生成を実行すれば、FPGA へ書き込むことができます。

すすたわり