皆さん、こんにちは。今回は、前回 (FPGA を対象とした非同期式回路の設計 (2)) で準備した回路モデルを Intel の FPGA を対象に合成していきます。前回を読んでいない方は、最初に前回を確認してください。

また、Quartus Prime が必要になりますので、インストールしていない方は Quartus Prime Lite (無償版) を準備してください。

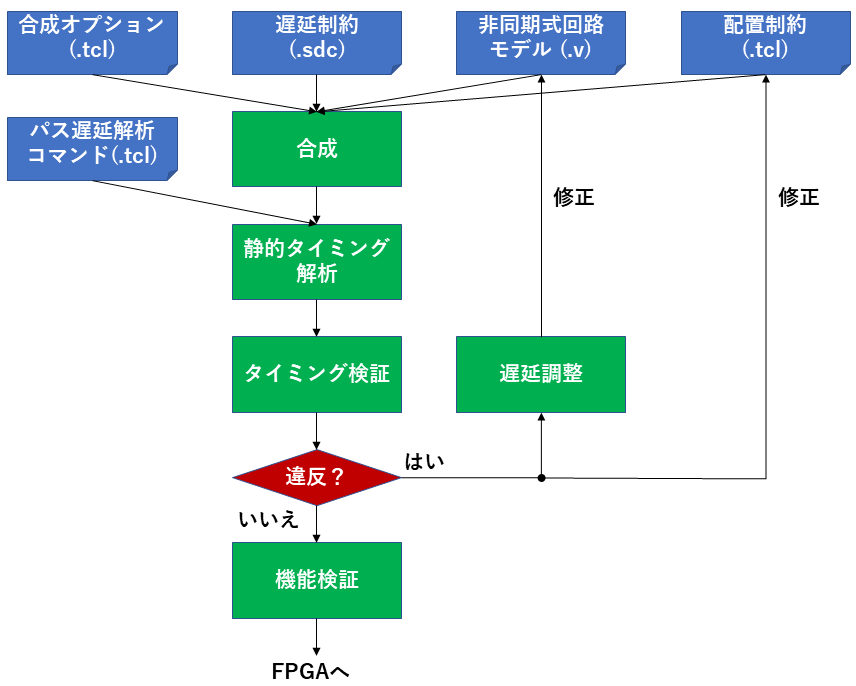

設計フロー

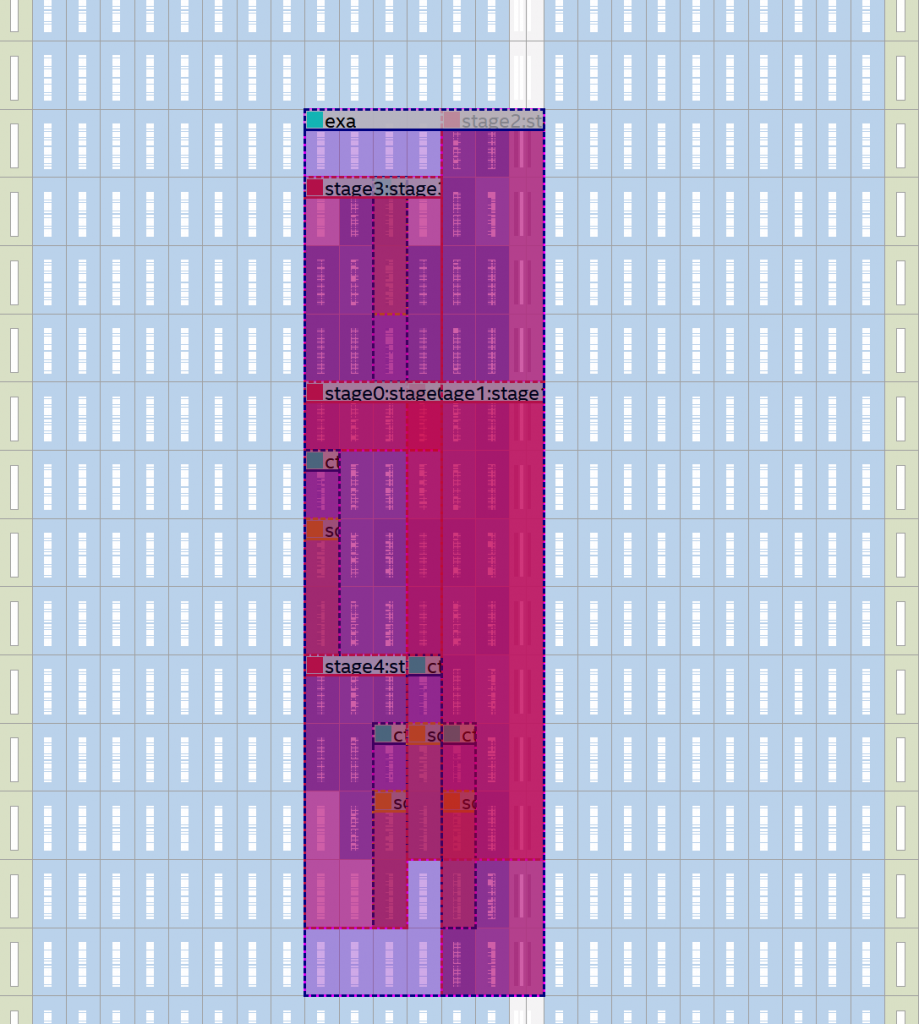

図1は、今回用いる設計フローです。今回は合成に必要となるものと合成までを解説し、タイミング検証と遅延調整は次回解説したいと思います。なお、非同期式回路モデルについては前回をご覧ください。

青色は入力として準備しなければいけないところです。初めに、これらの内容と意義を説明していきます。

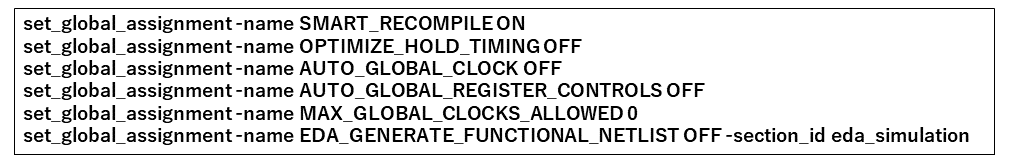

合成オプション

図2は、合成オプションをTCL形式で表したものです。

SMART_RECOMPILE ですが、遅延素子の調整を行った際、再合成が必要になります。その時、再実行の必要ない項目を Quartus Prime が自動で判断し、スキップすることで合成時間を短縮するためのものです。OPTIMIZE_HOLD_TIMING ですが、最小遅延を最適化する機能です。不用意な最適化で遅延調整に影響を及ぼさないために OFF としています。以上は、これまでの経験上つけたものです。一方、次の AUTO_GLOBAL_CLOCK、AUTO_GLOBAL_REGISTER_CONTROLS、MAX_GLOBAL_CLOCKS_ALLOWED は、特に大事でグローバル信号 (クロック信号を含む) を使用しないためのものです。最後の EDA_GENERATE_FUNCTIONAL_NETLIST は、デフォルトのシミュレーションが遅延なしなので、それを OFF にして、遅延情報を含んだタイミングファイルを利用したシミュレーションとしています。これは、合成後のゲートレベルシミュレーションのためです。

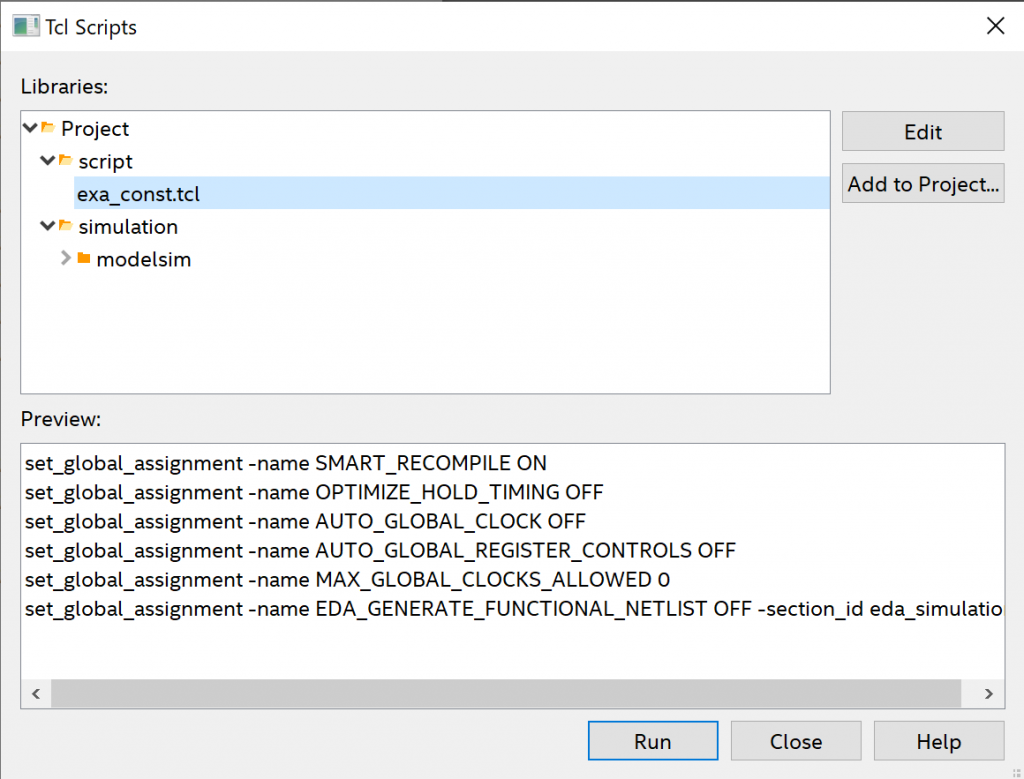

準備した TCL ファイルを Quartus Prime で認識させる方法ですが、一つは、Quartus Prime のメニューから Tools を選び、現れたリストの中で Tcl Scripts を選びます。図3のような画面がでますので、ファイル名を指定して実行すれば反映されます。

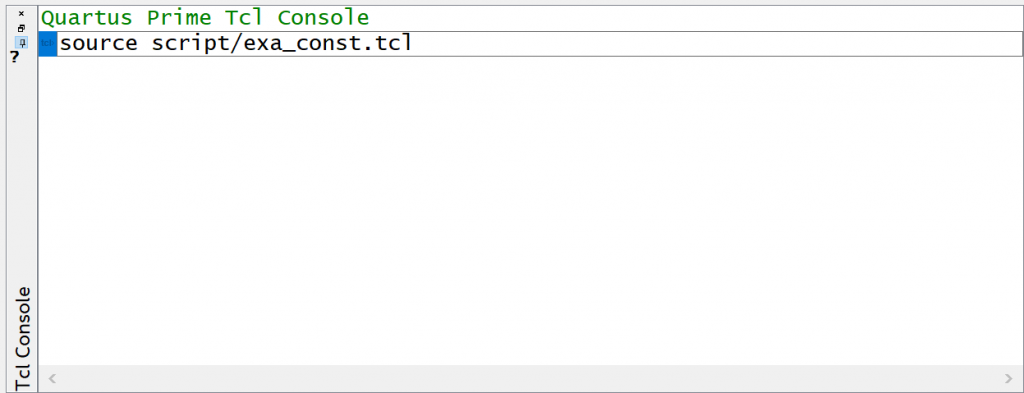

もう一つの方法は、Quartus Prime にある Tcl Console にて source コマンドを使う方法です (図4)。source TCL ファイル名を入力した後、リターンすれば反映されます。Quartus Prime のデフォルト画面に Tcl Console がない場合、メニューの View の中から選択して下さい。

遅延制約

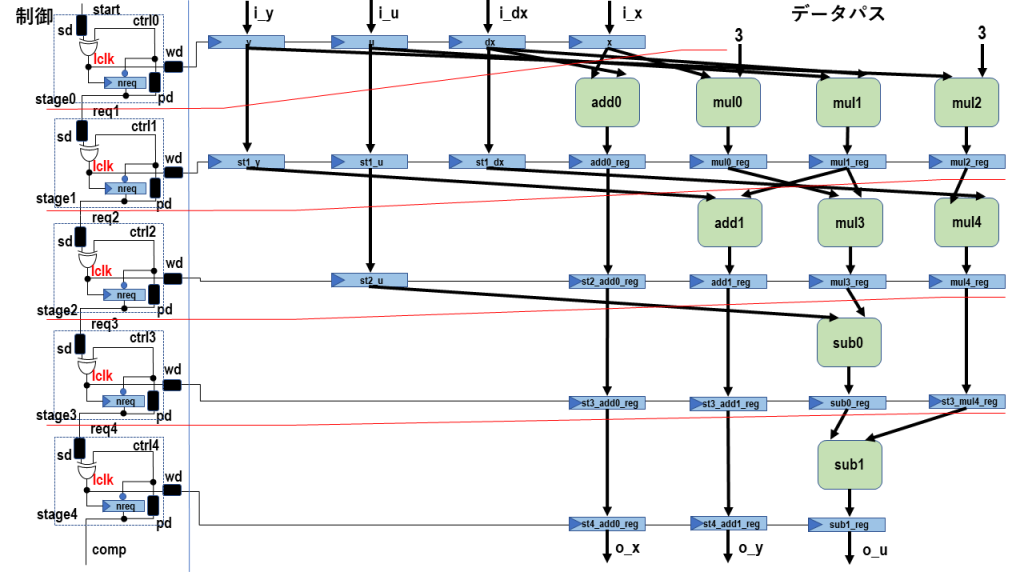

Quartus Prime のような EDA ツールは、同期式回路設計を対象としています。同期式回路の場合、要求性能を満足するためにクロック制約を与えて合成するのが普通です。しかし、非同期式回路にはクロック信号 (細かく言えばグローバルクロック) がないため、要求性能を満足するにはどうすべきかと悩むことがあります。今回はソリューションの1つとして、self-timed モジュールが生成するローカルクロック信号 lclk にクロック制約を与えます。なお、パイプライン回路の場合、前回も説明した通り、一番遅いパイプラインステージにてサイクルタイムが決まってしまいます。そのため、今回の例でも遅延素子の生成同様 (前回を参照ください)、全てのパイプラインステージで同一の制約を与えます。図5は、対象となる非同期式回路モデルですが、lclk を赤で示しています。

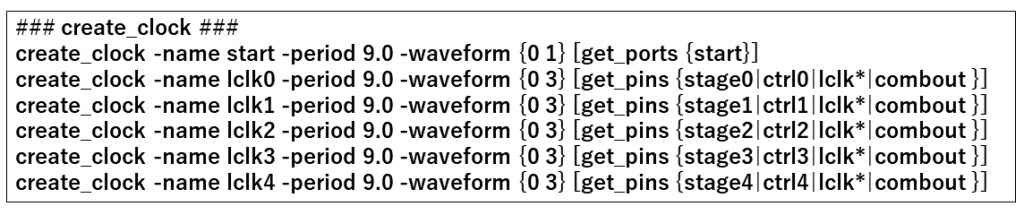

制約は、Synopsys Design Constraint (SDC) 形式で準備します。図6は、生成した SDC ファイルを表します。クロック制約は create_clock コマンドで与えます。

-name はクロック名を記載します。この例では、start と lclk としています。-period は周期です。今回は 9ns としています。-waveform の部分は括弧書きで立ち上がり遷移の時間と立ち下がり遷移の時間を表します。この場合、全ての信号は 0ns で立ち上がり、lclk は 3ns、start は 1ns で立ち下がるとしています。最後は、実際にクロック制約を与える信号名を表し、start は外部入力信号なので get_ports、lclk は XOR ゲートの出力なので get_pins としています。ところで、外部入力信号の start にもクロック制約を与えていますが、これは start も周期的に動作することを想定してのことです。

一方、period の決め方は、以下のように考えています。start は二相式の信号で、立ち上がり遷移と立ち下がり遷移それぞれで次の入力を与えることになります。周期でみると 18ns です。一方、lclk は四相式の信号で、立ち上がり遷移の時にレジスタに書き込みを行います。ここでは、短いほうに合わせるということで period を 9ns としています。なお、start の立ち上がり遷移を 0ns と考えると、本来立ち下がり遷移は 9ns です。しかし、period の値と立ち下がり遷移の値を一致させてしまうと、invalid な与え方と警告がでてしまいます。そのためここでは、適当な値 (1ns) としています。また、lclk の立ち下がりを 3ns としていますが、特に深い意味はありません。

今回は考慮しませんが、仮にもし、一部のパスに対して、最大・最小遅延制約を与えたい場合は、set_max_delay/set_min_delay コマンドを用いて与えることもできます。

準備した SDC ファイルは、Verilog HDL ファイルと同様、プロジェクトに追加します。

配置制約の生成

配置制約ですが、ここでは2種類の配置制約を使っていきます。一つは、Design Partition と呼ばれるものです。もう一つは、Logic Lock と呼ばれるものです。こういったものが必要な理由とどのように設定していくのかを説明していきたいと思います。

Design Partition の準備

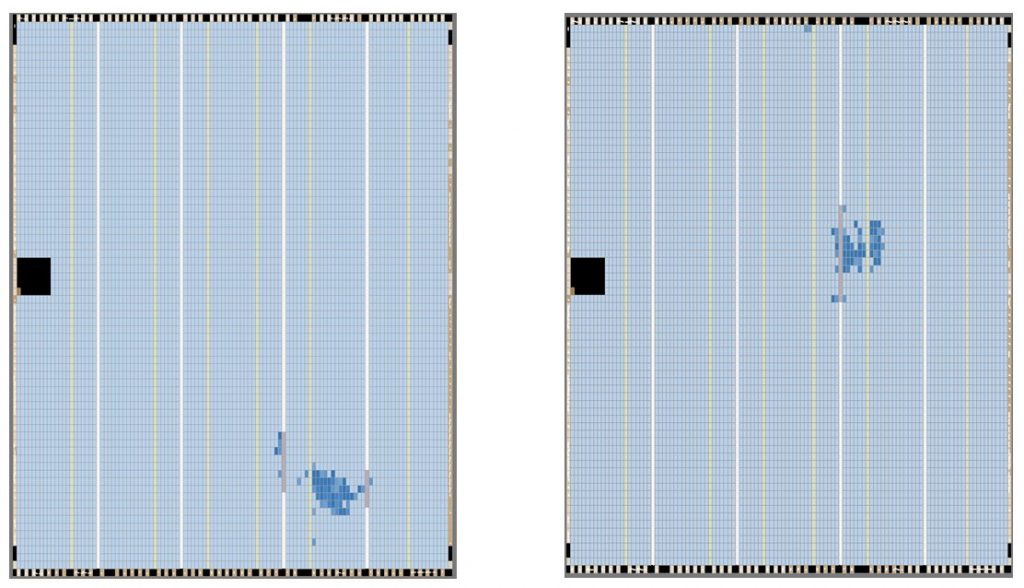

タイミング検証と遅延素子の調整 (遅延調整) に関しては、次回に詳しく説明するつもりですが、Design Parition は、タイミング収束を測るための手段として用います。以下の図を見てください。左は、Quartus Primeで合成を行った後、Chip Planner (Quartus Prime のメニューのなかで、Tools から選択) を開いたときの画像です。ちなみに、Chip Planner は、配置を確認するためのツールです。右は、sd1 に対して NOT を2つ追加して (遅延調整を想定) Quartus Prime で合成を行った後の Chip Planner の画像です。見てわかると思いますが、回路の配置が大幅に変わっています。

遅延調整を行うことで、回路の配置が大幅に変わってしまうと、折角タイミング違反を解消しようと遅延を調整したのに、それ自体が維持されなくなってしまう可能性があります。この問題を解消するために、Design Partition を用います。Design Partition は、リソース毎に合成のどの段階を維持するのかを指定することができます。例えば、POST_SYNTH とすると、論理合成後の結果が維持され、POST_FIT とすると配置配線 (Quartus Prime では Fitting と呼びます) 後の結果が維持されるということになります。遅延調整をしても大幅な配置の変更をさせないというのが、Design Partition を用いる目的です。もう1つ、Design Partition を使うメリットがあります。合成時間の短縮です。結果を維持するということは、変更があったところだけ時間をかけるということになります。しかし、デメリットもあります。Partition で区切られたリソースは、最適化が限定されてしまうということです。その結果、より多くの Logic Element を必要としてしまいます。

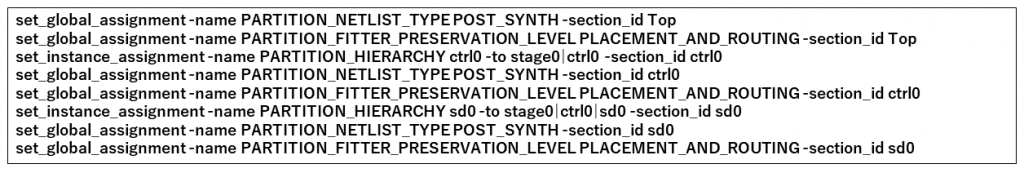

以上を考慮して、Design Partition は必要最小限で、トップレベルモジュール、self-timed モジュール、および各遅延素子に設定することとします。最初の合成では、全てPOST_SYNTH に設定します。self-timed モジュールにも Design Partition を設定するのは、self-timed モジュールに対して想定していない最適化が掛かることを避けるためです。特に束データ方式による非同期式回路の場合、制御回路に予期せぬ信号遷移 (ハザードとも呼ぶ) が発生してしまうと誤動作になる恐れがありますので、予防的に行っていると思っていただければと思います。図8は、TCL による Design Partition の設定の一部を表します。トップレベルモジュール以外、1つのリソースにつき、3つのコマンドを準備しています (set_instance_assignment と2つの set_global_assignment)。最初のset_instance_assignment は階層の指定、次の set_global_assignment はネットリストタイプの指定、最後の set_global_assignment は配置配線における維持レベルの指定です。リソース名に該当するところは (例えば ctrl0 や sd0、あるいはそれらを含むパス) 適切に与える必要があります。

準備した2つのTCL ファイルは、合成オプションと同様に、Quartus Prime のメニューから Tools を選び、表示されたリストのなかで Tcl Scripts を選んだあと、ファイルを選択して、実行すれば良いということになります。もちろん、TCL Console から source で指定しても構いません。なお、TCLファイルは1つにまとめてもらっても問題ありません。1つのファイルに多くのことを記載すると、ファイルの読み込みに時間が掛かるため2つに分けているにすぎません。

Logic Lock の準備

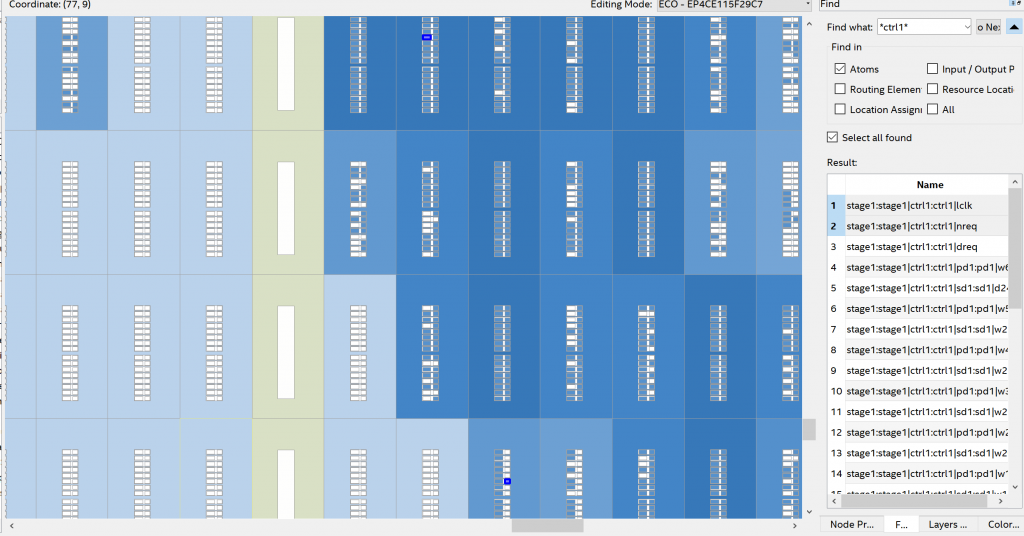

Logic Lock の使用には、2つの目的があります。1つは性能改善で、もう1つはタイミング収束です。図9は、配置制約を使用しないで合成した非同期式回路の配置を表します。この図は、Chip Planner の画面を拡大していったものです。

小さいですが、青枠がついたところは上が ctrl1 の XOR で、下は ctrl1 の DFF です。ctrl1 のリソースなので、離れた場所に配置されているのが確認できます。このように、同じリソースに対する論理がFPGAの離れた場所に配置されてしまうと、当然のことながら配線遅延の影響が無視できなくなてしまいます。結果として、性能が悪くなってしまうことがあります。

Logic Lock は、配置領域を指定するための制約で、リソース毎に設定することができます。Logic Lock を用いることで、上記の問題を解決することが期待できます。Logic Lock ですが、今回は、トップレベルモジュール、各パイプラインステージ、各 self-timed モジュール、及び各遅延素子に設定します。ところで、前回のモデリングのところで、わざわざリソース毎に階層化するような記述にしましたが、Logic Lock を指定する際、インスタンスレベルで指定するため階層化した記述にしておいたということになります。

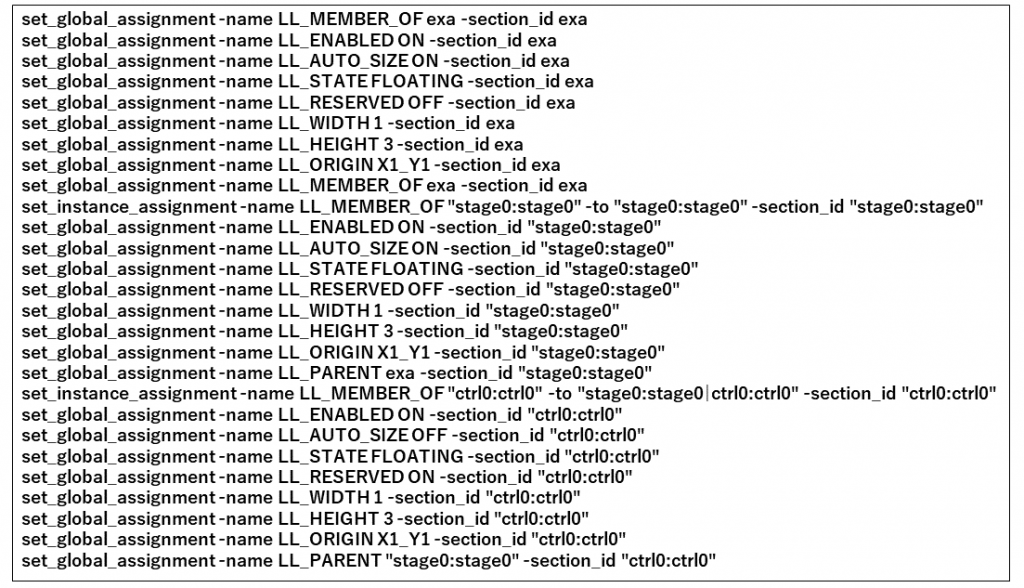

Logic Lock では、配置領域のサイズや FPGA 上の座標を指定することができます。また、配置領域内に他のリソースの配置を許容するかどうかも指定することができます。図10は、Logic Lock の設定を表す TCL ファイルの一部です。

トップレベルモジュールの exa と stage0 は、ほぼ同じ設定です。ctrl0 は少し設定が異なります。LL_MEMBER_OF ですが、Logic Lock を指定する配置領域名と指定するリソースを記載します。LL_ENABLED は、ON で配置領域を有効にします。LL_AUTO_SIZE は配置領域を Quartus Prime に決めてもらい場合 ON となります。OFF の場合、LL_WIDTH と LL_HEIGHT で指定した配置領域に配置するようになります。指定する値ですが、Logic Array Block (LAB) 数です。対象となる Cyclone IV FPGA ですが、16個の logic element で1つの LAB となります。例えば ctrl0 の場合、幅1、高さ3の配置領域という意味になります。ところで、LL_AUTO_SIZE を ON にした exa と stage0 にも LL_WIDTH と LL_HEIGHT を指定していますが、この部分を記載しないと、TCL ファイルを読み込んだ際、幅1高さ1の領域となってしまうため、子階層の中で一番大きな領域のサイズに合わせています。LL_STATE は配置座標の指定です。FLOATING の場合、Quartus Prime が自動で決めます。LOCKED の場合、自分で座標を指定する必要があります。LL_ORIGIN は、基準座標を示します。最後に LL_PARENT ですが、親の階層を指定します。

Logic Lock を扱うときには、Design Partition 同様、注意が必要です。Logic Lock によって、最適化に制限をかけてしまいます。また、Logic Lock の中にある FPGA のリソース数より回路で必要となるリソース数 (これは logic elementだけではなく、配線リソースやメモリ、DSP も含みます) の方が多い場合、配置配線が失敗します。この他にも、設定するリソースの数が増えると合成時間が延び、設定するリソースの数が少ないと離れた位置に配置されてしまう可能性があるということになります。こうしたことを踏まえて、設定する必要があるため結構面倒です。また、これまでの経験上、配置領域サイズや座標を Quartus Prime に自動で決めてもらうとしても、必ずしも質の良い回路を出してくれるわけではないのだなというのが率直な印象です (余談ですが、回路規模が大きなケースで実際に頭を痛めています)。

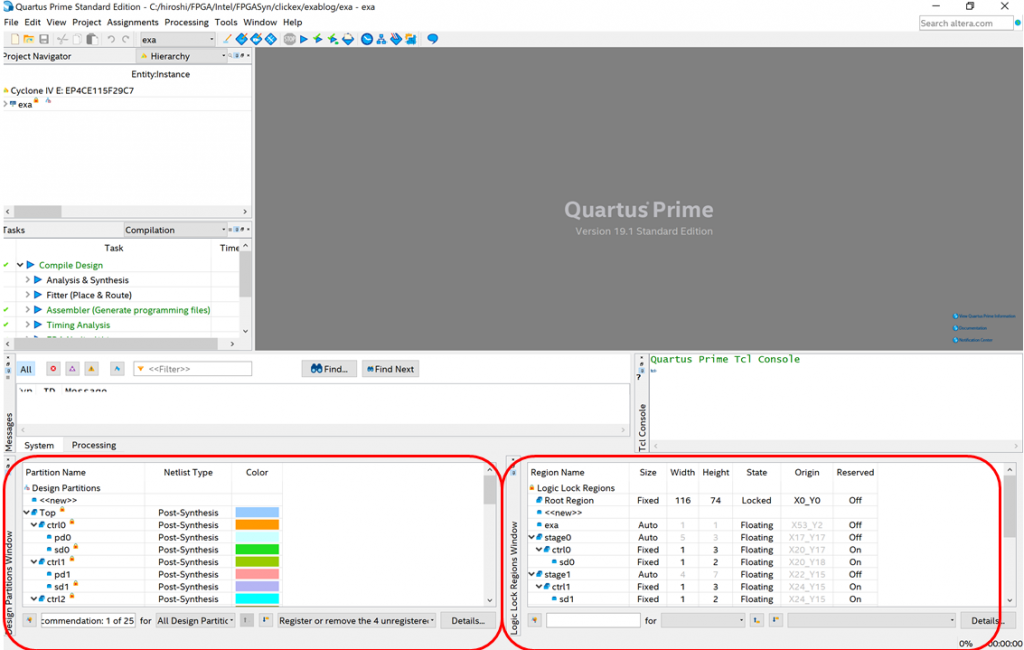

GUI による設定

今回、Design Partition や Logic Lock を TCL ファイルで準備する方法を説明しましたが、Quartus Prime では、図11赤枠のようにこれら専用の Window がありますので、GUI レベルで視覚的に設定することができます。慣れないうちや、TCL ファイルの準備が面倒という場合は、そちらを利用するのがお勧めです。デフォルトでこれらの Window がない場合は、Quartus Prime のメニューより Assignments を選んでいただき、一番最後にある2つ Logic Lock Regions Window と Design Partition Window を選択して下さい。

合成

必要となる全ての入力を準備しましたので、最後に合成を行います。確認ですが、ここまでに遅延素子をプリミティブで実現した HDL ファイル、SDC ファイルをプロジェクトに追加する必要があります。前回利用した、時間指定の遅延素子ファイルは、この段階でプロジェクトから削除してください。また、合成オプション、Design Partition、Logic Lock に関する TCL ファイルは、上記で説明した通りに実行しておく必要があります。全ての準備が整ったら、Quartut Prime の Compile ボタンを押して合成してください。合成が問題なく終了した後、配置制約の効果を Chip Planner で確認すると図12のようになります。

今回はここまでです。お疲れさまでした。

次回は

次回は、タイミング検証と遅延調整を説明する予定です。

会津大学 齋藤 寛