20Q4.02B

20Q4.02BFPGA を対象とした非同期式回路の設計 (5)

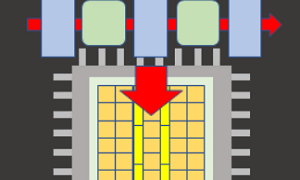

皆さん、こんにちは。今回は、前回までに合成した非同期式回路の機能検証と評価を説明していきます。前回をご覧になっていない場合は、初めにそちらをご覧下さい。 設計フローの続き 図1は、前々回示した設計フローです。 図1 設計フロー 前回の終了時点で、タイミング違反がないことを確認しました。今回は、その段階での Quartus Prime プロジェクトを想定して、説明をしていきます。 機能検証 ここでは、第2回で解説した RTL シミュレーションと同じ...