皆さん、こんにちは。今回は、前回までに合成した非同期式回路の機能検証と評価を説明していきます。前回をご覧になっていない場合は、初めにそちらをご覧下さい。

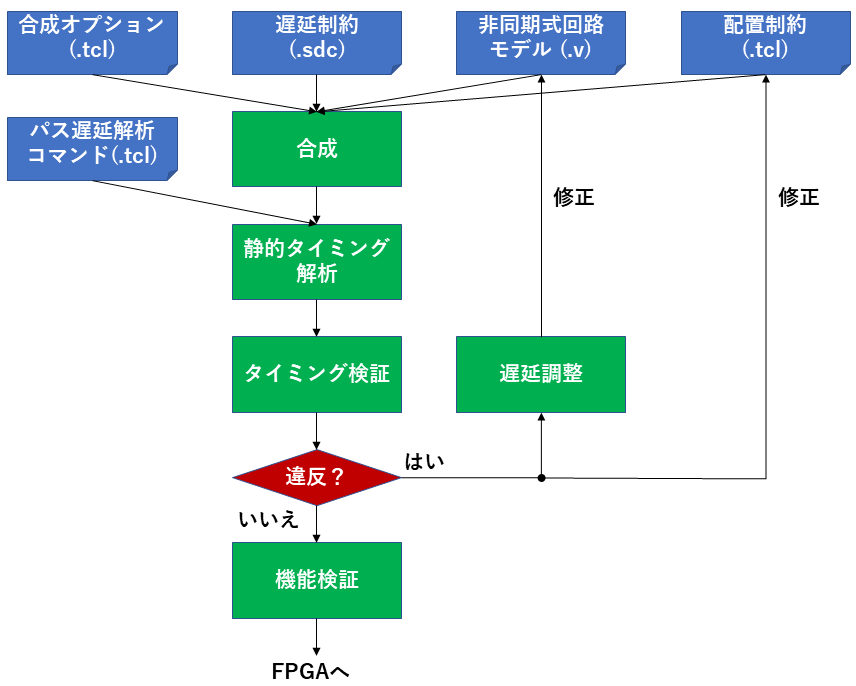

設計フローの続き

図1は、前々回示した設計フローです。

前回の終了時点で、タイミング違反がないことを確認しました。今回は、その段階での Quartus Prime プロジェクトを想定して、説明をしていきます。

機能検証

ここでは、第2回で解説した RTL シミュレーションと同じテストパターンを用いて、機能検証をしていきます。なお、Quartus Prime では、合成が済んだ段階でのシミュレーションは Gate Level シミュレーションと呼びます。

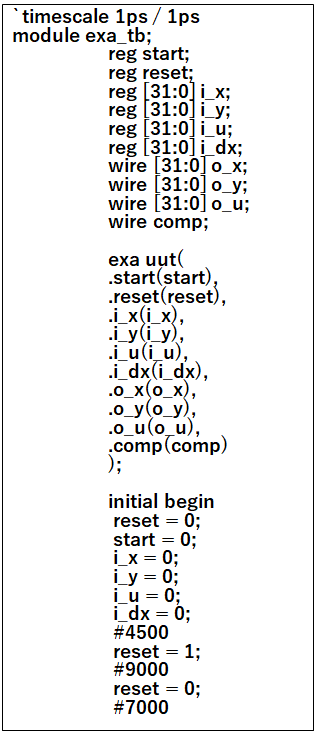

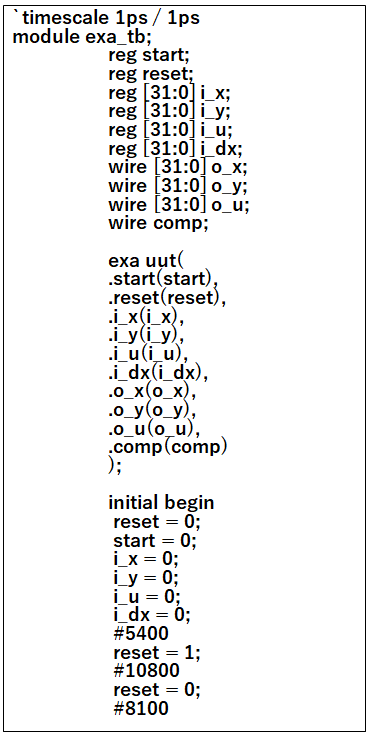

図2は、RTL シミュレーションの時に使用した、exa_tb.v です。

前回の終了時点で、サイクルタイムが10.8になることを確認しましたので、この exa_tb.v のなかで、時間に関するところは修正が必要です。#9000 のところは #10800、#4500 のところは #5400、#54000 (#9000×6 サイクル) のところは #64800 (#10800×6 サイクル)、最後に #7000 のところは #8100 とします。図3は、Gate Level シミュレーションのために修正した、exa_tb.v です。

exa_tb.v 自体は、RTL シミュレーションの時に、Qaurtus Prime プロジェクトに含めています。ですので、exa_tb.v が保存されているところに上書きすれば、そのままプロジェクト内で使用することが可能です。

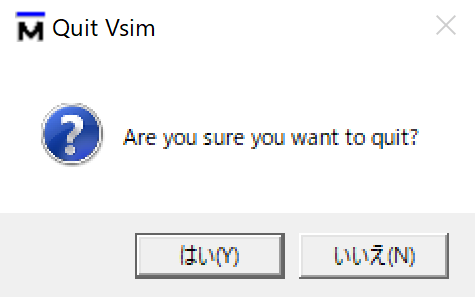

Quartus Prime プロジェクトに修正した exa_tb.v を反映した後は、再度 Compilation ボタンを押します。その後、Quartus Prime のメニューから Tools→Run Simulation Tool→Gate Level Simulation を選びます。ModelSim が起動して、図4のような画面がでたらいいえを押すと波形が表示されます。

ここで、注意が2つあります。1つは、図4の画面が出ない場合です。その場合、ModelSim の Transcript ウインドウに赤字で error が出ていると思います。こちらを修正する、あるいはシミュレータの設定が正しく行われているか (第2回の図7から図10を参照) 確認してください。もう1つは、波形が出たけど、不定値が出ているような場合です。この場合も Transcript ウインドウを確認してもらえば、おそらく青字で setup、もしくは hold 違反が出ていると思います。タイミング検証にミスや漏れがある可能性が高いので、再確認が必要です。

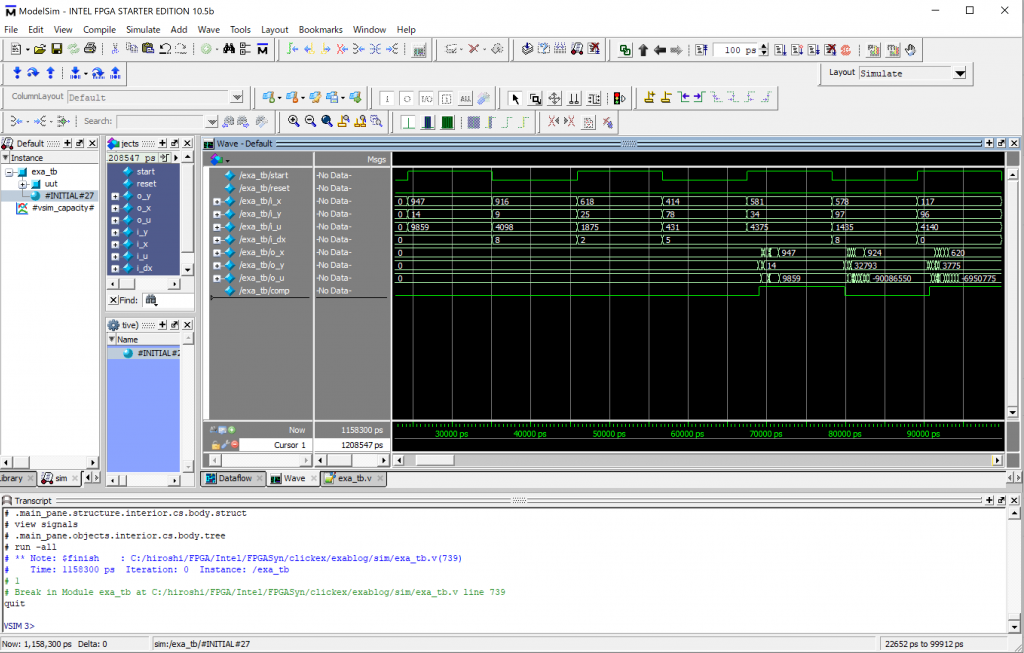

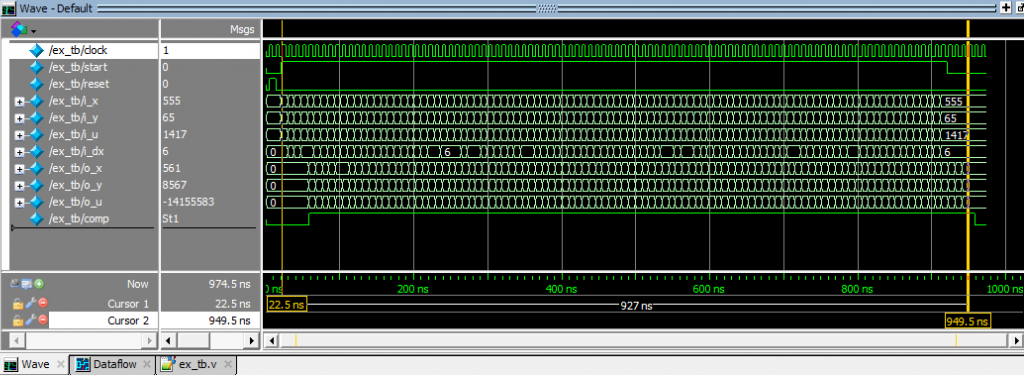

図5は、生成された波形です。Transcript を見ると、error もタイミング違反もなく、シミュレーションが終わっているのを確認することができます。

RTL シミュレーションの結果と一致すれば、機能的に問題がないということになります。

評価

評価は、回路面積、実行時間、消費電力、消費エネルギーの順で行っていきます。評価に関しては、同期式回路も非同期式回路も手順は同じです。ここでは、非同期式回路に焦点を当てて説明していきます。

回路面積

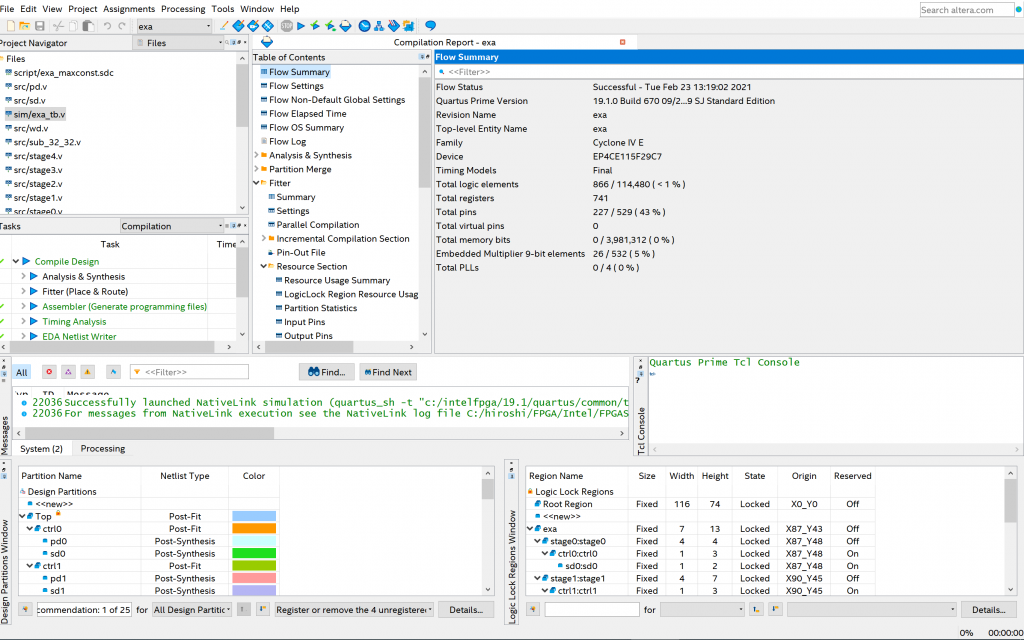

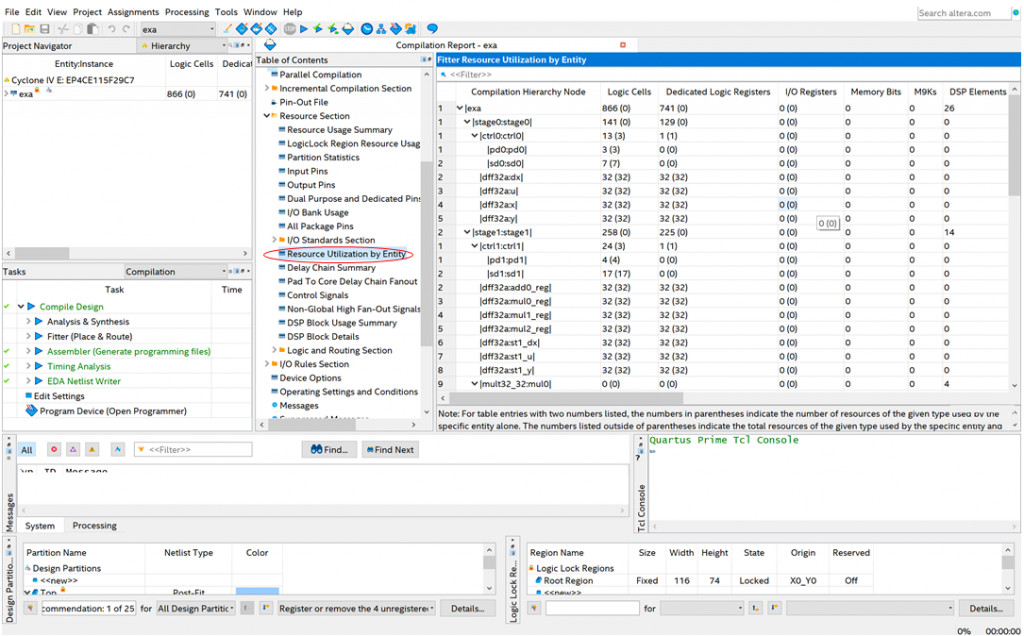

回路面積は、Quartus Prime が合成時にレポートを生成しますので、そちらを確認していきます。Intel Cyclone IV FPGA における、基本素子は Logic Element (LE) です。ですので、LE 数を確認します。合成が終わると、自動的に Compilation Report を表示してくれます (表示されない場合、メニューにある Processing→Compilation Report を選んでください)。図6は、Compilation Report を表します。

基本的な情報は、Flow Summary の項目で確認することができます。今回の例では、Total logic elements が 866 になっているのが分かります。その左にある、Table of Contents から、更に詳細を確認することができます。Fitter の下にある、Resource Section の中に、Resource Utilization by Entity というのがありますが、こちらを選ぶと、リソース毎の使用LE数を確認することができます (図7)。

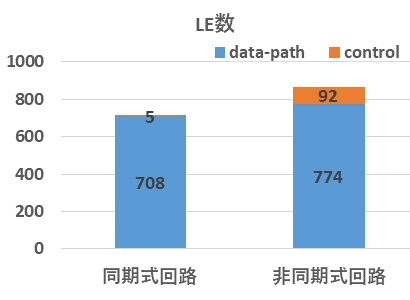

図8は、今回の例における同期式回路と非同期式回路の LE 数を表したものです。

非同期式回路ですが、全体でみると14%の増加となっています。そのうちの半分以上は遅延素子を含んだ self-timed モジュールによるものです。残りは、データパス回路における増加分です。この増加分は、LogicLock や Design Partition といった配置制約の影響です。

実行時間

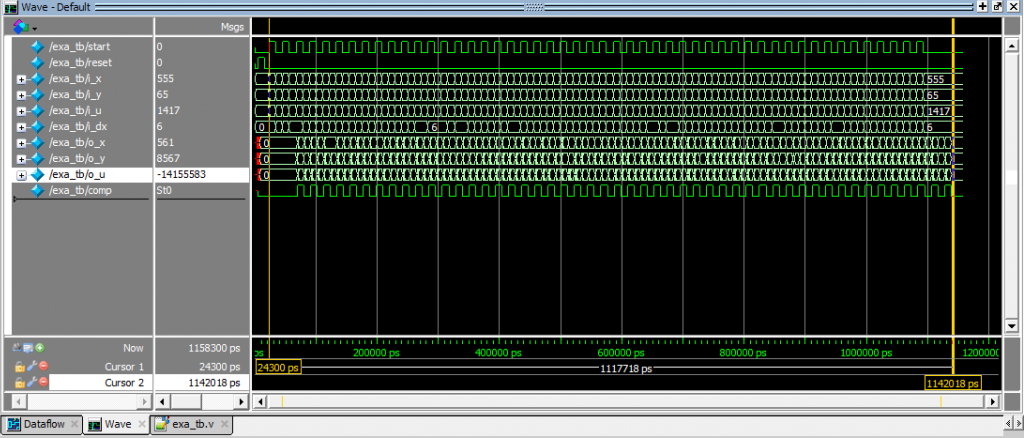

実行時間は、ModelSim によるシミュレーション結果より求めます。図9は、同期式回路の処理開始のサイクルから処理集合のサイクルにカーソルを当てて実行時間を得たものです。図10は、同様に非同期式回路です。非同期式回路の方は、最後のデータが出力された時点としています。

時間の単位が違うことご注意ください。

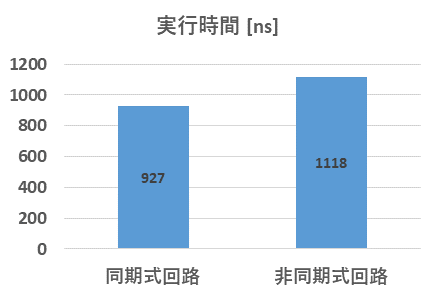

図11は、実行時間をグラフで表したものです。

実行時間は、同期式回路と比べ約21%遅くなっています。この原因は、サイクルタイムの増加にあります。同期式回路が 9ns だったのに対して、非同期式回路は 10.8ns でした。その原因ですが、パイプラインステージ1と2のところで、max(sdp) が 11ns に近いパスが複数存在したためです (max (sdp) は、データパス sdp の最悪遅延です)。また、前回ホールド制約を満足するために 0.5ns サイクルタイムを増やしています (詳しくは、前回を確認してください)。

こうした問題に対する対策として、lclk からソースレジスタ、lck からディスティネーションレジスタの遅延をそろえること、及び wd を調整することでホールド制約を解消することが挙げられます。

消費電力

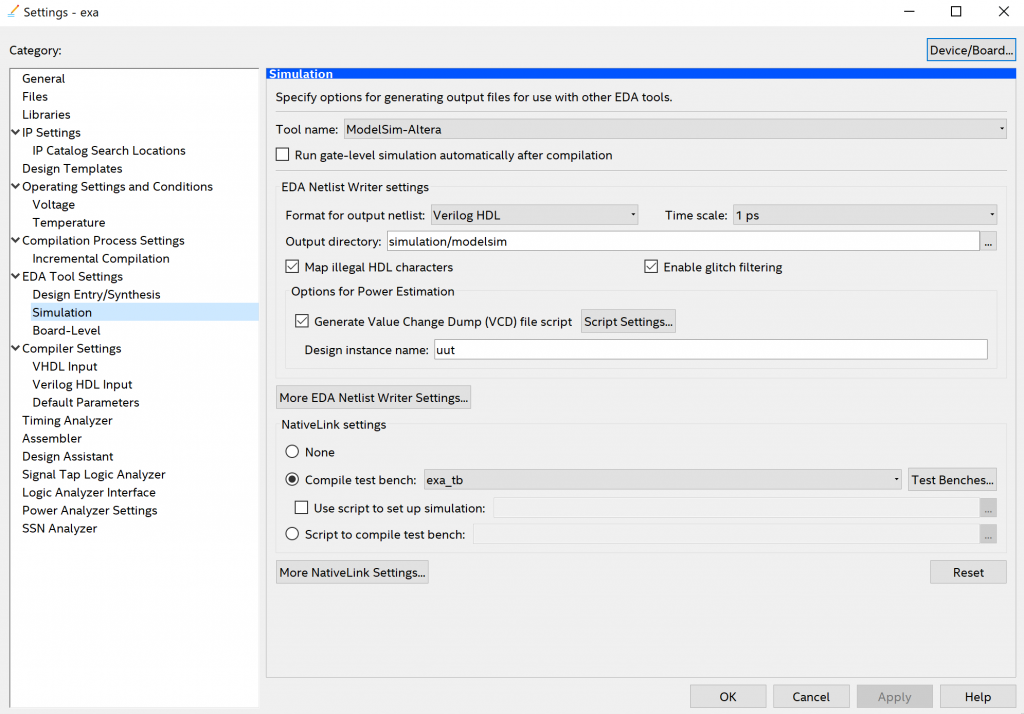

消費電力に関しては、シミュレーションの際に生成した Value Change Dump (VCD) ファイル (信号の遷移を表したファイル) を用いて評価します。VCD ファイルですが、シミュレーションの設定の際に、指定しています (第2回参照)。図12は、シミュレーションの設定の画面です。

Generate Value Change Dump (VCD) file script のチェックボックスにチェックを入れ、Design instance name を指定すれば、ModelSim を閉じたときに、VCD ファイルが生成されます。Design instance name は、exa_tb.v の中で設計した回路 exa を呼び出していますが、そこに記述したインスタンス名となります。生成された VCD ファイルは、プロジェクトが入ったディレクトリの中に simulation/modelsim という子ディレクトリがありますが、その中に含まれます。

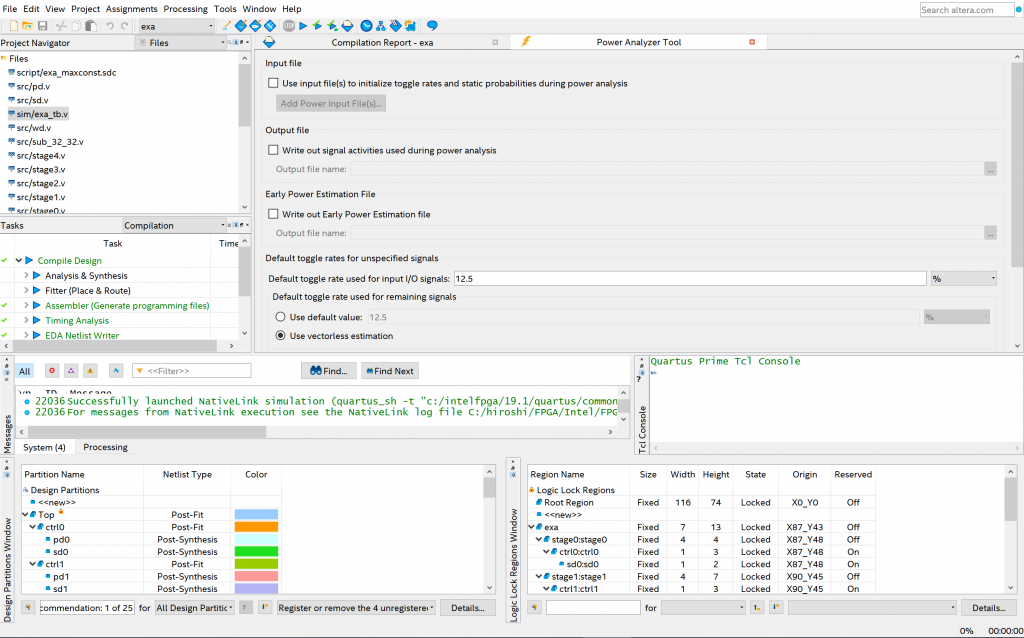

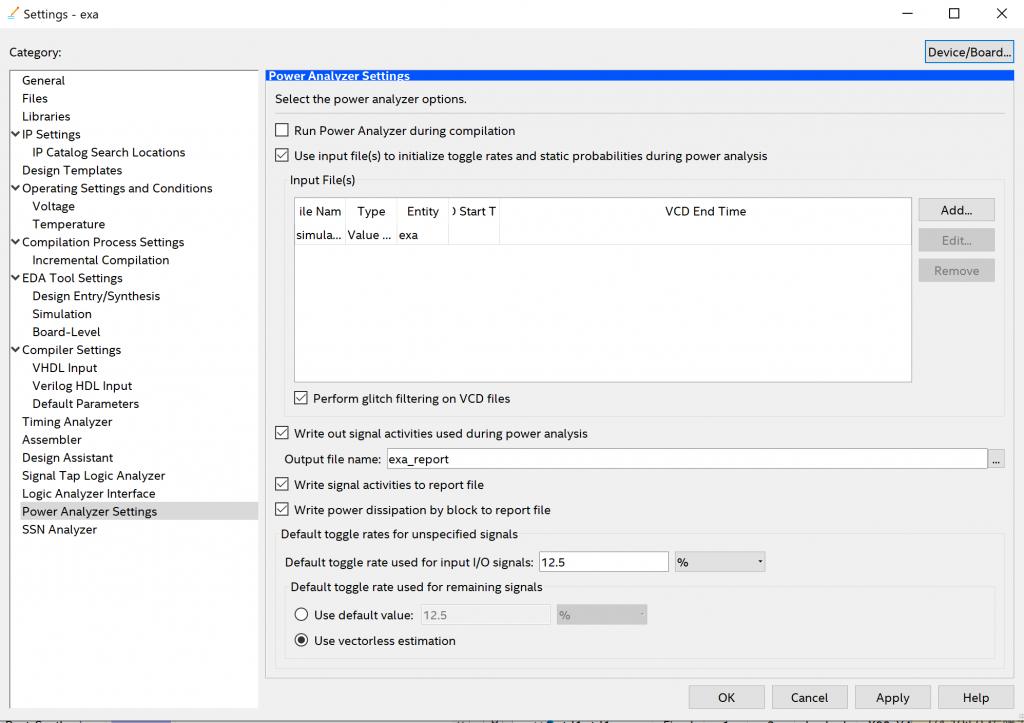

電力解析は、Power Play Power Analyzer を用いて行います。Quatus Prime のメニューから、Processing→Power Analyzer Tool を選ぶと、図13のような設定画面が出てきます。

最初の Use input file(s) to initialize toggle rates and static probabilities during power analysis のチェックボックスをチェックして、Add Power Input File(s) を押します。押すと図14の画面が出ます。

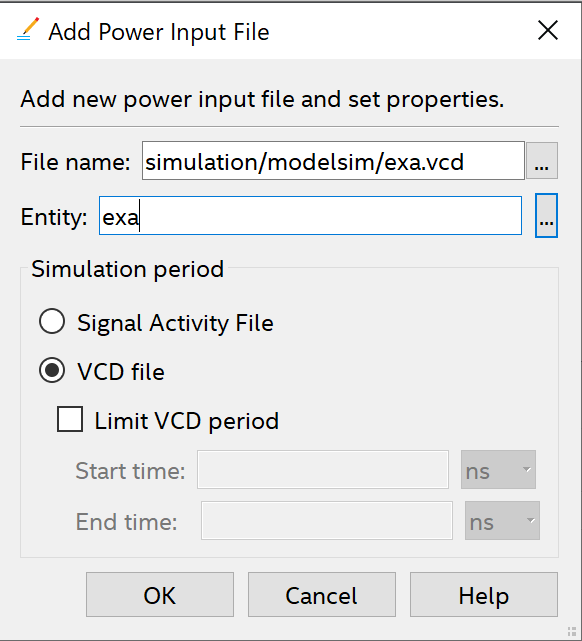

ここで、Add ボタンを押すと、図15の画面が出てきます。

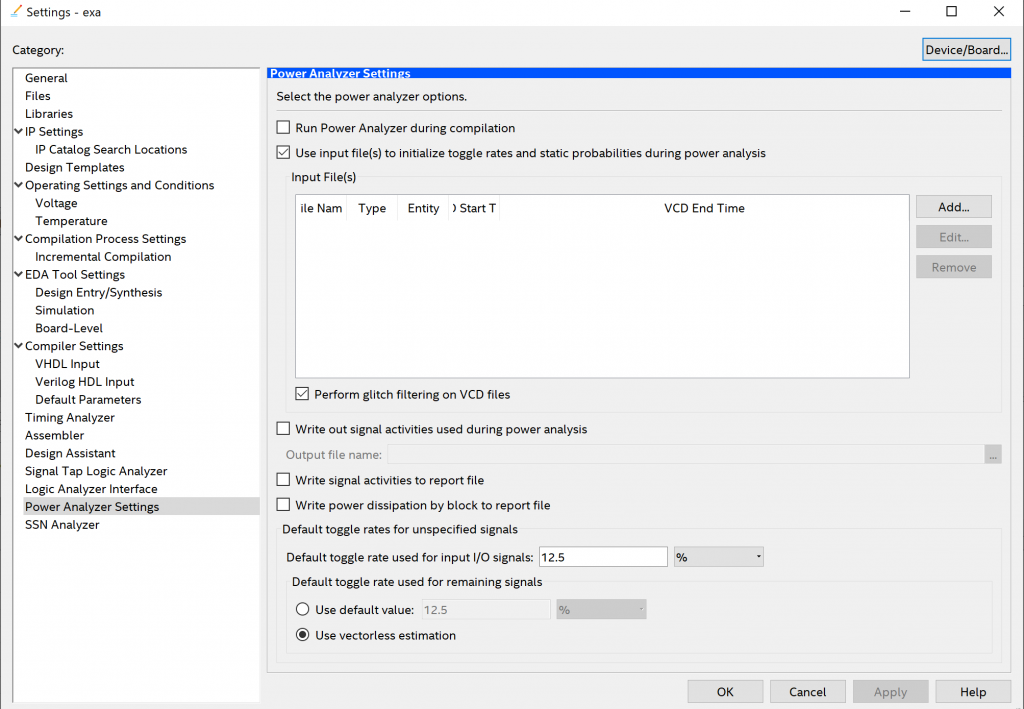

ここで、File name に VCD ファイルを指定し、Entity を指定します。Entity は、設計した回路のモジュール名は exa ですので、exa としています。OK を押すと VCD の指定は完了です。電力解析に関する、詳細な情報を得るために、図14の write で始まるチェックボックスをチェックし、OK ボタンを押します (図16)。

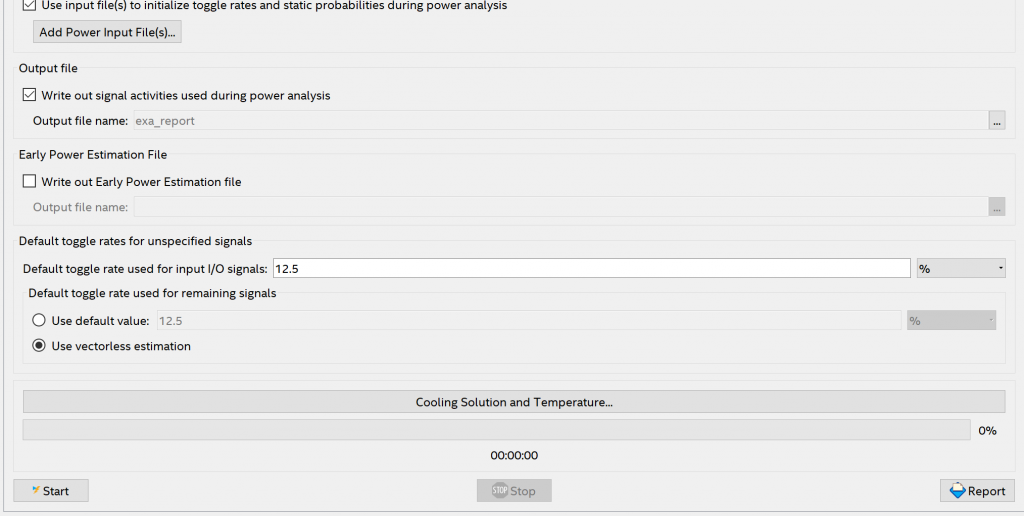

OK を押すと、図13の画面に戻りますので、下にある Start ボタンを押すと、電力解析が始まります (図17)。

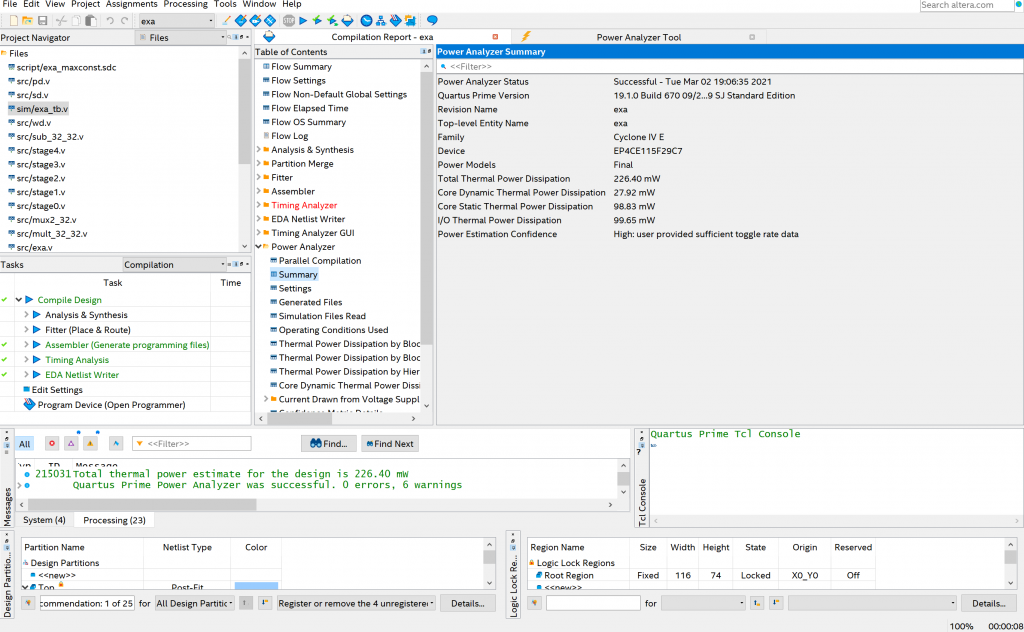

電力解析が終了した後、Compilation レポートの Table of Contents から Power Analyzer の Summary を選択すると、図18の画面が出ます。この画面で、最後にある Power Estimation Confidence を確認してください。こちらが High になっていることを確認してください。Low の場合は、設定が間違っている可能性がありますので、再度行うようにしてください。もしかしたら、VCD ファイルが正しく生成されていない可能性もありますので、再確認してください。

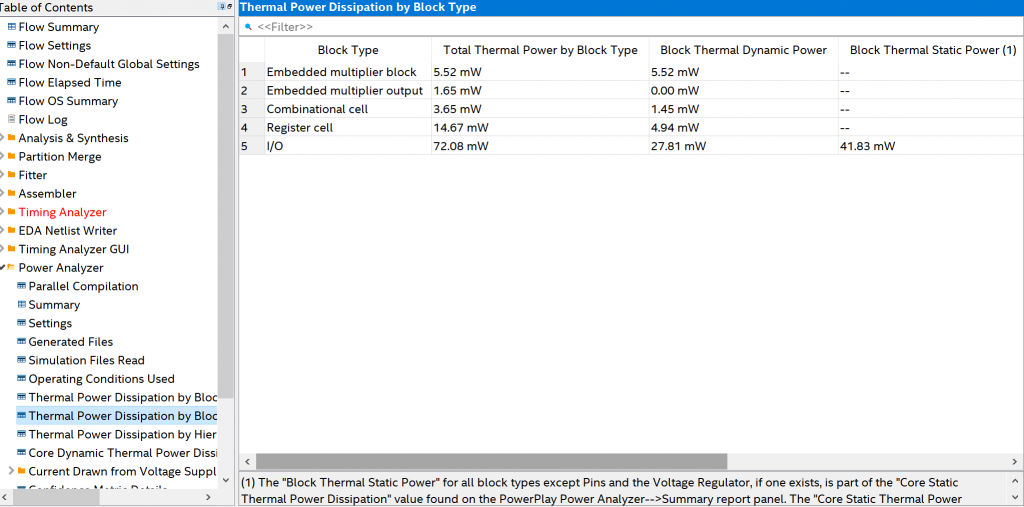

FPGA の要素毎に消費電力を確認したい場合は、Thermal Power Dissipation by Block Type を確認します。回路のリソース毎に確認したい場合は、Thermal Power Dissipation by Hierarchy、回路の信号毎に確認したい場合は、Thermal Power Dissipation by Block を確認します。図19は、Thermal Power Dissipation by Block Type によるレポートです。

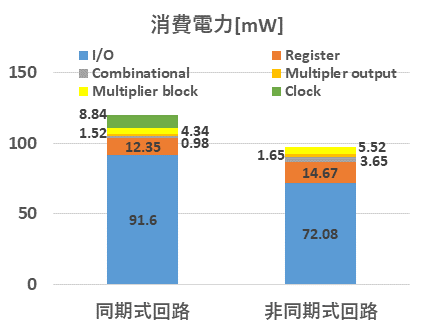

図20は、同期式回路と非同期式回路の消費電力を表します。

同期式回路と比較して、18.4%の削減となりました。Clock の部分が減ったことと、動作スピードが遅くて I/O が減ったことが主な要因です。一方、Multipler、Combinational、および Register は少し増加しています。Combinational に関しては、遅延素子を含んだ self-timed モジュールの影響があるためです。また、それ以外に関しては、配置制約の影響のためです。特に最近の FPGA は、配線リソースにおける消費電力が大きいため、配置配線時に、長い配線ができてしまうと、遅延と消費電力の両方に影響を与えてしまいます。

消費エネルギー

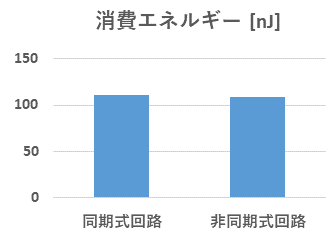

最後に、図21は同期式回路と非同期式回路の消費エネルギーを表します。これらの値は、実行時間×消費電力より求めた値です。

今回の例では、非同期式回路でも1.6%しか減少しませんでした。今回の設計では、可能な限り手数を少なくしたことも原因として挙げられます。一方で、回路規模や構成、および Quartus Prime の最初の合成に依存するところもあります。ですので、良い時もあれば、そうでない時もあります。そのあたりはまだまだ研究が必要だと感じていますが、概ね非同期式回路を FPGA に設計し、評価する方法をご理解いただければ幸いです。

最後に

5回にわたり連載させていただきましたが、自分自身も改めて非同期式回路の設計を見直すことができました。まだまだ、研究しなければいけないところは多々あると思っています。設計支援を行うツールの中で、まだ完成させていないところを完成させると共に、Xilinx の FPGA も扱えるようにしていきたいと思っています。また、色々な回路を評価することで、非同期式回路が効果があるところやそうでないところも明らかにしていきたいと思っています。

FPGA に関しては、非同期式回路の研究を行っている方でも対象とする機会は出てきていると思っています。[Bhardwaj’19] は、その一例で、Xilinx FPGA を対象に非同期式回路を設計する手法を提案しています。ご興味のある方はご参考ください。

最後になりますが、ここまで読んでいただき、ありがとうございました。

会津大学 齋藤 寛

[Bhardwaj’19] K. Bhardwaj et.al, “Towards a Complete Methodology for Synthesizing Bundled-Data Asynchronous Circuits on FPGAs”, Proc. ISLPED, pp.1–6, 2019.