みなさんこんにちは。このコースでは FPGA を使いこなすために理解しておきたい論理回路の基本について説明します。FPGA を使って開発しているけどハードウェアはよく分からないという方は、ぜひお付き合いください。

前回の記事では論理代数の基本で論理演算とそれに対応する論理回路について説明しました。今回は、論理回路の重要な要素をさらにいくつか紹介しつつ、広く用いられているクロック同期回路までを説明します。今回までの内容でディジタル回路を理解するために必要な基本的な要素を習得できます。

組み合わせ回路と順序回路

マルチプレクサ

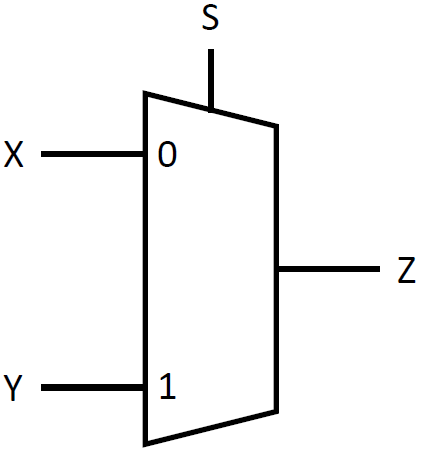

はじめに論理回路において重要な素子であるマルチプレクサを説明します。マルチプレクサはこれまでに紹介した論理演算ではなく、複数の信号から出力するものを選択する素子です。具体的に、2入力のマルチプレクサは、選択信号 S に応じて入力 X、Y から 1 つを選択して Z として出力します。2 入力のマルチプレクサの場合、真理値表と回路図の記号は次になります。

| \(X\) | \(Y\) | \(S\) | \(Z\) |

|---|---|---|---|

| 0 | 0 or 1 | 0 | 0 |

| 1 | 0 or 1 | 0 | 1 |

| 0 or 1 | 0 | 1 | 0 |

| 0 or 1 | 1 | 1 | 1 |

入力は X、Y、S、出力は Z です。

S が 0 の場合は Y の値にかかわらず X の値を出力し、逆に S が 1 の場合は X の値にかかわらず Y の値を出力します。

組み合わせ回路と順序回路

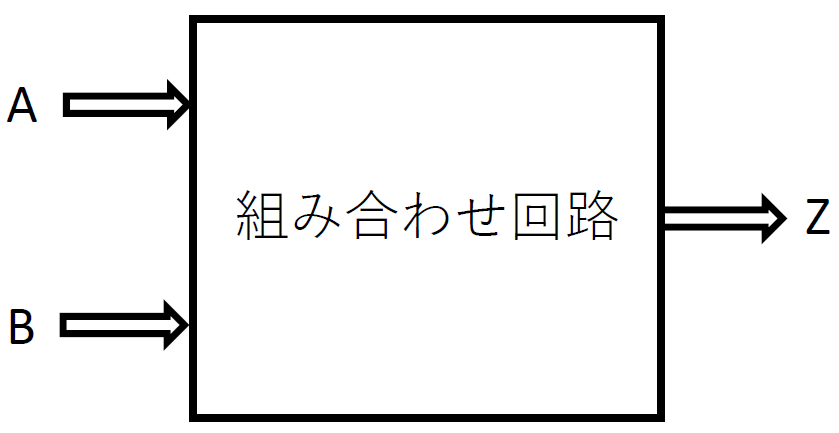

これまでに説明してきた論理演算とマルチプレクサを組み合わせて構成される回路を組み合わせ回路と言います。組み合わせ回路の構成要素は他にもありますが、基本的にはこれまでに説明してきた要素で構成できます。組み合わせ回路を一般的に表現すると、現在の入力のみで出力が決まる回路です。次の図のイメージです。

カウンタのような回路は組み合わせ回路だけでは構成できません。4ビットカウンタを例に考えます。4ビットなので 0 から 15 までを数える回路です。いまカウンタの値が 10 で、これに 1 を足して 11 にしようとします。そのためには、今の 10 という値を覚えておかないと 1 を足して 11 にはできません。つまり、前の状態を覚えておかないと次の状態になりません。

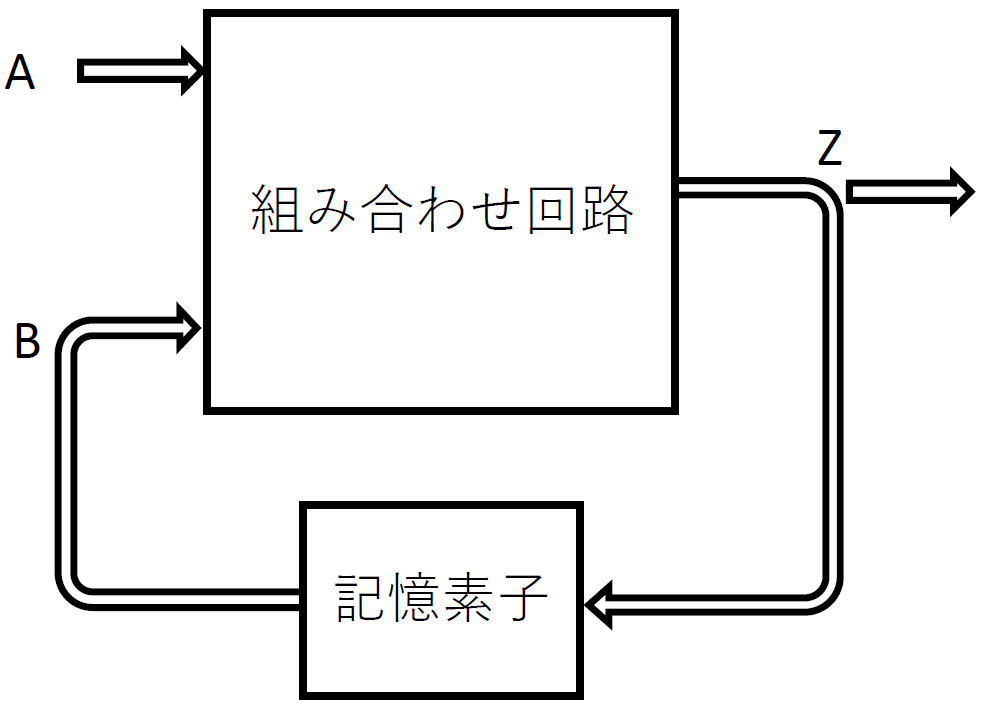

このように前の状態を記憶する必要がある回路を順序回路といいます。順序回路を一般的に表現すると過去から現在までの入力によって出力が決まる回路です。組み合わせ回路は現在の入力のみで出力が決まる回路でしたが、順序回路は過去の入力を記憶する要素(記憶素子)を持ち、それと現在の入力を合わせて出力が決まります。次の図のイメージです。

クロック

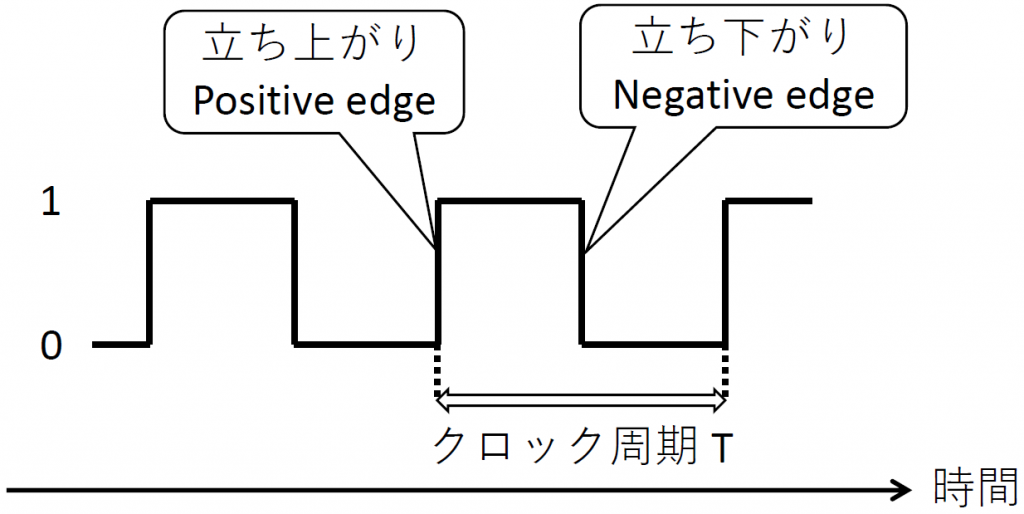

順序回路の1つにクロック同期回路があります。この回路では記憶素子が値を記憶する操作がクロックと呼ばれる信号に同期して行われます。クロック信号は次の図のように一定時間ごとに0と1が反転する信号です。

クロック信号は時間の経過とともに0と1が反転します。0と1の1回の変化に要する時間をクロック周期と呼びます。また、クロックが 0 から 1 に変化するタイミングを立ち上がりエッジ (positive edge),1 から 0 に変化するタイミングを立ち下がりエッジ (negative edge) といいます。

単純な設計のクロック同期回路では回路中にあるすべての記憶素子の操作が 1 つのクロック信号によって同じタイミングで行われます(論理的には同時ですが、実際には多数ある記憶素子を完全に同時に動作させることは不可能なので様々な設計上の工夫がなされます)。

例えば、パソコンの主要なパーツである CPU はクロック同期回路でできています。CPU の性能のひとつに動作周波数がありますが、これは、クロック信号が 1 秒間に 0 と 1 を繰り返す回数を表しています。例えば 1 GHzの CPU であれば1秒間に10 億回 (1G 回) 0、1を繰り返すクロック信号です。つまりクロック周期が1ナノ秒のクロック信号が使われているということになります。

FPGA 開発においても「設計した回路が何 MHz で動作する」といった話が出てきます。FPGA で設計している多くの回路もクロック同期回路です。

フリップフロップ

順序回路の記憶素子として一般的にフリップフロップが用いられます。フリップフロップは入力信号を加えない限り現在の状態を保持し続ける素子です。「FF」と略されます。

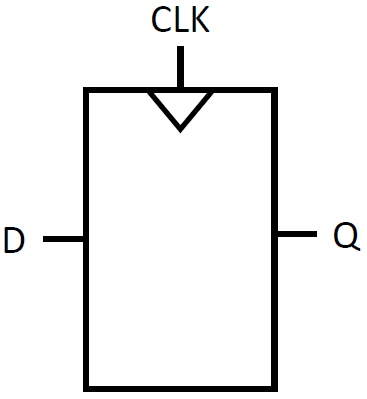

フリップフロップにはいくつかの種類がありますが、クロック同期回路で広く用いられているフリップフロップは D フリップフロップです。

D フリップフロップはクロックの立ち上がりや立ち下がりで入力の値を取り込み、出力の値を変化させます。クロックの立ち上がりで値を取り込む D フリップフロップの動作、回路図での記号は次のようになります。

| \(D\) | \(CLK\) | \(Q\) |

|---|---|---|

| 0 or 1 | 0 | 保持 |

| 0 or 1 | 1 | 保持 |

| 0 or 1 | ↓ | 保持 |

| 0 | ↑ | 0 |

| 1 | ↑ | 1 |

入力は D とクロック信号 CLK で、出力は Q です。真理値表の「↑」はクロックの立ち上がり、「↓」はクロックの立ち下がりを表します。CLK が 0、1、↓ の時は入力にかかわらず出力の値は変化しません (保持)。CLK が立ち上がりの時は入力の値が取り込まれ、その値が出力となります。

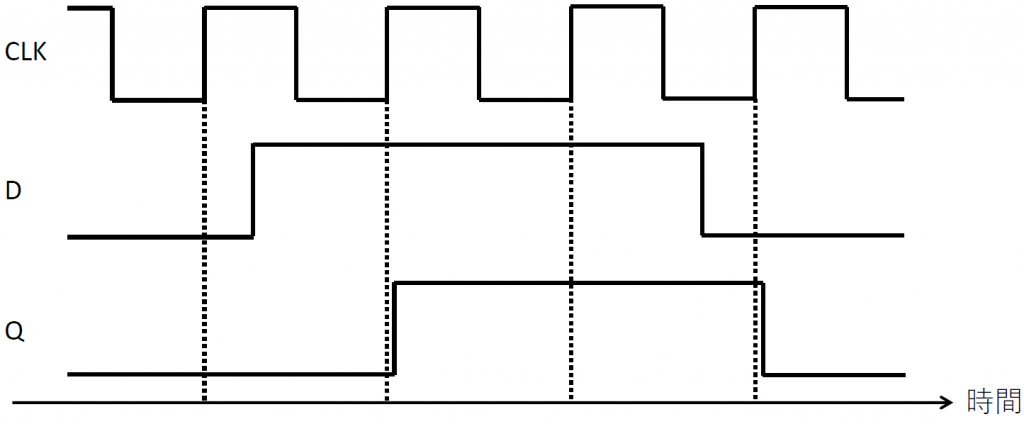

信号の時間変化を表す図をタイミング図と呼びます。D フリップフロップのタイミング図を見ると、入力 D が 0 から 1 に変化した後のクロックの立ち上がりでフリップフロップの値が取り込まれ出力 Q が 0 から 1 に変化します。同じように D が 1 から 0 に変化した後の立ち上がりで Q は 0 に変化します。

フリップフロップは値を取り込むタイミング以外で入力の値が変化しても出力は変化しません。一方で、入力の値を正しく取り込むために、値を取り込むタイミングの前後にはセットアップ時間とホールド時間という入力の値が変化してはいけない期間があります。今回の記事ではこれについては詳しい説明は省きます。

大事な点は、フリップフロップの前にある組み合わせ回路の出力を正しくフリップフロップに記憶させるためには、クロック信号の周期を調整してフリップフロップへの入力が安定するように設計する必要があるということです。

単相クロック同期回路

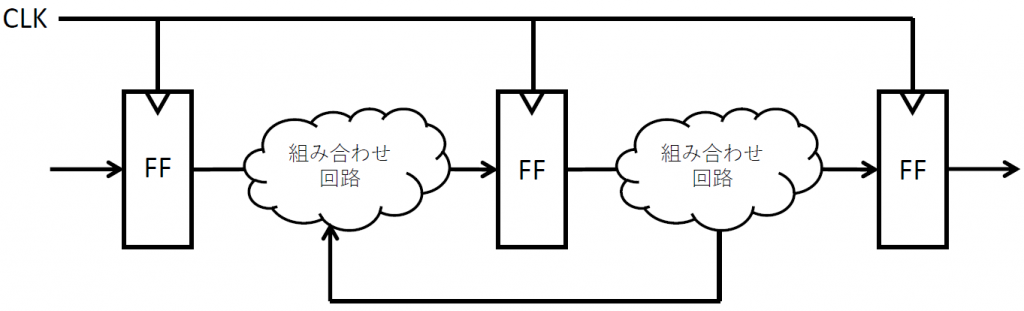

クロック同期回路は組み合わせ回路とフリップフロップで構成される順序回路です。さらに、クロック信号が1つのクロック同期回路を単相クロック同期回路と呼びます。FPGA 開発ではこの単相クロック同期回路の設計が基本になります。図にすると次のようなイメージです。

フリップフロップが 3 個あり、それぞれのフリップフロップの間に組み合わせ回路があります。すべてのフリップフロップには同じクロック信号が接続されています。

回路遅延とクロック周期

上のような単相クロック同期回路があったときに、クロック信号の周期はどう決めればよいか考えてみましょう。

組み合わせ回路は論理ゲートなどで構成されます。論理ゲートにはそれぞれ遅延があります。これは、論理ゲートに信号が入力されてから出力の値が決まるまでの時間です。また、それぞれの論理ゲートをつなぐ配線(ワイヤ)にも信号が伝搬する遅延があります。組み合わせ回路の遅延、つまり組み合わせ回路に信号が入力されてから出力が決まるまでの時間は、出力まで通過する論理ゲートと配線の遅延の和になります。

組み合わせ回路の中で信号が通る論理ゲートの系列をパスと呼びます。したがって、組み合わせ回路にはいくつかのパスが存在し、それぞれのパスごとに遅延が決まります。それらの中で最も大きい遅延を最大遅延、最も小さい遅延を最小遅延といいます。最大遅延はその組み合わせ回路の出力が決まるまでにかかる最悪のケースの時間です。

組み合わせ回路の前後にはフリップフロップがあり、クロック信号にしたがって組み合わせ回路の出力する値を取り込みます。このとき、クロック信号の周期を組み合わせ回路の最大遅延よりも大きくしておかないと正しい出力結果をフリップフロップに取り込めません。つまりクロック信号の周期はフリップフロップ間の組み合わせ回路の最大遅延によって制限されます。

クリティカルパス

クロック同期回路の全体を見ると、組み合わせ回路がいくつかあります。クロック信号が 1 つの場合、回路を正しく動作させるにはすべての組み合わせ回路の最大遅延の中で一番大きな遅延に合わせてクロック周期を決める必要があります。このようにクロックの周期を決定する最も大きな遅延を持つパスをクリティカルパスと呼びます。つまりクリティカルパスがそのクロック同期回路の動作速度を決めるのです。

クロック同期回路を設計したときに、1 つもしくは複数のクリティカルパスが回路内に存在します。それらのパスの設計を見直して遅延を削減できればより小さいクロック周期を用いることができ、より高性能な回路となります。

FPGA ではどうなる?

前回の記事で LUT (Look-Up Table) が FPGA の重要な構成要素という話をしました。LUT は真理値表をそのまま表現できる組み合わせ回路です。FPGA には LUT と今回紹介したフリップフロップ、マルチプレクサなどで構成される論理ブロックが多数搭載されています。そして、その論理ブロックが配線でつながれている構造になっています。

FPGA で実現される回路は、イメージとしてはクロック同期回路の論理ゲートが LUT に置き換わった回路になります。LUT の遅延と論理ゲートの遅延は一致はしませんが、FPGA で高性能な回路を設計するためには自分の開発している回路がクロック同期回路としてどのような構成になるかが大きな手がかりになります。

まとめ

今回は、組み合わせ回路と順序回路について、そしてクロック同期回路について説明しました。これで、FPGA 開発のために知っておくと良い論理回路の基本的な部分がおさえられました。

次回はいよいよタイトルにもある4ビットカウンタが登場します。4ビットカウンタをハードウェア記述言語で記述し、それがどんな回路になるかを解説していきます。座学が終わりやっと「手を動かす」内容になります。

東工大 佐藤真平