愛知工業大学の藤枝です。2020年第1クォーター (20Q1) のコース「シリアル通信で Hello, FPGA」に引き続き、FPGA 上のディジタル回路設計の基本を学ぶコースを担当します。

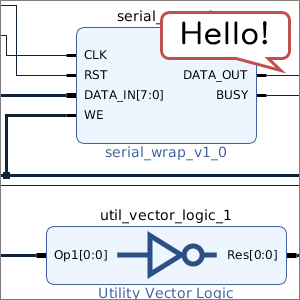

このコースでは、「シリアル通信で Hello, FPGA」で作成した文字送信回路をパッケージ化して、他の回路やチップ内のプロセッサと組み合せて使う方法について学びます。先のコースの最後で、作り込んだ回路のパーツは貴重な財産 (Interectural Property) である……と書きましたが、まさにこのようなパッケージ化された回路のことを IP (Interectural Property) コアといいます。Vivado には IP コアを組み合せてより大きな回路やシステムを設計する IP インテグレータという機能があります。この機能を使った開発手順をひととおり理解し、様々な方法で「Hello, FPGA」を PC に送信することが、このコースの目標となります。

(注: ネットワークの世界で IP というと Internet Protocol が思い浮かびますが、それとは違う用語です)

IP インテグレータとは

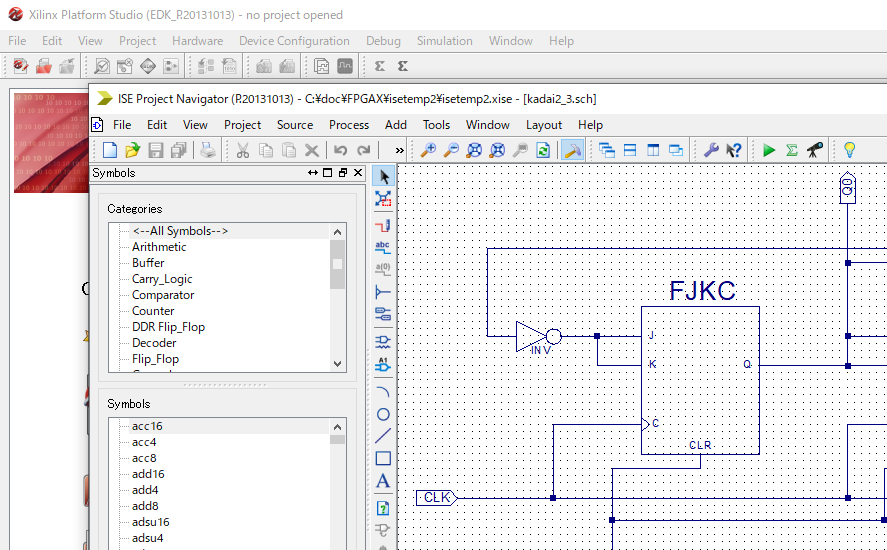

Xilinx の旧世代の FPGA 向けには、 ISE という開発ツールがありました。ISE には回路図エディタ機能があり、簡単な論理回路を学習するときや、作った回路同士を接続するときなど、HDL を使うまでもない学習や設計をするのに便利でした。また、ISE には、回路設計用の Logic Edition に加え、Embedded Edition という組込み開発向けのエディションがあり (Vivado では Design Edition に統合されました)、そこでは Platform Studio というツールでプロセッサと IP コアを組合せた設計を行えました。

IP インテグレータは ISE 時代の Platform Studio の後継ツールで、回路図 (ブロック図) ベースのインタフェースを使って、複数の IP コアを使った複雑なシステムを直感的に設計するためのツールです。基本的にはプロセッサを含んだシステムの設計に使われることが多いのですが、作った回路同士を接続してより大きな回路を作成する、といった用途にも使うことができます。

ただ、残念ながら ISE の回路図エディタの頃ほど自由な設計はできません。IP インテグレータでの設計における部品はあくまで IP コアなので、フリップフロップなどの基礎的な論理素子は含まれていません。こうした基礎的な論理素子を使った設計を行いたい場合は、Deeds などの HDL へのエクスポートに対応した回路図エディタを使うことになるでしょう。

このコースでは、第2~3回でプロセッサを含まない回路の設計・動作確認を行ったあと、第4~5回でプロセッサを含んだシステムについて扱います。

IP インテグレータで利用できる IP コアの例

まずは IP カタログを見てみよう

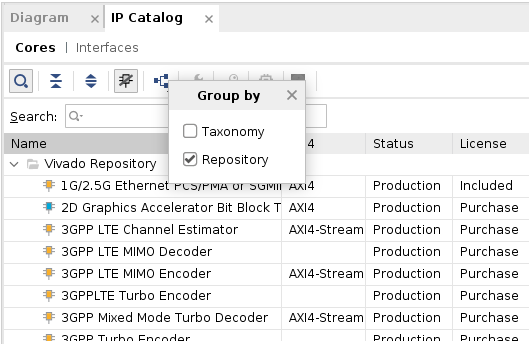

IP インテグレータで利用できる IP コアの一覧は、Vivado のプロジェクトを作成した後で参照できる、IP カタログという画面で確認できます。Vivado を起動し、適当なプロジェクトを作成し (あるいは既存のプロジェクトを開き)、画面左側の Flow Navigator から「Project Manager → IP Catalog」をクリックすると、IP カタログが右上の画面に表示されます。

デフォルトでは、IP コアは用途別に表示されます。もし用途に関係なく一覧で表示したければ、上図のようにツリー状のアイコン (左から5番目) をクリックし、Group by Taxonomy のチェックを外します。

この一覧の中で、AXI4 という列があり、一部の IP コアには AXI4 または AXI4-Stream (またはその両方) の記述があるかと思います。これは、IP コアが AXI (Advanced Extensible Interface) という、プロセッサを含んだシステムでよく利用される接続インタフェースを含んでいるかを示しています。つまり、この列の記載のある IP コアは、プロセッサから容易にアクセスできる可能性が高いです。

このコースの後半でも、AXI4 インタフェースを含み、プロセッサからアクセス可能な IP コアをテンプレートから作成していきます。もちろん、AXI のインタフェースごと自作することもできますが、その方法については別の機会 (コース) で紹介することにしましょう。

また、IP カタログにリストアップされている IP コアでも、必ずしも利用できるとは限りません。License の列が Purchase となっている IP コアは、利用のために Vivado とは別にライセンスの購入が必要です。制限つきの評価版ライセンスが一定期間無償で利用可能な場合もありますので、各 IP コアの製品ガイド (IP カタログ上で右クリック→ Product Guide) を確認してください。License の列が Included となっている場合は、ライセンスが Vivado に含まれており、追加のライセンス購入は不要です。また、まれに Free となっているものもあります。これも無償で利用できます。

それではここからは、IP カタログから IP コアの例をいくつか見てみましょう。

プロセッサ

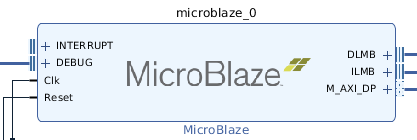

先述したとおり、IP インテグレータはプロセッサを含んだシステムの設計に使われることが多いので、まずはプロセッサから紹介します。

Xilinx の FPGA では、Xilinx 謹製のソフトプロセッサ (FPGA 上に実装可能なプロセッサ) である MicroBlaze がよく使われます。資料も Xilinx 社のサイトからダウンロードできます。標準では5段のパイプライン (3段・8段も選択可) をもつ、いかにも典型的な RISC プロセッサといったところです。このコースでも第4回以降で MicroBlaze を使用していきます。

また、20Q1 のコース「PYNQ を使って Python で手軽に FPGA を活用」でも扱われた PYNQ-Z1 など、Zynq シリーズを搭載したボードを使っているのであれば、ZYNQ Processing System もリストアップされていることでしょう。これを IP インテグレータに貼り付ければ、Zynq に搭載されたハードウェアのプロセッサ (PS; Processing System) 部分が利用可能になります。

Zynq を使うような規模のシステムではないが、既に ARM での開発に慣れているという場合であれば、Arm 社が DesignStart FPGA プログラムで無償提供している Cortex-M1, Cortex-M3 の IP コアを使用するという方法もあるかもしれません。

クロック信号の生成

詳しいことは第3回で説明しますが、MicroBlaze を使おうとするとその周辺にメモリやデバッグ回路などの様々な回路が必要となります。その中には、「FPGA をもっと活用するために IP コアを使ってみよう (3)」でも紹介されていた、Clocking Wizard が含まれます。

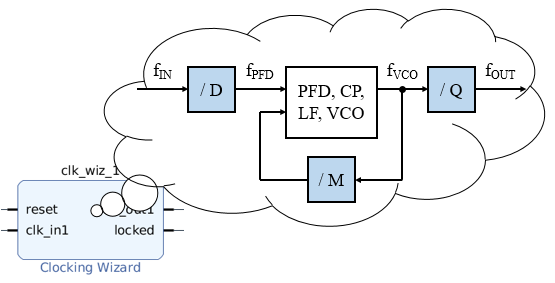

Clocking Wizard の中身は MMCM (Mixed-Mode Clock Manager) という、FPGA 内部の高性能なクロック生成器になっています。基本的な動作は一種の PLL (位相同期回路) であり、位相周波数比較器 (PFD)、チャージポンプ (CP)、ループフィルタ (LF)、電圧制御発振器 (VCO)、およびいくつかの分周器を用いて、必要な周波数のクロック信号を生成します。

プロセッサと周辺回路で別々のクロック信号が必要な場合などは、この Clocking Wizard を編集します。適当な周波数を得るための分周器のパラメータ (上図の D, M, Q) を自動的に求め、適当なパラメータをもつ MMCM を作成してくれます。パラメータを自力で設定すれば MMCM を直接インスタンス化することもできるのですが、生成途中の信号の周波数 (上図の fPFD や fVCO) にも制約があったりして、何かと面倒です。通常の用途であれば、Clocking Wizard を使うのが良いでしょう。

なお、Zynq を使う場合にはクロック信号の生成は PS が行いますので、PS の設定を変更することになります。

HDMI を扱う

PYNQ-Z1 や Nexys Video など、HDMI の入出力端子をもち、動画処理のアプリケーションを実現可能なボードでは、HDMI の信号の扱いにも IP コアを使います。

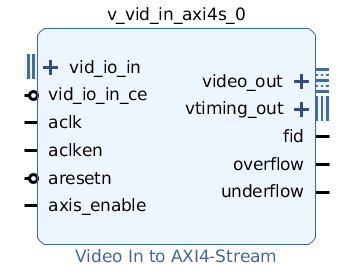

これらのボードで HDMI の入力を受け取る場合、典型的には (1) HDMI (DVI) のシリアル信号を 24-bit RGB のパラレル信号に変換し、(2) それをさらに AXI Stream インタフェースの信号に変換し、(3) DMA (Direct Memory Access) で特定のメモリ領域に書き込む、という流れを経ます。これらのそれぞれに対応する IP コアがあり、上図はこのうちの (2) の IP コアを示したものです。出力の場合はこの逆の流れになります。

なお、(1) に対応する IP コアは、これらのボードを製造販売している Digilent 社がオープンソースで公開しています。入力側が dvi2rgb、出力側が rgb2dvi です。「PYNQ を使って Python で手軽に FPGA を活用 (4)」で紹介されている PYNQ-Z1 のサンプルデザインでもこれらが利用されています。もしこういったアプリケーションを作成したければ、サンプルデザインを分析・改造するところから始めると良いでしょう。

その他の便利な IP コア

これ以外にも様々な IP コアが IP インテグレータから利用できます。「FPGA をもっと活用するために IP コアを使ってみよう」では上述の Clocking Wizard の他にも、いくつかの IP コアを HDL ベースの設計で使う方法について扱っていました。もちろん、それらも IP インテグレータから利用できます。

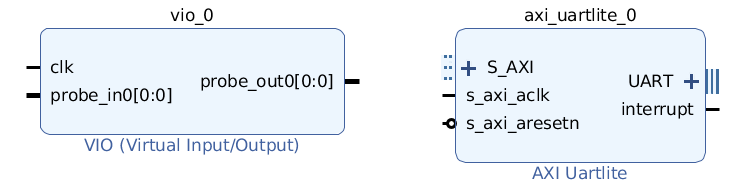

VIO (仮想I/O) を使えば、入力の操作や出力の確認が Vivado の Hardware Manager 経由で行なえます。また、今回のコースでは扱いませんが、UART での送受信をプロセッサから手軽に行いたければ、AXI インタフェースを使った AXI Uartlite を使うとよいでしょう。

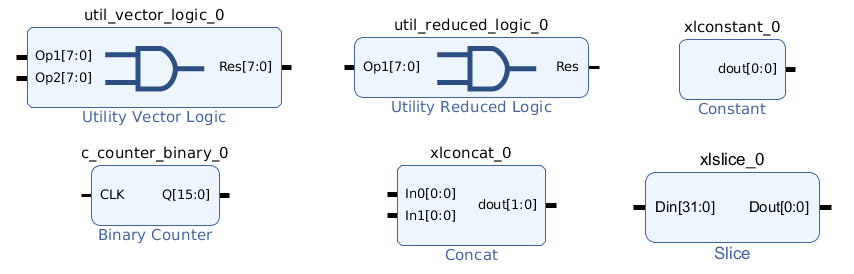

また、IP コア同士で信号をただ接続するのではなく、ちょっとマスクをかけ (一部のビットだけを ‘0’ や ‘1’ に設定し) たり、連結・分割したりする必要が生じることもあるでしょう。この場合には、各種の基本的な IP コアやユーティリティ IP コアを使うのが便利です。

例えば論理演算には、複数ビットの論理演算のための Utility Vector Logic、リダクション演算を行う Utility Reduced Logic があります。定数を出力する Constant という IP コアもありますので、これを Utility Vector Logic と組み合わせれば、信号にマスクをかけられます。例えば、16ビットの信号の下位8ビットだけを ‘0’ に設定したければ、定数 0xFF00 との AND を取ればよい、といった具合です。また、カウンタ回路に対応する Binary Counter も用意されています。第3回ではこれらの IP コアを活用していきます。

なお、信号を連結するには Concat、分割するには Slice の IP コアを使用します。

まとめ

今回は、IP インテグレータの紹介とその上で使用できる各種の IP コアの例を見てきました。今回のポイントは以下のとおりです。

- IP インテグレータは、ブロック図を使って複数の IP コアを使った複雑なシステムを直感的に設計するツールである。

- Vivado では、プロセッサやクロック生成、周辺機器との入出力など、様々な IP コアが利用できる。

ここで紹介した IP コアを使いこなすのももちろん大切ですが、専用システムを作成するためには IP コアを自作し、それを既存の IP コアと組み合わせて使う方法を知る必要があります。次回は、「シリアル通信で Hello, FPGA」で作成した文字送信回路をパッケージ化し、自作の IP コアとして使用する方法を解説します。

愛知⼯業⼤学 藤枝直輝