IP インテグレータを用いた回路やシステムの設計について学ぶコースの第2回です。前回は、IP インテグレータの概要と、いくつかの既存の IP コアの例を見てきました。今回は、自作の IP コアをこれら既存の IP コアと組み合わせて使うために、IP パッケージャというツールの使い方を学びます。

今回の内容に関する Xilinx 社の公式ドキュメントの文書番号は UG1118 となります。詳細な仕様などは上記ドキュメントを参照してください。

IP コア作成の下準備

IP コア作成のメリット

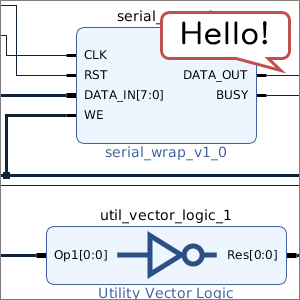

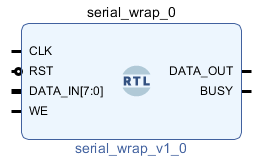

単に、HDL で書かれた簡単な回路を IP インテグレータで使いたいだけなら、「Vivado でのブロック図設計」の記事に示された方法で HDL で記述されたモジュールをそのままブロック図に貼り付けることができます。この方法で貼り付けられたモジュールの例を下図に示しますが、中央に RTL (レジスタ転送レベル Register Transfer Level の略です) という文字列が表示されます。

これはこれで手軽で良いのですが、今回学ぶ方法で回路を IP コア化すると、以下に例示するようなメリットを受けられます。

- ファイル一式を収めたディレクトリをリポジトリに追加するだけで、回路が利用可能になる。

- テストベンチなど、回路設計以外のファイルをまとめてパッケージングできる。

- より柔軟でわかりやすいパラメータの設定方法を提供できる。

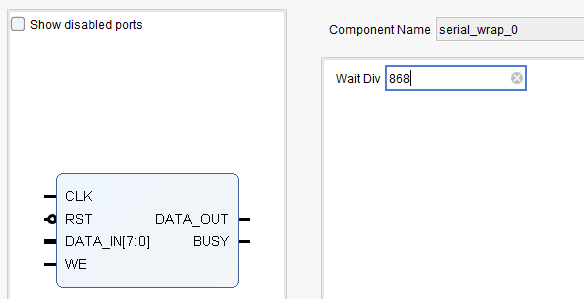

第1・第2のメリットは、開発効率 (生産性) の向上という意味で重要です。また、第3のメリットに関しては、確かに上述の方法で貼り付けたモジュールでも、SystemVerilog の parameter 文や VHDL の generic 文で指定したパラメータを直接書き換えることはできます (下図参照)。IP パッケージャでパラメータ設定を適切に変更すると、パラメータの説明を付加したり、選択範囲を限定したりといったカスタマイズが可能になります。

Verilog HDL によるラッパの作成

SystemVerilog で回路を記述している場合、IP パッケージャを使う前に Verilog HDL を用いたラッパ回路をあらかじめ用意しておく必要があります。VHDL や Verilog HDL を使用している場合には、この作業は必要ありません。

残念ながら、この記事を書いている時点のバージョンの IP パッケージャは、SystemVerilog で記述されたモジュールを IP コアのトップモジュールに設定できません。一方、20Q1 のコース「シリアル通信で Hello, FPGA」では、シリアル通信による文字送信回路を SystemVerilog で記述しました。そのため、文字送信回路に対するラッパとして、以下のような Verilog HDL で書かれたソースファイル (ここでは serial_wrap.v とします) を用意しておきます。

module serial_wrap (

input wire CLK, RST,

input wire [7:0] DATA_IN,

input wire WE,

output wire DATA_OUT,

output wire BUSY);

parameter WAIT_DIV = 868;

serial_send #(.WAIT_DIV(WAIT_DIV))

ser (CLK, RST, DATA_IN, WE, DATA_OUT, BUSY);

endmodule10行目でインスタンス化されている serial_send は、先のコースの第2回で示した serial_send.sv の記述そのままです。SystemVerilog では論理値を logic で表していましたが、Verilog HDL では配線を wire で表します (この他に、レジスタや always 文の出力に対応する reg があります)。そのため、入出力を logic のかわりに wire で宣言し (2~6行)、パラメータを宣言し (8行)、これらを SystemVerilog で記述されたモジュールに接続します (10~11行)。

IP パッケージャの起動

パッケージの対象を選ぶ

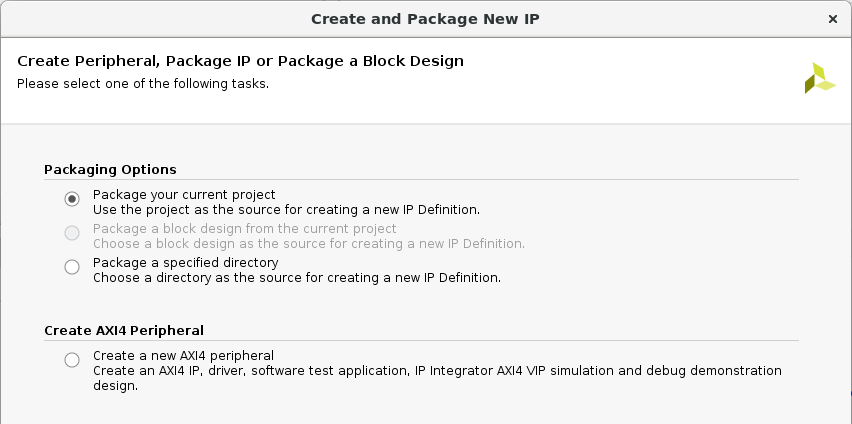

IP パッケージャは、Vivado で何らかのプロジェクトを開いている状態で、メニューの「Tools → Create and Package New IP」を選択すると起動できます。

IP パッケージャでの IP コア作成法には、上図の上から順に (1) 現在のプロジェクトをパッケージする、(2) 現在のプロジェクト内にあるブロック図をパッケージする、(3) 必要なファイル一式の含まれたディレクトリをパッケージする、(4) AXI4 インタフェースを含んだテンプレートを作成してパッケージする、の4通りがあります。現在のプロジェクトでブロック図が作成されていない場合、(2) はグレーアウトされます。

この記事では (2) を除く3つの方法を順番に説明したあと、共通の手順として IP コアのパッケージの方法を説明します。

既存プロジェクトをパッケージする場合

最初に説明するのは、既存のプロジェクトをパッケージする方法です。一般的には、回路を IP コアとしてパッケージする前に、シミュレーションで動作確認したり、正しく論理合成ができるか確認したりすることでしょう。その時のプロジェクトを開いた状態で IP パッケージャを実行すると、プロジェクトの内容をもとに IP コアが作成できます。

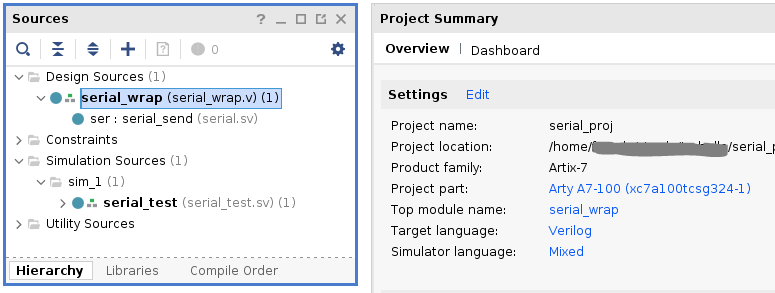

今回は、シリアル送信回路のシミュレーションによる動作確認が完了したことを想定して、このときのプロジェクトをもとに IP コアを作成してみます。プロジェクトの対象ボード (パーツ) は Arty A7-100 に設定されており、プロジェクトには Design Source(s) としてシリアル送信回路 (serial_send.sv) と先ほどのラッパ (serial_wrap.v) が、Simulation Source(s) としてシリアル送信回路のテストベンチ (serial_test.sv) が、それぞれ追加されているものとします。この時のプロジェクトの様子を下図に示します。

メニューの「Tools → Create and Package New IP」で IP パッケージャを起動し、最初の画面で Next を押すとパッケージ方法の選択画面 (上述) が出てきます。ここでは、1番上の「Package your current project」を選択します。

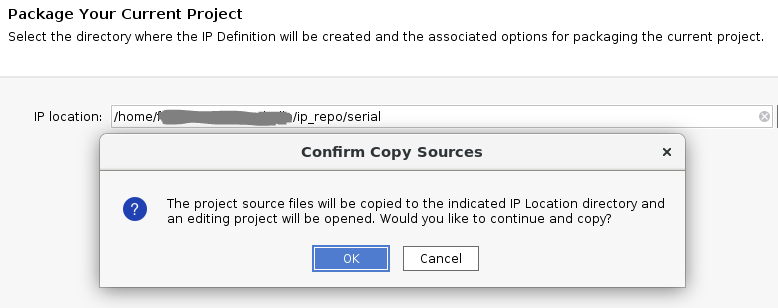

次の画面で IP コアをどこに保存するかを尋ねられます。一般的には、自作の IP コアをまとめたディレクトリ (ユーザリポジトリ) を作成し、その下に個々の IP コアのディレクトリを置く場合が多いです。そのため、今回はプロジェクトのディレクトリとは別に ip_repo/serial というディレクトリを作成し、そこに IP コアを保存することにします。

指定したディレクトリによっては、ソースファイルをコピーするかどうかの確認が表示されますので、OK を押します。以後、ソースファイルを修正する必要がある場合には、プロジェクト上のファイルではなく、このコピーされたファイル (通常、指定したディレクトリの中に src などのディレクトリが作られます) を修正することになるので、注意してください。更に画面を進めると最終確認の画面が現れますので、Finish ボタンを押します。

この後、必要なファイルの作成・コピーなどの処理が終わると、Vivado のウィンドウがもう1つ表示されます。以降の説明は次章で行います。

ディレクトリをパッケージする場合

次に説明するのは、必要なファイル一式の含まれたディレクトリをパッケージする方法です。ひと通り開発を進めた後、改めてファイル一式を整理してから IP コアを作成したい場合には、この方法を取ったほうが楽でしょう。

この方法では、まずパッケージするディレクトリの下に用途別のディレクトリを作ります。例えば、Design Source(s) に相当する回路設計は src (または hdl) ディレクトリ、Simulation Source(s) に相当するテストベンチは test (または testbench, tb) ディレクトリ、といった具合です。ソースファイルをこれらのディレクトリにまとめて置いておくと、IP パッケージャが自動的に用途を認識してくれます。

今回は、文字送信回路とそのラッパ、テストベンチを含んだディレクトリをパッケージしてみます。適当なディレクトリを作成し、その下に src と test の2つのディレクトリを作成します。ファイルの構成は以下の通りとなります。

| 用途 | モジュール名 | ファイル名 |

|---|---|---|

| 文字送信回路 | serial_send | src/serial_send.sv |

| ラッパ | serial_wrap | src/serial_wrap.v |

| テストベンチ | serial_test | test/serial_test.sv |

メニューの「Tools → Create and Package New IP」で IP パッケージャを起動し、最初の画面で Next を押すとパッケージ方法の選択画面 (上述) が出てきます。ここでは、3番目の「Package a specified directory」を選択し、次の画面で作成したディレクトリを選択します。この画面の「Packaging as a library core」のチェックが外れていることを確認します。

次の画面では一時的なプロジェクトの保存場所を指定できますが、通常は変更せずに Next ボタンを押します。更に画面を進めると最終確認の画面が現れるので、Finish ボタンを押します。

ファイルの解析や必要なファイルの作成などの処理が終わると、Vivado のウィンドウがもう1つ表示されます。以降の説明は次章で行います。

テンプレートを作成してパッケージする場合

第1回でも説明しましたが、IP コアをプロセッサから容易にアクセスするために、AXI4 という接続インタフェースがよく用いられます。IP パッケージャには、AXI4 インタフェースを含んだ IP コアをテンプレートから作成する機能もあります。テンプレートの内容やその改変については第4回で扱う予定ですので、ここではまずは IP パッケージャの利用の流れだけ見ていきます。

メニューの「Tools → Create and Package New IP」で IP パッケージャを起動し、最初の画面で Next を押すとパッケージ方法の選択画面 (上述) が出てきます。ここでは、1番下の「Create a new AXI4 peripheral」を選択します。

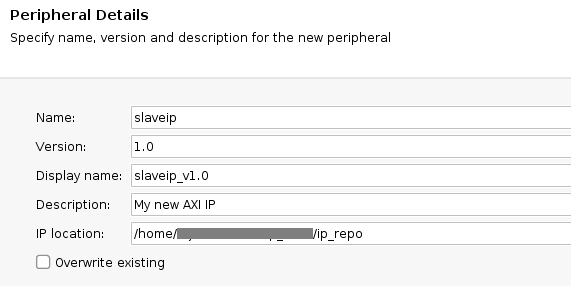

下図に示す IP コアの名前や保存先などを設定する画面が表示されます。IP コアは、IP location で指定したディレクトリの下に新たに作成される、[Name]_[Version] というディレクトリに保存されます。例えば下図の例であれば slaveip_1.0 となります。Display name と Description は IP カタログに表示される表示名と説明ですので、必要があれば変更します。

次の画面では作成する IP コアにどのようなインタフェースを持たせるかの設定を行います。デフォルトでは、AXI4-lite のスレーブモード (プロセッサ等から発行されたコマンドを受け取って動作するモード) のインタフェースが1つ作成される設定になっています。今は変更せずに Next を押します。

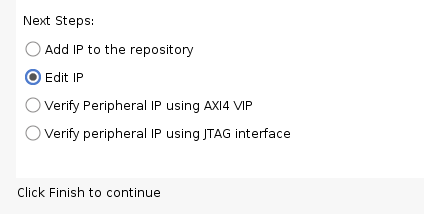

最終確認の画面が現れます。下図に示す通り、IP コアが作成された後に行う操作を選択できますので、Edit IP を選択してから、Finish ボタンを押します。

テンプレートの作成などの処理が終わると、Vivado のウィンドウがもう1つ表示されます。

IP コアのパッケージ

これまで紹介したどの方法で IP パッケージャを起動した場合でも、最終的には Vivado のウィンドウがもう1つ表示されます。通常は、右上のメイン画面に下図に示す Package IP という画面が表示されているかと思います。こちらの画面で、IP コアのパッケージに必要ないくつかの手順が案内されます。

確認・変更の必要のない項目にはあらかじめチェックマーク (✓) が、確認が必要な項目には注意マーク (!) が表示されます。それぞれの項目について簡単に紹介します。

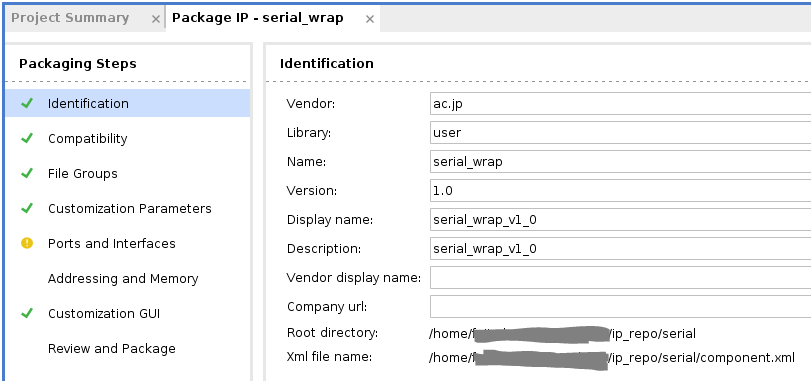

- Identification: IP コアの名前を指定します。正式名称は [ベンダー名]:[ライブラリ名]:[コア名]:[バージョン] という形でつけられます。例えば、上図の通りであれば ac.jp:user:serial_wrap:1.0 が正式名称です。また、Display name が IP カタログに表示される表示名となります。管理上必要があれば変更します。

- Compatibility: FPGA ファミリとの互換性を指定します。互換性のない IP コアは IP カタログ上で非表示になります。デフォルトでは Vivado で扱える全ての FPGA と互換性をもつように設定されますが、もしそうでない場合は変更します。

- File Groups: ファイルの一覧が用途別に表示されます。念のため、誤って認識されていないか確認しておくとよいでしょう。

- Customization Parameters: 設定できるパラメータや、その変更方法を確認・変更できます。通常、トップモジュールの parameter 文 (VHDL では generic 文) で指定したパラメータが表示されます。

- Ports and Interfaces: トップモジュールの入出力ピンの用途を確認・設定します。通常クロック・リセット入力は自動認識されます。AXI4 インタフェースを使わない場合には注意マークが表示されますが、無視して構いません。

- Addressing and Memory: AXI4 インタフェースを使う場合には、ここでアドレス空間を設定します。使わない場合には何もする必要はありません。

- Customization GUI: 上記の Customization Parameters を設定するためのダイアログのレイアウトを指定します。

今回は、「既存プロジェクトをパッケージする場合」または「ディレクトリをパッケージする場合」のいずれかの方法で、文字送信回路をパッケージする手順に進んだ場合について説明します。

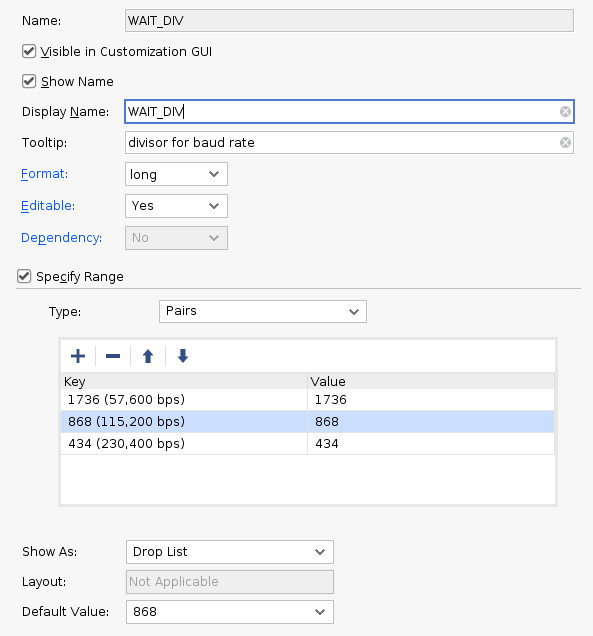

Ports and Interfaces についている注意マークは無視できますので、そのまま1番下の Review and Package に進んでも構いません。ただ、せっかくですのでパラメータの変更方法を修正してみましょう。Customization Parameters を選択し、WAIT_DIV をダブルクリックすると,パラメータの変更方法を指定する画面が表示されます。

Display Name、Tooltip の各欄は、パラメータ変更の画面で表示される見出し (表示名) と、マウスオーバー時に表示される説明 (ツールチップ) となります。

好きなパラメータ値を入力させるのではなく、いくつかの候補の中から選択させたい場合には、Specify Range にチェックを入れ、Type を Pairs に設定します。その下に表がありますが、Key の列が画面上で表示される項目名、Value が実際の値になります。なお、Key と Value が一致する場合は、Type に List of Values を選択しても構いません。

ここでは上図に示すように、あらかじめ設定していたパラメータ868 (115,200 bps に相当) のほかに、その2倍の1736 (57,600 bps) と1/2倍の434 (230,400 bps) も選択できるようにしてみます。

全ての項目の確認・変更が済んだら、IP のパッケージを完了させます。項目の1番下にある Review and Package をクリックします。確認画面が表示されますので、確認の上 Package IP ボタンを押すと、パッケージが完了します。

パッケージが問題なく完了すると、一時的なプロジェクト (つまり、パッケージに使った Vivado のウィンドウ) を閉じてよいか確認されるので、Yes を押してプロジェクトを閉じます。最終的に、作成したディレクトリ内のファイルの構造は以下の通りとなります。

| 用途 | ファイル名 |

|---|---|

| IP コアの定義 | component.xml |

| Customization GUI の設定内容 | xgui/serial_wrap_v1_0.tcl |

| 文字送信回路 | src/serial_send.sv |

| ラッパ | src/serial_wrap.v |

| テストベンチ | src/serial_test.sv ※ |

※ 「ディレクトリをパッケージする場合」の手順では、test/serial_test.sv。

この時作成された component.xml に、先ほどの設定項目のほとんど全てが記載されています。実は、最初に示した HDL で記述されたモジュールをそのままブロック図に貼り付ける方法でも、裏ではこの component.xml が貼り付けたモジュールに対して作成されているのです。

作成されたファイルを直接編集することはできません (チェックサムがあります) が、ファイルの中身を眺めれば、先ほど見てきた項目の情報が含まれていそうだという雰囲気は掴めるでしょう。

まとめ

今回は、自作の IP コアを作成するための IP パッケージャの使い方を見てきました。今回のポイントは以下のとおりです。

- IP パッケージャでは、既存のプロジェクト、ブロック図、ディレクトリを指定して、回路を IP コアへとパッケージできる。

- IP パッケージャには、AXI4 インタフェースを含んだ IP コアのテンプレートを作成する機能もある。

- パッケージ中の手順で Customization Parameters の項目を設定することで、パラメータの設定画面に説明を加えたり、選択できる値を限定したりできる。

次回は、今回作成した文字送信回路の IP コアを使って、ブロック図を使った設計で「Hello, FPGA」を PC に送信する回路を作成していくことにします。

愛知工業大学 藤枝直輝