みなさんこんにちは。このコースでは、「非同期式回路」というものはいったいどんなものなのか、FPGA に実装したらどうなるのか、ということを非常に大雑把に紹介していきたいと思います。ある簡単な例題を非同期式回路として FPGA 上に実装し、ツールを適切に使うことで、正しく動作するものを作ってみる、ということ目指したいと考えています。

まず、第一回は「非同期式回路の超入門」と題し、非同期式回路のざっくりとしたイメージを紹介します。

非同期式回路の超入門

非同期式回路とはいったいどのようなものでしょうか。非同期通信などのなじみのある用語と同じ「非同期」という言葉が使われていますが、何が非同期かに関して、非同期通信などとは似て非なるものです。

非同期式回路は、先頭に「非」という文字が付いている通り、「同期式回路」ではない回路、ということになります。では、同期式回路であるとはどういうことでしょう。よくパソコンなどの性能を話すときに、例えばこのパソコンのクロックは3.5GHzだ、とか言うと思います。このクロックというものが同期式回路において非常に重要な働きをしています。すなわち、同期式回路とは、クロック信号により実行制御している回路、ということができます。

クロック信号とは

では、クロック信号とは具体的にどのようなものでしょう。次の図は、IC チップ上の信号変化の様子を可視化したものです。

緑の枠が、5mm×5mm 程度の IC チップを表しています。便宜上、「コア」と示した小さな箱 (チップ内に16個配置されています) に計算をする要素があるものと思ってください。この可視化では、左下のコアから右上のコアに、また、逆に右上のコアから左下のコアにデータを送るという状況を示しています。これは、実際の回路を非常に精密にシミュレーションした結果に基づいたものです。

この中でとても目立っている赤い信号、これがクロック信号です。一方、青い信号は、データ信号などを表しています。データ信号は、クロック信号が何回か届くごとに次々と送り出されていく様子がわかるかと思います。

ここで、注意すべき点が二つあります。まず、電気信号は非常に高速に伝わりますが、それでもクロック信号が伝わるのは時間がかかり、クロック信号のチップへの入力端子 (最下列左から2つ目のコアの下側のチップ端部分) で変化しても、それが各コアまで伝わるのには、少し時間がかかっていることがわかると思います。

しかし、データを正しく送受信するには、クロック信号は各素子に同時に到着しなくてはならない、という制約があります。そのため、クロック信号は図のような非常に複雑なルートを通して分配されていて、よく見るとわかると思いますが、チップのクロック入力端子とコアのクロック入力部分には時間差がありますが、コア間でのクロック信号到達タイミングはまったく同じに見えると思います。この複雑なクロック信号伝搬ルートはこの制約のために考え出されたものなのです。

もう一つは、内側の4つのコアに関してです。これらは、この可視化のタイミングではデータの送受信などの動作はしていないのですが、それにもかかわらず、クロック信号は供給されています。これは、いつ動作が必要になるかわからないので、あらかじめ止めておくことが難しいからです。

クロック信号の良いところと悪いところ

さて、このようなクロック信号ですが、良いところと悪いところがあります。まず、良いところですが、クロック信号というのは、回路の素子に同時に到達するという性質を持つので、それにより回路の設計が簡単になります。また、もう長年、この設計方法が続けられてきたので、設計を支援するツールや、これまでの設計資産が豊富である点も挙げられます。

でも、悪いところもあります。クロック信号に関わる消費電力が大きいという点です。

まず、クロック信号の同時性の保証ですが、クロックの高速化とともに難しくなり、その保障のためにクロック分配に大きな電力が必要となります。また、動作していない素子にも供給しています。それから、先ほどの可視化でもわかったと思いますが、クロック信号は常に忙しく変化しています。IC チップの消費電力は、大雑把に言うと信号の変化の回数に比例するので、クロック信号に関わる消費電力だけで、場合によっては全体の半分以上になることもあります。これらは、ある意味、クロック信号に基づく同期式という方式の限界ということができます。

そこで、その限界を超えたい、というのが非同期式回路の研究のモチベーションです。非同期式回路は大きな可能性を秘めています。なぜなら、非同期式回路はクロック信号を一切使わない回路方式だからです。クロック信号がなければ、さきほどのような問題が起こらないのは明らかです。ただ、先ほど述べたように、クロック信号は実行の制御に重要な役割を果たしているわけで、それを使わずに実行制御をするには工夫が必要です。

非同期式回路の実行制御

まず、同期式の場合の実行制御のおさらいです。下の図のように、クロック信号が何回か変化することで、データが伝送されて行きます。

一方の非同期式回路では、クロック信号の代わりに要求信号と応答信号を用います。下の図のように、データが到達したら、要求信号を送り、レジスタに取り込みます。次に、取り込んだことを送信元に応答信号で知らせるとともに、次の送り先にデータを送り、その後、要求信号を出します。このような実行制御をハンドシェイクといいます。

ここで注意してほしいのは、このようなハンドシェイクは、実際にデータの送受を行う素子間のみで行う、ということです。データのやり取りを行う以外の素子とは、ハンドシェイクは必要ありません。ですから、動作しない素子やコアには何ら信号を送る必要はありません。

下の図は、先ほどと同じ動作を行う回路を、非同期式で構成した例です。赤いのが、クロック信号の代わりを務める、要求・応答信号です。これからわかるように、動作が必要な素子間のみで信号の受け渡しが行われています。

非同期式回路の特徴

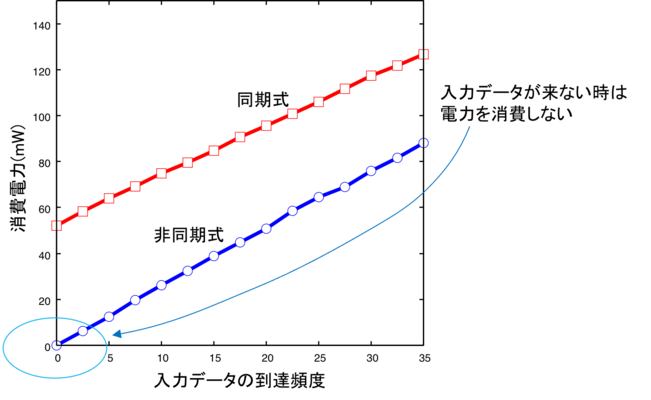

下の図は、先ほどの同期式回路と非同期式回路の消費電力を、やはり詳細なシミュレーションにより求めた結果です。

横軸は、入力データの到達頻度で、コア間のデータ送信がどれほど頻繁に起こるかに関係します。頻繁にデータ転送を行えば、消費電力が増えるのは当然なのですが、注目していほしいのは、非同期式では、入力データが来ないときは、ほとんど電力を消費しない、という点です。この場合の同期式の電力は、クロック分配のみに関わる電力と見ていいと思います。なお、この両方式の処理速度はほぼ同じなので、この例では、非同期式が優れていると言えます。

一般的に言うのは難しいですが、強いて言うと、非同期式回路は「まばらな処理」を効率よく扱うのが得意、と言えるかもしれません。処理が必要ないときは、自然に電力がセーブされるのです。逆に、連続的な処理は同期式回路の方が高効率のこともあります。

それらのいいとこ取りをした方式として、大域非同期・局所同期方式 (Globally Asynchronous Locally Synchronous: GALS) があります。これは、小〜中規模の回路で、連続した処理をするような部分を同期式回路で作り、それらを接続する部分、これは、まばらな処理になるといいのですが、そこを非同期式回路で作る、という考え方です。

もちろん、非同期式回路の設計にも課題がたくさんあります。まず、同期式回路の逆で、まだ設計ツールが整備されていません。また、設計の考え方が「何かが起こったら、次にこれが起こる」というような、イベント駆動の考え方で設計することが多く、同期式のクロックに基づくものと考え方が大きく異なります。ですので、とっつきにくく、普及していないと言う面もあると思います。

まとめ

今回は、非同期式回路の超入門と題して、非同期式回路とはどのようなものか、という点に焦点を当てて、ざっくりと紹介しました。

次回は、非同期式回路の実行制御のかなめとなる「ハンドシェイク」について少し詳しく紹介し、第3回での例題回路の設計につなげたいと考えています。

国立情報学研究所 米田友洋