20Q3.01B

20Q3.01BAXI でプロセッサとつながる IP コアを作る (5)

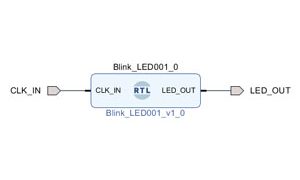

AXI を使ってプロセッサと連携する回路の設計例について説明するコースも、いよいよ最終回となりました。今回は、前回作成したインタフェース変換回路を使い、専用計算回路 (コプロセッサ) の一例としてステンシル計算コプロセッサを作成し、C 言語によるソフトウェア実装と性能を比較してみます。 なお、第4回~第5回で使用する回路の SystemVerilog 記述は、GitHub からダウンロードできるようにしています。今回は、主に stencil/hdl/stencil_opt.sv を取り上...