20Q2.09B

20Q2.09BMIG を使って DRAM メモリを動かそう (5)

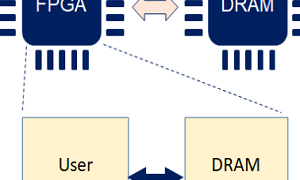

この記事では、DRAM ベースの設計のためのシミュレーション方法を解説していきます。説明では、Synopsys 社のシミュレータ VCS を使用し、前回の記事で実機の FPGA ボードで動かしたテストプログラムと RISC-V ソフトプロセッサのシミュレーションを行います。 ソースコード: テストプログラム: ソフトプロセッサ: 概要 FPGA の設計において、シミュレーションは不可欠です。簡単な回路を設計する場合は、一発で実機で動かせることがありますが、ほとんどの...