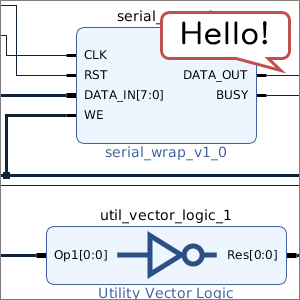

IP インテグレータを用いた回路やシステムの設計について学ぶコースも、いよいよ今回が最終回です。前回は、文字送信回路の IP コアを MicroBlaze と組み合わせるための IP コアを作成し、これらを含むブロック図からシステムを合成しました。今回は、このシステムの上で動作するソフトウェアを記述し、動作確認を行います。

なお,今回の内容は基本的に Vivado/Vitis 2019.2 を対象に記述しています。2019.1 以前の Vivado では、こうした FPGA 上の組込みプロセッサ向けの開発環境は SDK と呼ばれていましたが、2019.2 で AI 応用やアクセラレータ向けの機能を含んだ Vitis へと統合されました。SDK と Vitis とは概ね使い勝手は変わりませんが、一部の画面や操作方法が異なります。特に注意が必要な箇所は、SDK での操作方法も併記することにします。

Vitis での動作確認

プロジェクトの作成まで

Vitis は以下のいずれかの方法で起動します。

- スタートメニューから「Xilinx Design Tools → Vitis IDE (バージョン番号)」を選択 (Windows の場合)

- シェルで初期設定スクリプトを実行して PATH を設定してから、vitis を実行 (Linux の場合、ACRi ルームを使用する場合はマニュアルを参考に)

- Vivado のメニューから「Tools → Launch Vitis」 をクリック (OS 不問)

なお、2019.1 以前の Vivado のメニューから SDK を起動する場合は、「File → Launch SDK」を使います (Tools ではありません)。

もし該当するショートカットが見当たらなかったり、起動時にエラーが発生する場合には、そもそも Vivado をインストールした際に Vitis をインストールしていない可能性があります。別途インストールしても良いですが、Vivado のメニューの「Help → Add Design Tools or Devices」から追加インストールできる場合もあります。

起動すると作業ディレクトリ (ワークスペース) を指定するよう促すダイアログが表示されます。適当な場所に新しいフォルダを作成し、そのフォルダを指定してください。

Vitis のメインウインドウが開いたら、まずはプロジェクトを作成します。厳密には、Vitis のプロジェクトにはプラットフォームプロジェクト、システムプロジェクト、アプリケーションプロジェクトの3種類があります。プラットフォームプロジェクトにはハードウェアの定義と、それらを動作させるためのソフトウェアである BSP (Board Support Package) が含まれます。アプリケーションは個々のアプリケーションプロジェクト上で開発していきます。複数のアプリケーションを同時に動作させる場合には、これらを1つのシステムプロジェクト上に置きます。

ただ、今回のコースの範囲ではこれらは全て1対1で対応することになります。そのため、ここではアプリケーションプロジェクトを作成しながら、対応するプラットフォームプロジェクトやシステムプロジェクトも一緒に作成することにしましょう。

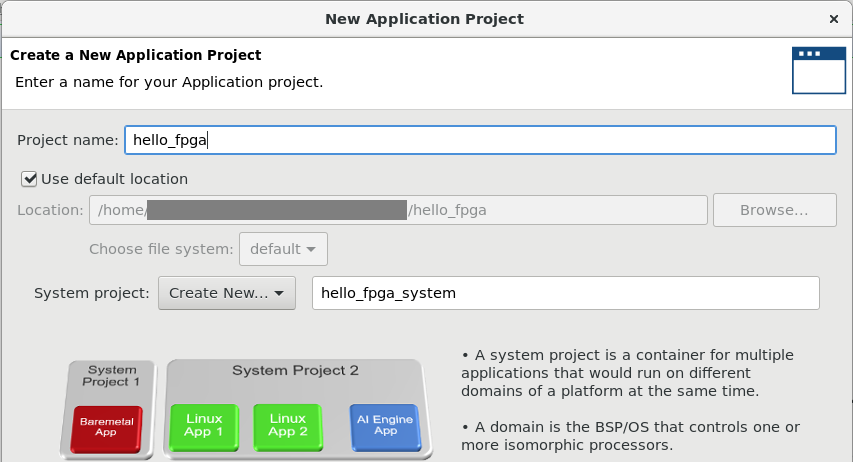

メニューの「File → New → Application Project」を選択すると、下図に示すプロジェクトの設定ダイアログが表示されます。

プロジェクト名を適当に設定します。ここでは hello_fpga としました。その他の設定は変更しませんが、この場合、自動的に hello_fpga_system というシステムプロジェクトも同時に作成されます。

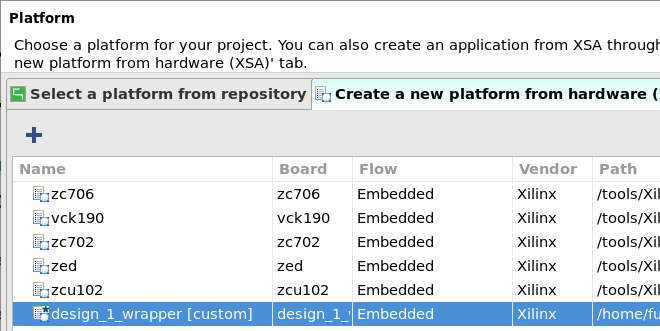

下図に示す次の画面では、プラットフォームの設定を行います。ここではプラットフォームプロジェクトも作成するので、「Create a new platform from hardware」のタブをクリックし、+ ボタンを押します。ファイルの選択ダイアログで、第4回 で作成した design_1_wrapper.xsa を指定すると、ハードウェアがリストに追加されます。これを選択して Next ボタンを押します。

3番目の画面 (Domain) では開発に使用する言語などを指定できますが、変更せずに Next を押します。4番目の画面 (Templates) ではプロジェクトのテンプレートを指定できます。ここではプログラムは全て自分で作成するので、「Empty Application」を指定し、Finish ボタンを押します。これまでの設定をもとに各種のプロジェクトが作成されます。

ソフトウェアの記述

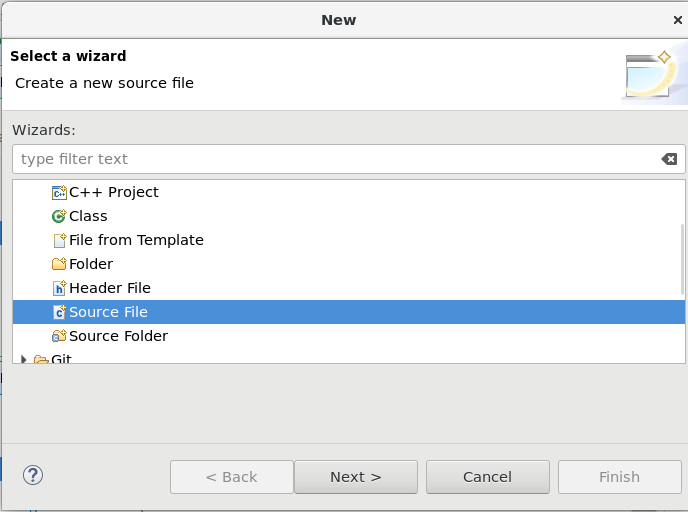

プロジェクトが作成できたら、作成したアプリケーションプロジェクト (hello_fpga) の下に src というソースコードを格納するためのディレクトリが作成されています。Vitis 上でこのディレクトリを選択した状態で、メニューの「File → New → Other」を選択すると、下図に示すファイル追加のダイアログが表示されます。

リストの C/C++ から Source File を選択し、Next ボタンを押します。次の画面でファイル名 (拡張子を含む) を指定して、Finish ボタンを押します。ここでは hello.c としました。

次に、このファイルに、文字送信回路を制御するためのソフトウェアを記述していきます。第4回 で作成した IP コアは、コアにとっての0番地のアドレスに文字を書き込むとその文字が送信でき、同じく0番地の最下位ビットが1であるかどうかを読み取ることで文字を送信中かどうかが判断できるように設計しました。これを踏まえて C 言語でソフトウェアを記述すると、例えば以下のようなコードになります。

#include "xparameters.h"

#define UART_CTRL (*(volatile unsigned int *) XPAR_SERIAL_TARGET_0_S00_AXI_BASEADDR)

int main () {

char *message = "Hello, FPGA\n";

char *ptr;

for (ptr = message; *ptr; ptr++) {

UART_CTRL = (unsigned int) *ptr;

while (UART_CTRL & 0x1) {}

}

return 0;

}

1行目では xparameters.h というヘッダファイルを include しています。このファイルは BSP に含まれているもので、どのメモリアドレスに IP コアを割り当てたかなどの情報を持っています。3行目の XPAR_SERIAL_TARGET_0_S00_AXI_BASEADDR という定数が定義されているのが、このヘッダファイルです。なお、3行目の define は、特定のメモリアドレスへの読み書きを通常の変数操作と同じように扱うためのものです。

main 関数では、メッセージ (ここでは「Hello, FPGA」と改行文字) の各文字について順番に、9行目で文字を送信し、10行目でその文字の送信が終わるまで待つ、という処理を行っています。10行目のような中身のない while 文は通常の C 言語だとあまり見かけないかもしれませんが、これはビジーウェイトといい、組込みソフトウェアでハードウェアの処理を短時間待つ場合には頻出する書き方です。

Vitis での動作確認

ソフトウェアが記述できたら、次にプロジェクトをビルドします。メニューの「Project → Build All」を選択すると、自動的に必要なファイルのコンパイルやリンクなどが行われ、MicroBlaze 向けの実行ファイルが作成されます。初回は BSP のコンパイルも必要なため、少し時間がかかります。

次に、FPGA にビットストリームを、その内部の MicroBlaze に実行ファイルを書き込み、実機での動作確認を行います。

デフォルトの設定では、毎回のプログラム書き込みの前に FPGA にビットストリームを書き込むようになっていますが、これらを別々に書き込んだ方が効率的な場合も多いです。そのため、これらを別々に書き込めるように、設定を変更します。

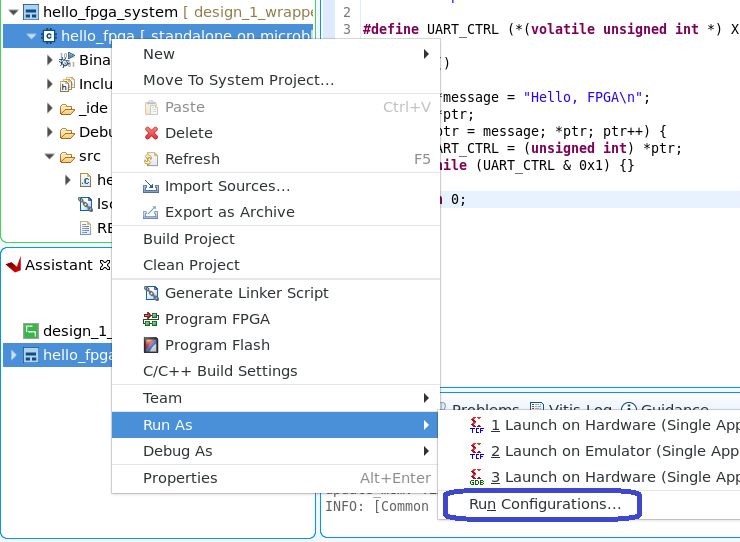

下図に示すように、アプリケーションプロジェクトを右クリックして、「Run As → Run Configurations」を選択します。

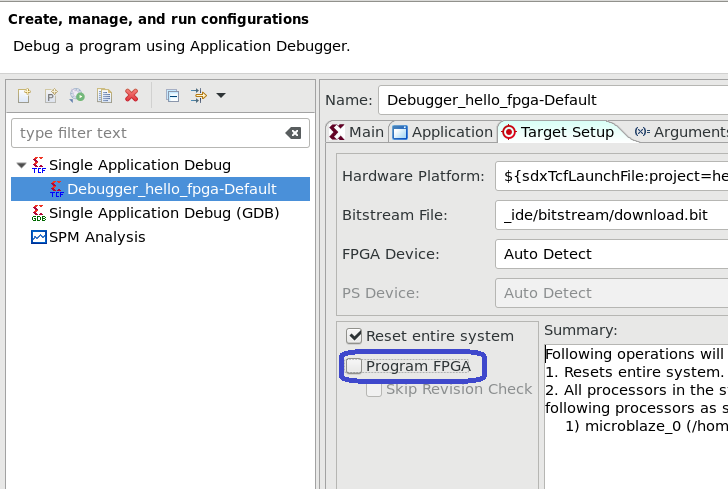

Single Application Debug の下の Debugger_hello_fpga-Default を選択します (ない場合は作成します)。続いて、Target Setup のタブを参照し、Program FPGA のチェックを外します。このときの様子を下図に示します。設定を変更したら、Apply ボタンをクリックして設定を保存し、Close ボタンでウィンドウを閉じます。

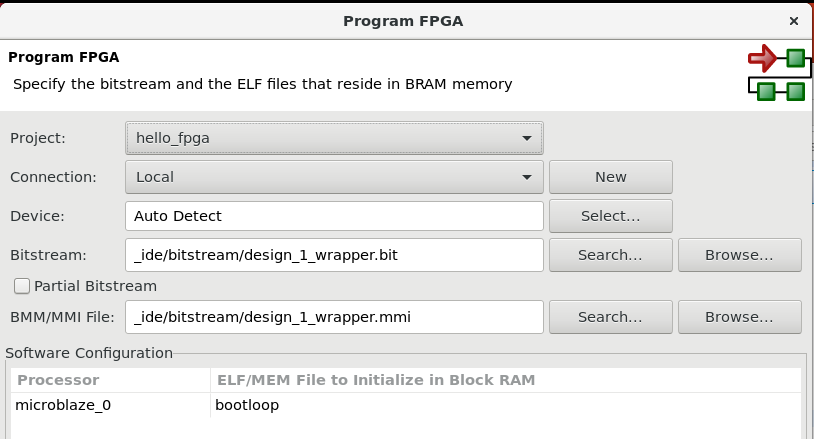

それではまずは FPGA にビットストリームを書き込みます。メニューの「Xilinx → Program FPGA」を選択するか、アプリケーションプロジェクトを右クリックして、「Program FPGA」を選択します。下図に示すダイアログが表示されますので、Program ボタンを押すと書き込みが始まります。

いよいよプログラムを書き込みます。事前に GTKterm などの実行と設定を済ませておいてください。アプリケーションプロジェクトを右クリックして、「Run As → Launch on Hardware (Single Application Debug)」を選択します。しばらくするとプログラムが書き込まれ、例によって「Hello, FPGA」が表示されます。

(注) FPGA にビットストリームを書き込んだとき、何らかの理由で TXD 出力が一瞬 ‘0’ になってしまい、うまく表示できない文字が1文字だけ送信されてしまうようです。プログラムを書き込んだときの挙動には影響しないので、今回はそのままにしています。

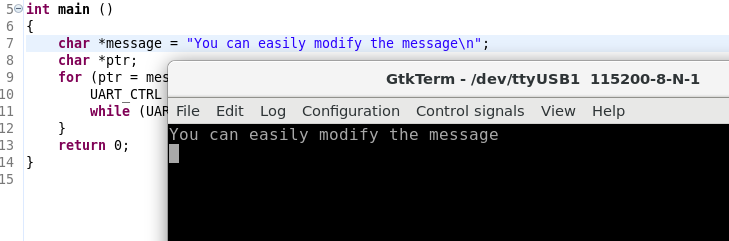

今回はプログラムでメッセージを指定しているので、プログラムを変更することで簡単に送信されるメッセージを変更できます。プログラムを変更したら、上記と同じ要領で再度ビルドを行い、プログラムを書き込んでください。なお、この時に動作中のプログラムの上書き確認が表示される場合がありますが、無視して構いません。

ACRi ルームの利用環境でプログラムを変更したときの動作結果の例を下図に示します。

ハードウェアを変更した場合

実際の開発では、後々ハードウェア側を修正・変更する場合がほとんどかと思います。ここでは、IP コアの HDL 記述を変更した場合の手順について説明します。

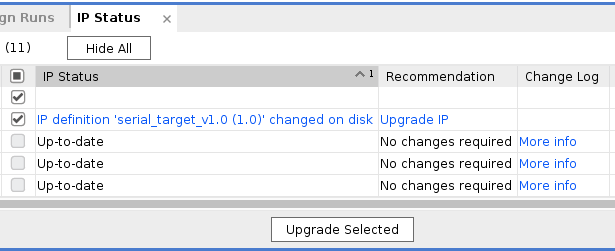

Vivado のプロジェクトのソースファイルと同様に、IP コアのソースファイルの更新時刻も Vivado によってチェックされています。ファイルに更新があったことが Vivado に認識されると、IP コアのステータスの確認を促すメッセージが表示されるので、それをもとに下図に示す IP コアのステータス画面を開きます。

ここでは、第4回 で作成した serial_target のソースコードを変更したとします。そうすると、ソースファイルが更新されたので serial_target をアップグレードするよう促されます (自動でチェックマークがつきます)。Upgrade Selected ボタンをそのままクリックして、アップグレードを完了させます。

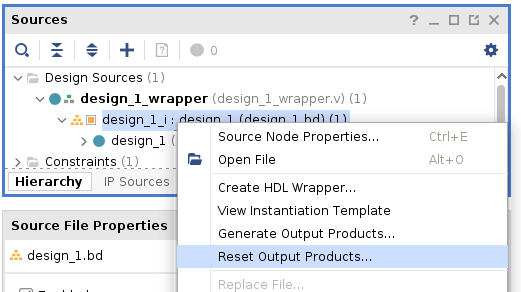

通常はここから「Generate Block Design」以降の手順を踏めばいいはずですが、時々ブロック図から生成されたファイルへ更新が反映されない場合があります。この場合には、ブロック図 (bd) を右クリックして「Reset Output Products」を選択し、生成されたファイルを一旦リセットする必要があります。このときの様子を下図に示します。

Vivado 側ではこのあと「Generate Bitstream」までの一連の手順を行い、「Export Hardware」で新しいハードウェアをエクスポートします。「include bitstream」のチェックを忘れないようにしてください。こうして、新しい xsa ファイルが作成されます。

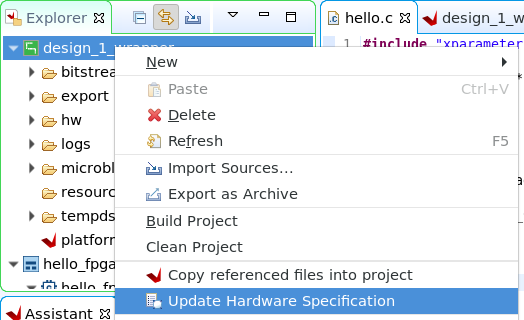

Vitis 側では、作成された新たな xsa ファイルをプラットフォームプロジェクトに適用します。プラットフォームプロジェクトを右クリックして、「Update Hardware Specification」を選択し、新たな xsa ファイルを指定します。

更新後はビルドを最初からやり直す必要があるので、メニューの「Project → Clean」を選択し、生成物のファイルを削除してから再度ビルドを行います。このとき、Platform Invalid というエラーが表示される場合がありますが、単に必要なファイルが一時的に削除されているだけなので、気にせず×ボタンでダイアログを閉じてしまって構いません。

なお、SDK では xsa ファイルの更新は自動検出されます。更新を検出するとハードウェアのアップデートを促すダイアログが表示されますので、その指示に従ってください。

Vitis や SDK でのこの辺りの作業は不安定なことも多く、ふとした弾みでプロジェクトが壊れてしまう場合がよくあります。場合によっては、必要なファイルのバックアップを取った上で、新しい作業ディレクトリ (ワークスペース) で最初からプロジェクトを作り直してしまったほうが、結果的には近道になることも多いです。

まとめ

本コースでは、2020年第1クォーター (20Q1) のコース「シリアル通信で Hello, FPGA」で作成した文字送信回路をもとに IP コアを作成し、それを他の回路やプロセッサと組み合わせて使う方法について学習しました。結果として得られる出力は変わらず「Hello, FPGA」ではありましたが、最後にはプロセッサ上のソフトウェアと組み合わせることで、かなり柔軟な使い方ができるようになりました。

最近の FPGA のよくある利用法は、大部分の汎用的な処理はプロセッサ上のソフトウェアで行い、何らかの用途に特化させたい部分だけをハードウェアとして作り込むことで、特定用途向けの処理の効率化を実現する、というものです。Zynq シリーズの場合はハードウェアのプロセッサが内蔵されているので、なおさらです。このコースで学んだことは、そうした利用法を扱うための第一歩です。

次の一歩としては、例えば実際にオリジナルの IP コアを作ってみるとか、特定の入出力を扱うためにサンプルデザインを分析・改造してみるとか、あるいは Vivado HLS (Vitis HLS) を使って C 言語から高位合成で IP コアを作ってみるとか、色々なステップが考えられます。読者の皆さんの作りたいものに合わせて、それぞれの一歩を踏み出してもらえればと思います。

……改めて、FPGA の世界へようこそ!

愛知工業大学 藤枝直輝