20Q4.04A

20Q4.04ABRAM 達人への道 (5) レイテンシ 0 FIFO と Read Modify Write

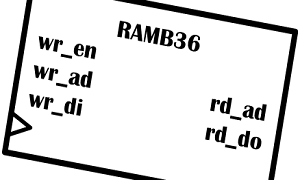

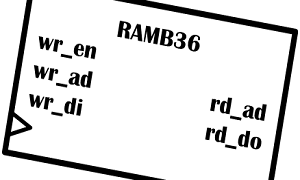

はじめに BRAM アプリケーションとして FIFO を扱ってきましたが、今回は読み出しレイテンシを0にするにはどうしたらいいか、を扱います。加えて、FIFO から離れますが、Read Modify Write を BRAM で実行したい場合について考察します。 読み出しレイテンシ0の FIFO 読み出しレイテンシ0の定義 読み出しレイテンシ0を誤解されないために、ここで扱うその定義について明確にしておきましょう。図5-1を見てください。BRAM としての出力段をラッチ...