20Q2.10B

20Q2.10BNNgenとFPGAで作るニューラルネットワーク・アクセラレータ (5)

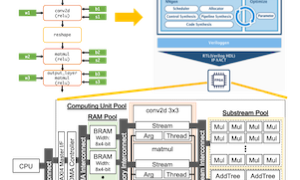

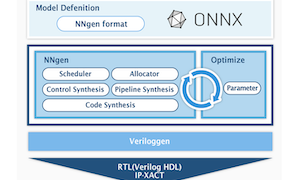

前回までは、学習済みモデルから、VGG-11 専用のハードウェアを構築したりしました。 第5回 (最終回) では、NNgen を活用するために、NNgen で利用可能な演算や入力の紹介をします。加算、減算、畳み込みといった基本的な演算から、Extern と呼ばれる CPU 上のソフトウェアと連携を可能にする特殊なものまで、いろいろあります。 データの入力 (placeholder, variable, constant) 演算の前に、データや重みを入力するインタフェースをみて...