21Q1.01B

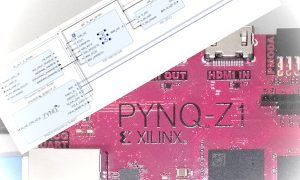

21Q1.01B自作回路を PYNQ につなぐ様々な方法 (5)

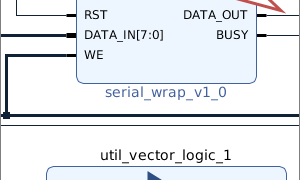

自作回路を PYNQ から使うための設計・開発法に関するコースの最終回になります。今回の設計も、対象のアプリケーションがステンシル計算であること、IP コアがフル機能の AXI をもつ場合を取り上げることは変わりません。異なるのは、IP コアを Vitis HLS (2019.2 以前の Vivado では Vivado HLS とよばれていました) による高位合成で作成する点です。 本コースで使用したハードウェア記述 (一部ソフトウェアも含む) は、GitHub リポジトリ上で公開して...