皆さん、こんにちは。これから5回にかけて、FPGA に非同期式回路を実現するための方法を解説していきたいと思います。以前、こちらのブログでも紹介があった「非同期式回路と FPGA ~ 作ってみる編」(1) から (5) と被るところもありますので、ご了承いただきたいと思います。

内容を理解する上で、「非同期式回路と FPGA ~ 作ってみる編」を先に見ておいた方が良いです。あまり冗長にしないためにも、今回は非同期式回路とはどういったものかなどの説明は割愛させていただこうと思います。以下にリンクを掲載しますので、ご活用ください。

はじめに

このブログでは、以下のスケジュールで説明をしていこうと考えています。現時点で最後まで書き切っていないため、少し修正があるかもしれません。

- 使用する非同期式回路モデルについて

- Verilog HDL によるモデリング例

- 設計 (1) – RTL シミュレーションと合成

- 設計 (2) – タイミング検証と遅延調整

- 同期式回路との比較

このブログでは、著者が長い間 Intel FPGA を対象に非同期式回路の設計支援ツールを開発してきた経緯より、Intel FPGA を対象に説明をしていきます。Xilinx 向けのものは現在開発中ですが、概ね「非同期式回路と FPGA ~作ってみる編」で述べられていることと同じようなことを想定しています。

設計支援環境

Intel FPGA の設計支援環境である Quartus Prime ですが、Standard Edition の19.1を用いています。論理シミュレータの ModelSim は、Intel FPGA Starter Edition 10.5b を用いています。今回説明する回路規模でしたら、Quartus Prime Lite Edition でも問題ないと思われます。使ってみたいという方は、以下にアクセスしてみてください。なお、初めて利用する場合、アカウントの登録が必要です (無償)。

使用する非同期式回路モデルについて

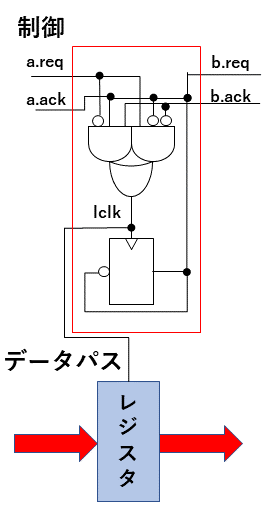

今回は、Click Element [Peters’10] と呼ばれる非同期式制御回路モデルを修正したものを使います。図1の太枠は、Click Element の論理構造を表します。

Click Element はとてもシンプルな構造をしていて、AND、OR、INV、Dフリップフロップからなっています。特徴として、非同期式回路に特有なセルを使わずに実現していることが挙げられます。ちなみに、[Peters’10] の論文では、Click Element を用いた非同期式回路を、同期式回路の Electronic Deign Automation (EDA) ツールで設計することも説明しています。また、Intel が研究用で開発している Loihi と呼ばれるニューロモーフィック回路の制御回路も、Click Element をベースにしているようです。興味がある方は是非 [Peters’10] の論文をご覧ください。

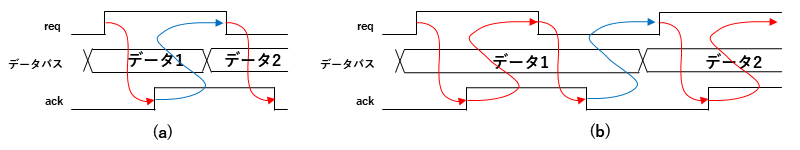

Click Element は、要求、応答信号 (ハンドシェーク信号とも呼ばれる。図1では,a.req とa.ack,b.req と b.ack に該当) による制御回路間の通信は、二相式と呼ばれるプロトコルを用いています。一方、レジスタへの書き込みを行うローカルクロック信号 lclk は、四相式と呼ばれるプロトコルを用いています。二相式と四相式は、図2に示す通り、一連の制御を行うために要求、応答信号の2つの相 (両方の 0→1 遷移、あるいは 1→0 遷移) で行うか、4つの相で行うかという違いがあります。二相式にするとハンドシェーク信号による通信時間は四相式と比べ短くなるという特徴があります。

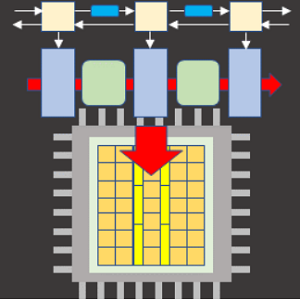

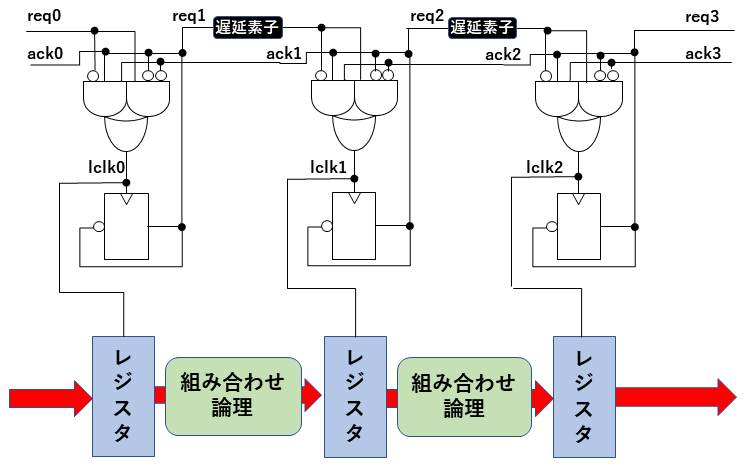

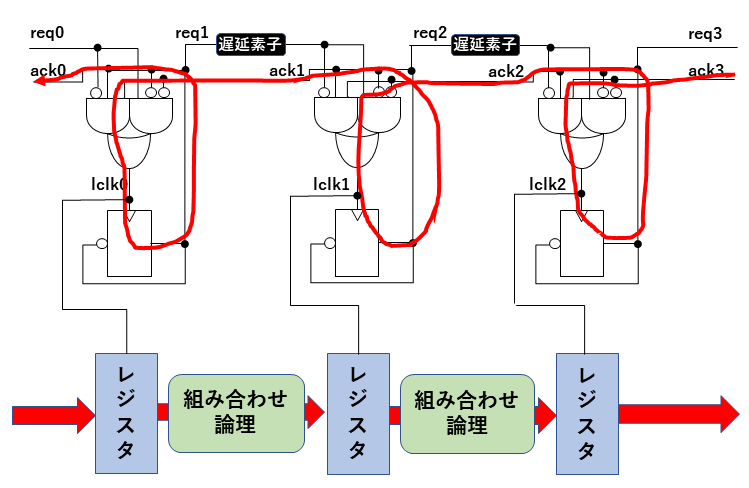

Click Element では、データエンコーディングは束データ方式と呼ばれる方式を採用しています。束データ方式の場合、データパス回路は同期式回路と同じで、制御回路はレジスタ間の最悪遅延より長い遅延を持った遅延素子を要求信号線上において、タイミングを保証します。図3は、3つの Click Element からなる回路モデルを表します。

Click Element の修正

Click Element の修正に関してですが、まずは動機から説明したいと思います。二つあり、そのうちの一つは性能です。非同期式回路では、データを転送する際、受け取り側がデータ受け取りを表す応答信号を生成することで、送り手側は次のデータを送信します。パイプライン回路の場合、応答信号の生成は、前のステージからの要求信号 (データを送りますよという意味) の他、後のステージの応答信号の値 (空いていますという意味) を確認した上で生成することになります。例えば図3の場合、ack1 が1になる条件は、req1 が1でなおかつ ack2 が0の時です。つまり、応答信号の生成は、後のステージにも依存するということです。図3の例でいえば、図4の通り、最後の応答信号 ack3 が最初の応答信号 ack0 まで影響を及ぼすということになります (赤矢印)。

パイプラインステージが深くなれば深くなるほど、この影響は大きくなり、性能にも影響を及ぼします。

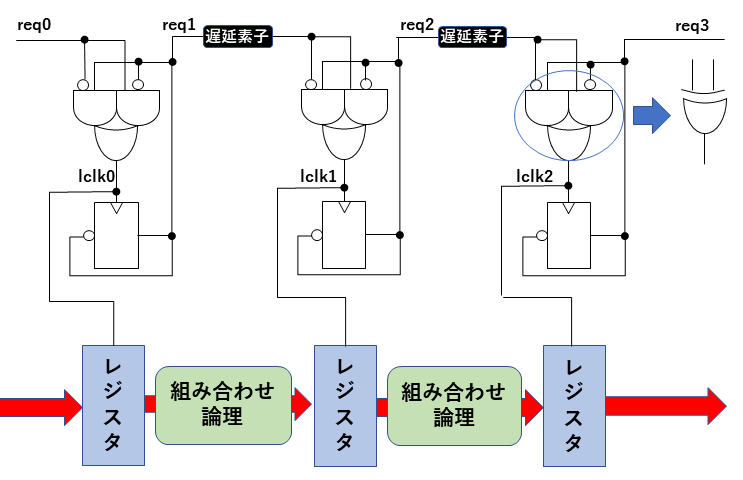

もう一つは、レジスタの書き込みタイミングのずれです。後のステージの ack 信号の影響は、レジスタの書き込みタイミングにも影響を及ぼします。例えば、ack2 の値が変化するためには、lclk2 が1である必要があります。その後、ack2 が変化し、lclk1 が変化します。これは、lclk2 と lclk1 にはズレがあるということを意味します。このズレがレジスタのセットアップ・ホールド違反をもたらす恐れがあります。こうしたことより、今回は図5のように Click Element のうち、ack 信号を無くしたものを用います。ack を無くすと、AND-OR の部分は、eXculsive OR (XOR) に置き換えることができます。ack を無くした場合、動作が完全に遅延素子に依存してしまうので、この回路は従来のハンドシェーク信号による非同期式回路とは異なる自己タイミング型 (self-timed) の非同期式回路です。また、Click Element とは呼べませんので、今後は Self-timed モジュールと呼んでいきます。

次回は

次回は、設計の対象となるアプリケーション例と Verilog ハードウェア記述言語 (Hardware Description Language, HDL) による Self-timed モジュールのモデリングを紹介したいと思います。

会津大学 齋藤 寛

[Peters’10] Ad Petters et al., “Click Elements An Implementation Style for Data-Driven Compilation”, Proc. ASYNC, pp.3–14, 2010.