はじめまして。 AVNET 仲見です。ここでは XILINX 社が Release している統合開発環境の Vitis という Tool の概要、構築するための Flow についてご紹介いたします。

XILINX 社の Tool はどんなものがあるの?

まずはじめに、XILINX 社が現在 Release している Tool について Hardware、Software のそれぞれの開発では以下が用意されています。

Hardware 開発

Vivado Design Suite-HLx Edition

Vivado でRTL (Verilog/VHDL) およびIP Integrator、FPGA の回路の開発

Software 開発

Vitis コア開発キット

Embedded Application、Acceleration Application の開発

Vitis Acceleration Platform の構築

Vitis HLS (CtoRTL) を使って Acceleration の開発

Petalinux ツール

Xilinx SoC 上で動作する Embedded Linux の構築

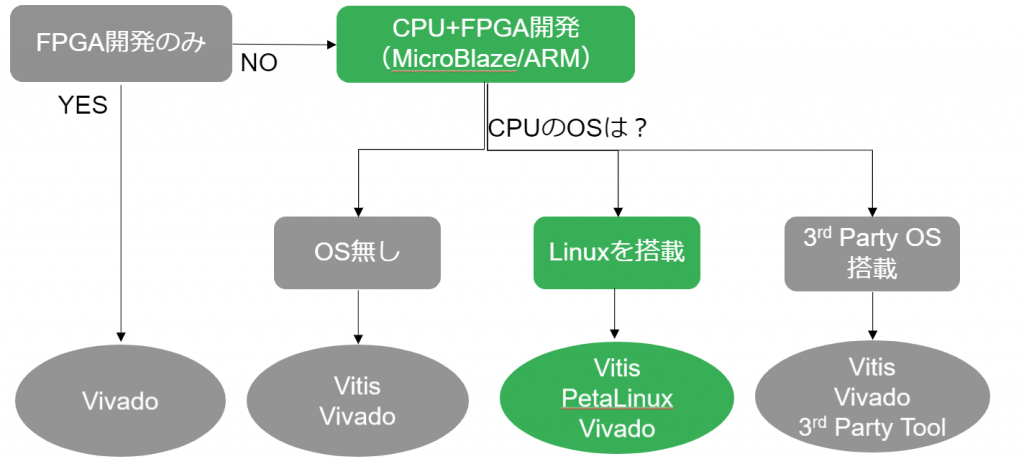

XILINX 社 ではこの3つの Tool を使用して FPGA および Zynq の開発を行います。目的別に Tool を分類すると以下の様な Flow になります。

Vitis で FPGA Acceleration を行うには、Zynq Series で、かつ ARM Linux を搭載する必要があります (図の緑色の Flow が必要)。

FPGA による Acceleration の Tool Flow は?

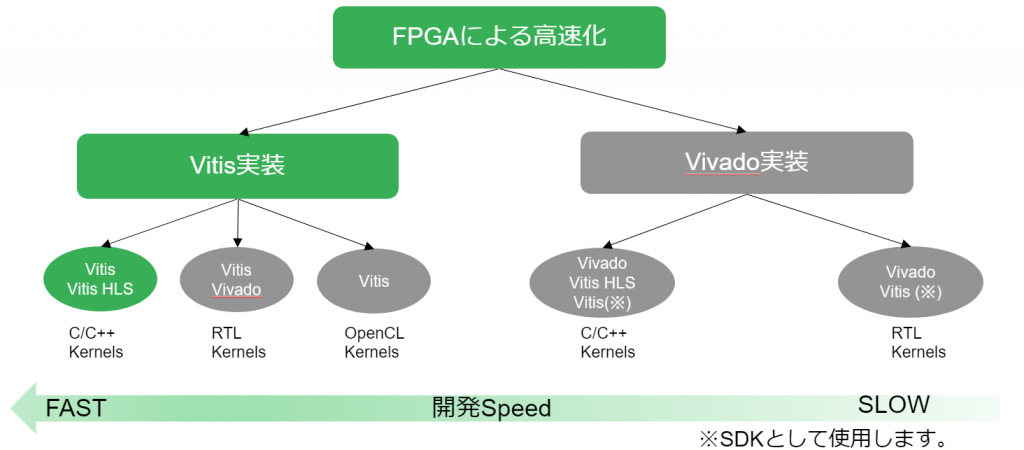

XILINX 社の Tool を利用して、FPGA Acceleration で使用する Tool Flow は以下のようになります。

従来では、Vivado で Acceleration Algorithm を設計し、Algorithm を含む Hardware Design の組み込み、そして Algorithm に対しての Peripheral Driver を SDK (Vitis) で設計し、最後に Software Application の開発という手順を踏む必要がありました。

しかし、Host Code を OpenCL で統一し、Kernel 部分のみを変更することができるようになるため、FPGA での Acceleration の開発 Speed は飛躍的に進歩しました (図の緑色の Flow)。また、従来のやり方では Hardware 構成が変わるため、Hardware と Software の両方の開発者が必要でしたが、Algorithm 部分のみの変更であれば、Software の開発者だけでも Acceleration Application を構築できるようになりました。

Vitisとは?

では、本題の「Vitis とは?」ですが、FPGA、Zynq Series 、Versal ACAP、Alveo Series で Edge および Cloud (on-premises) の Acceleration Application 開発が可能な統合開発環境です。Acceleration Application とは?という部分については、別 Blog にも詳細な記事があるため、ここでは割愛させていただきます。

この統合開発環境は、無償での提供となっており Hardware 開発用の Vivado (※) が同梱されており、追加で Install すること無く Hardware の開発も可能です。

※ License は WebPack となっており、Logic 規模が大きいものでは有償の Vivado のLicense が必要です。

それでは、この統合開発環境ではどのように Acceleration Application を構築していくかご説明いたします。

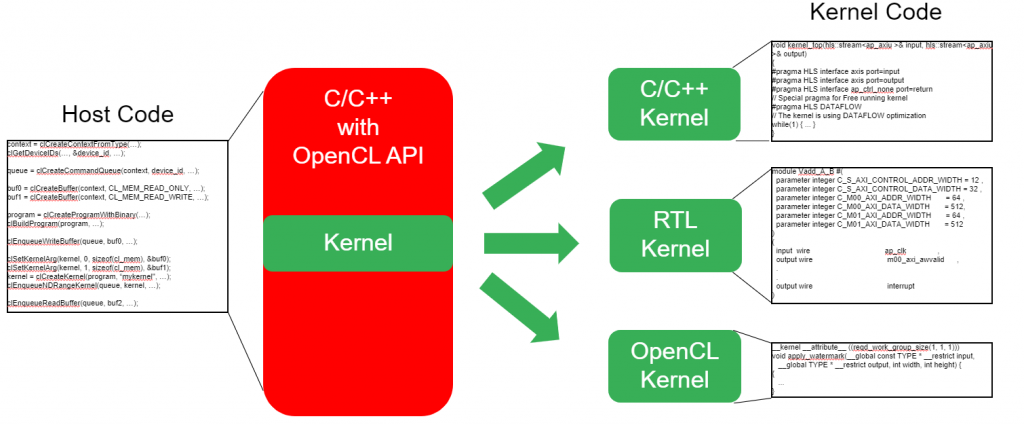

- Application の Host Code の記述言語は C/C++ で OpenCL API を使って記述

- 専用の Vits Target Platform が必要

- User が作成する HW Acceleration 関数は Kernel と呼び GUI 上で登録

- Compile 環境は Linux (Ubuntu など) のみで Windows には非対応

- Kernel の記述方法は3種類

- C/C++ Kernel (Vitis または Vitis HLS で構築)

- RTL Kernel (Vivado で構築)

- OpenCL Kernel (Vitis で構築)

実際の Coding Image は以下のようになります。

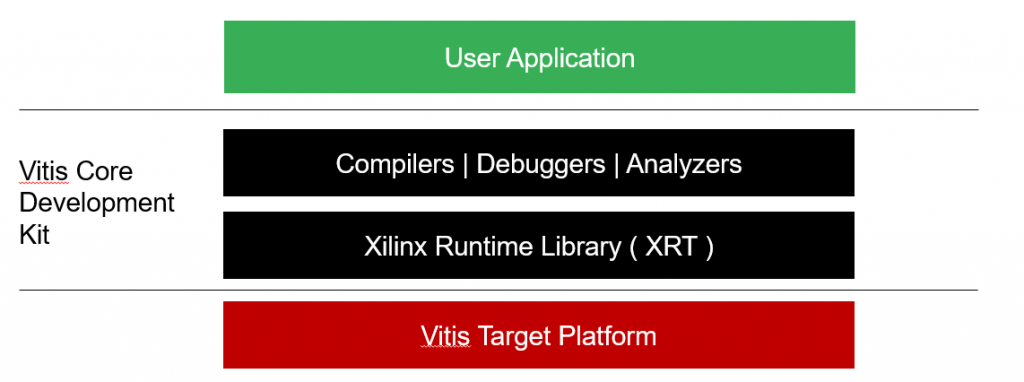

Vitis コア開発キットに含まれるものは?

Vitis には Software 開発に必要な Compiler 、Debugger 、Analyzer が含まれています。

XRTとは?

Acceleration Application を実装するためには Xilinx Runtime Library (XRT) が必要不可欠です。この XRT には、OpenCL の API や、CPU-FPGA 間の Driver が含まれており、Application から FPGA Configuration をする機能などはこの XRT の機能を利用することにより User は Interface を意識すること無く Application の構築が可能となります。

ちなみに、XRT は Vitis には同梱されていないため、XILINX 社の Web Page より Download し Install する必要がありますので、ご注意ください。

Vitis Target Platform とは?

Acceleration Application を実装するためには Vitis Target Platform が必要不可欠です。XILINX 社製の評価 Board (ZCU102、 ZCU104 etc.) 、Alveo Serise については XILINX 社のWeb Pageで公開されています。こちらも XRT と同様ですが、Default では Tool に Install されていないのでご注意ください。

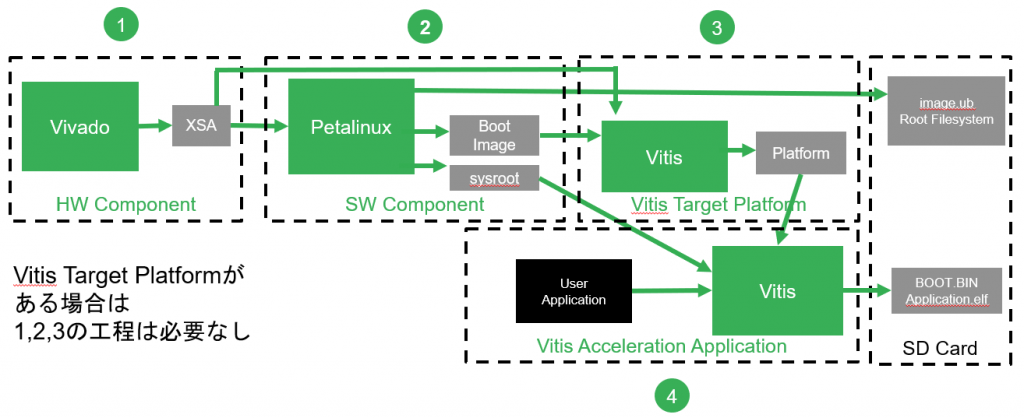

XILINX 社製ではないものについては、Board を作成している Vendor が提供しているもとを使うか、User 自ら作成する必要があります。VivadoでVitis Target Platform を用意し、Vitis で Application を構築までの Flow としては、以下の図のように大きく分けて4つの Step を踏む必要があります。

- HW Component では、Vivado を使用して CPU の設定、FPGA の機能 Block の構築を行います。

- SW Component では、PetaLinux を使用して Linux Kernel の構築を行います。

- Vitis Target Platform では、HW および SW Component で生成した Data をもとにAcceleration Application 構築に必要な Platform の構築を行います。

- Vitis Acceleration Application では、Vitis Target Platform上で動作する Application を構築します。

上記の4つの Step の殆どは下地となる Platform 作成となり、Hardware および Software の知識を必要とします。FPGA Acceleration が初めての方は、Vitis Target Platform を0から作成しないで始める (1から3までの Step を省略できる) という点で、まずは XILINX 社製評価 Board を利用することをお勧めします。また、Vitis Target Platform の構築方法については今後の Blog にて紹介しようと思います。

Vitis で実現できる Acceleration Application は?

FPGA で Acceleration できる Application の例としては、画像処理 (主に Filter 系)、算術演算、機械学習などがあります。

XILINX 社ではこれらを Vitis Library および Vitis AI という形で Open Source で公開しています。詳しくは、こちらも、今後の Blog でご紹介しようと思います。

AVNET K.K. 仲見 倫