前回は FPGA を活用することで低遅延、高スループット、低消費電力を実現できるしくみについて解説しました。そしてそのメリットをより多くの方に享受いただくための開発環境として Vitis が誕生したことをお話ししました。

今回はその開発環境について解説します。さらに、8月からオープンとなった ACRi ルーム (FPGA 利用環境) を使って実際にツールとハードウェアを動かしてみましょう。

統合ソフトウェアプラットフォーム “Vitis” とは

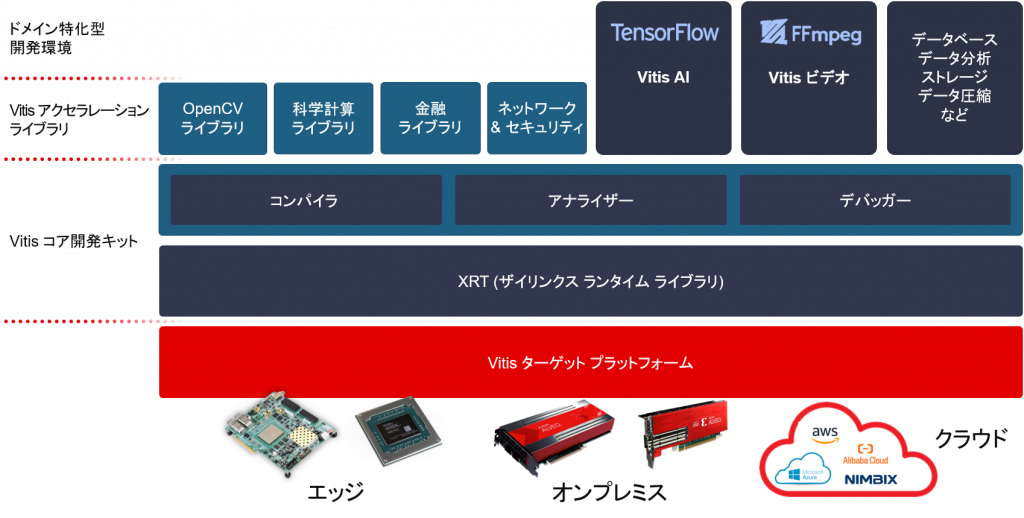

ザイリンクス社 Vitis (“バイティス” と読みます) はソフトウェア、ハードウェアすべての設計ツールを統合化した開発プラットフォームです。

ARM プロセッサを内蔵した zynq のプロセッサソフトウェア開発ツールのみならずプログラマブルロジック部もソフトウェア開発フローで設計ができることを意識した環境であるため、「統合ソフトウェアプラットフォーム」と呼んでいます。

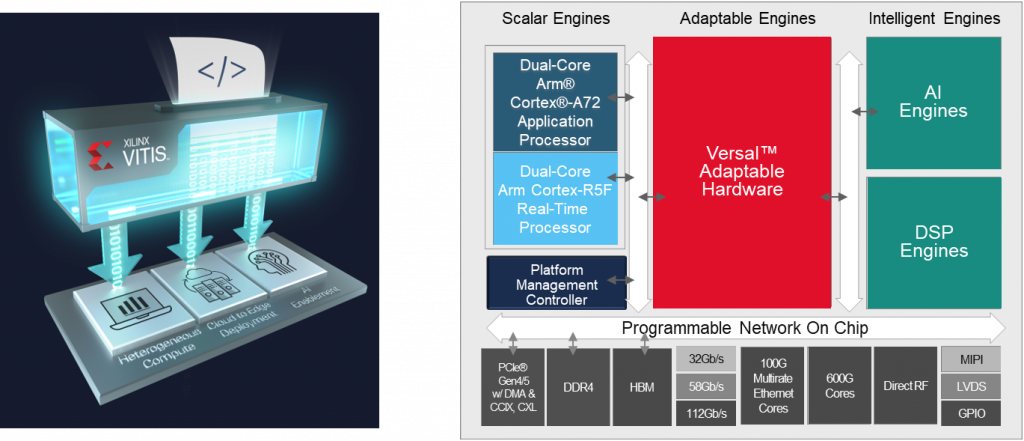

一般にタスクにはソフトウェアで実装したほうが適している処理、信号処理用プロセッサが得意な処理、ハードウェアで実現すると圧倒的に効果的な処理などが一連のフローに混在している場合が少なくありません。下図はザイリンクス社の Versal (“バーサル”と読みます) という製品の例ですが、異なる特性を持つプロセッサやプログラマブルハードウェアをしかも一つのデバイス内に混在させて一連のタスクとタスク間のやり取りを効率よく実行できることは FPGA だからこそできる優位な点です。

Vitis は、このようなヘテロジニアス・コンピューティングの時代にマッチした開発環境を提供します。さらにこの開発環境は前回のブログで触れたいくつかの課題を解決してくれます。

C++ などソフトウェア記述言語で設計が可能

FPGA はハードウェア記述言語 (HDL) で設計することが一般的で、ハードウェア設計固有の技能が必要であるため、ソフトウェアエンジニアにとってはとっつきにくいものでした。しかし数年前からC言語をベースとする HLS (High Level Synthesis ; 高位記述言語) という設計言語で関数を記述してコンパイルすることによって機能ブロックのハードウェアモジュールを生成し、他のハードウェアモジュールとリンクしてシステムに組み込まれるようになりました。

このアプローチによってハードウェア設計固有の技能の必要性を大きく軽減し、ソフトウェアエンジニアが容易に使用できるようになりました。さらにソースファイルの可読性と変更容易性を大幅にアップし、試行結果を素早く反映できるようになったことで、生産性を大きく向上しています。

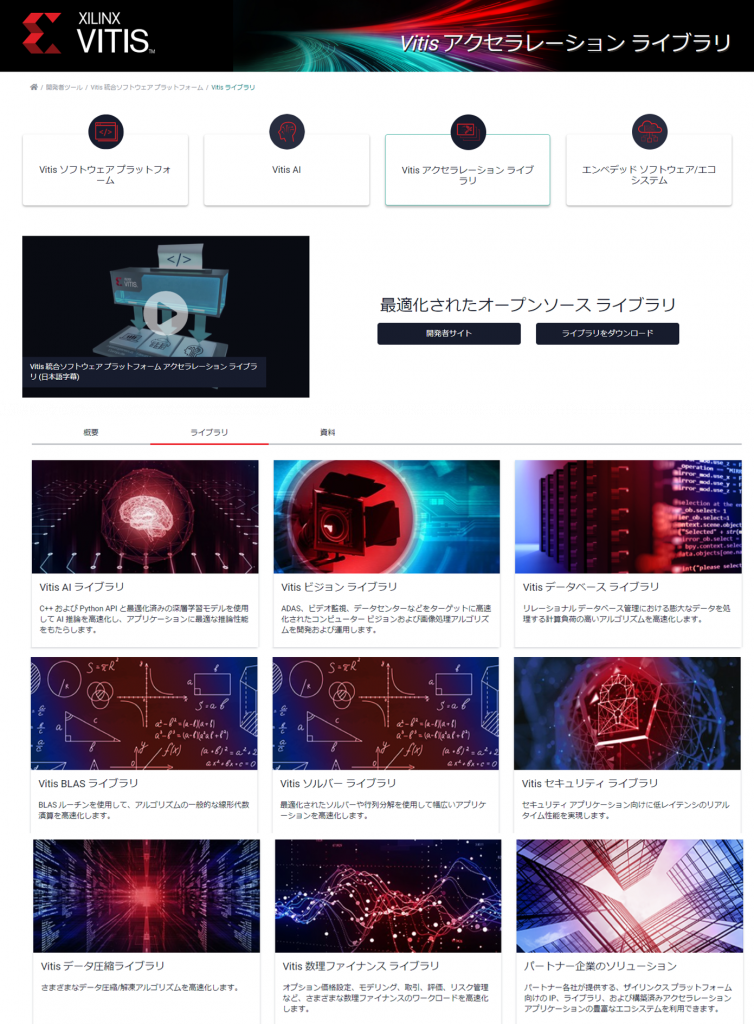

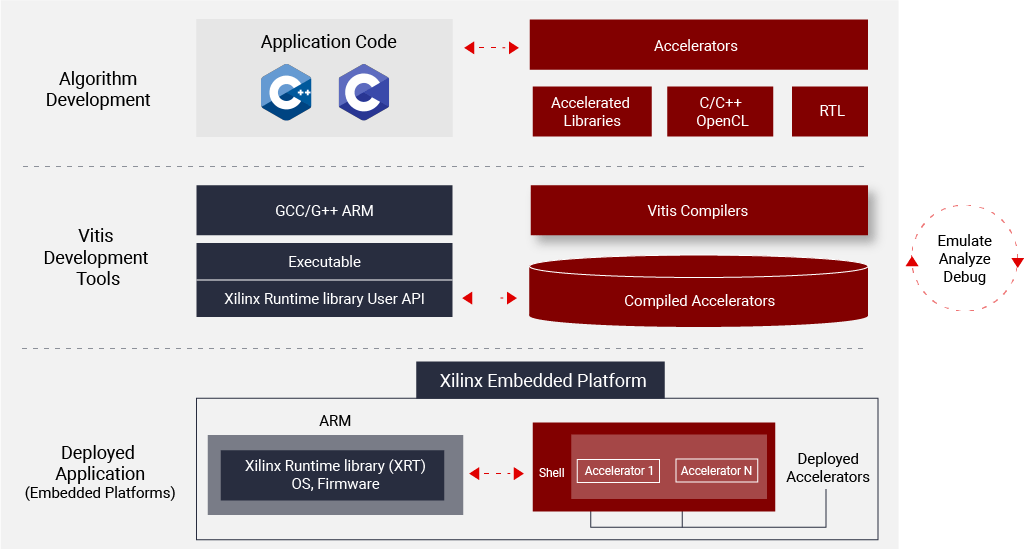

アプリケーションごとに最適化されたライブラリ

開発効率をさらに高めるために最適化された検証済みのライブラリをザイリンクス社およびパートナーから提供しています。

下図のように金融、ビデオ、ディープラーニング、データベース、ネットワークなどの分野には FPGA によるソリューションが効果的なアプリケーションが多数存在し、そのようなアプリケーション向けに最適化されたライブラリが準備されています。

ユーザが開発時に組み込んで使う HLS 関数やすぐに動かすことができるビルド済みでそのまますぐに動かすことのできるアプリケーションレベルのカーネルなどいくつかの形態で提供されています。ザイリンクス社からはオープンソースで費用負担なく利用いただけるようなライブラリを豊富に提供しており、さらに急速に拡充を続けています。次回説明する Vitis-AI はこれらライブラリ群のひとつとして提供しています。

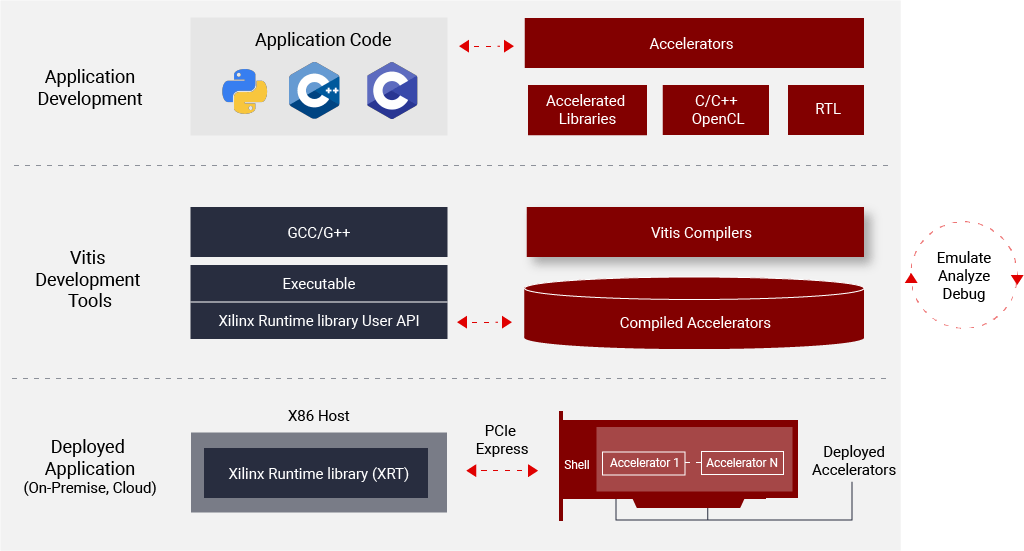

プロセッサとプログラマブルロジック間のインターフェースを自動生成

アクセラレータボードとホスト間のやり取りを PCIe を経由しておこなう場合、カード側の PCIe のハードウェア設計やホストとカード間の通信ドライバは設計者が作らなければなりませんでした。また ARM プロセッサを内蔵した SoC タイプの FPGA ではプロセッサ部とプログラマブルロジック間のインターフェースはハードウェア、ソフトウェアとも設計者が作らなければなりませんでした。

これらの標準インターフェースを設計することは機能を差別化する部分ではありませんが、設計者には大きな負担となっていました。Vitis はこれらのインターフェースのためのソフトウェア、ハードウェアを自動生成します。これにより、設計者は差別化する機能のデザインに集中することができます。

すぐに商用利用が可能なプラットフォームハードウェアを提供

ソフトウェア開発が容易になってもデバイスを搭載した基板設計をしなければならないとなると特にサーバーのアクセラレーションや CPU のオフロードを実現したい場合には工数、設計期間、開発費用などが負担となってしまいます。

このような障壁を解消するためにザイリンクス社からは Alveo という商用で利用可能なアクセラレータカードを提供しています。またパートナーからもアクセラレーターカードや zynq を搭載した SOM が提供されています。

クラウド、オンプレミス、エッジすべてを統合

近年、クラウドの活用が増大しています。しかし、用途によってはオンプレミスでシステムを構築したい場合も少なくありません。また、オンプレミス用途の検証をクラウドで手軽に行いたいといったニーズも増えています。さらに、例えば機械学習の推論をエッジで行う場合とクラウドで行いたい場合があります。

これらすべての開発環境を統合化することでクラウドとオンプレミスの間の移行を容易におこなうことができます。またクラウド向けに開発を経験した技術者がエッジ向けのシステム開発を行うラーニングカーブを大幅に短縮します。

試してみよう!

それでは Vitis を使った開発フローを体験してみましょう!

ACRi ルームの利用

今回は、8月からオープンとなった ACRi ルームを使用して Alveo アクセラレータカードを使った開発フローを体験します。zynq を使用したエンベデッド向け開発環境の ACRi ルームへの設置について現在検討中ですが、共通部分が多いと思います。

ACRi ルームを利用するためにはアカウントの申請と承認が必要になります。利用にあたって料金はかかりません。アカウント申請後、承認されるとユーザーネームとパスワードを含む承認のメールが届きます。ACRi ルームについて詳細は利用説明の「よくある質問」を参照して下さい。

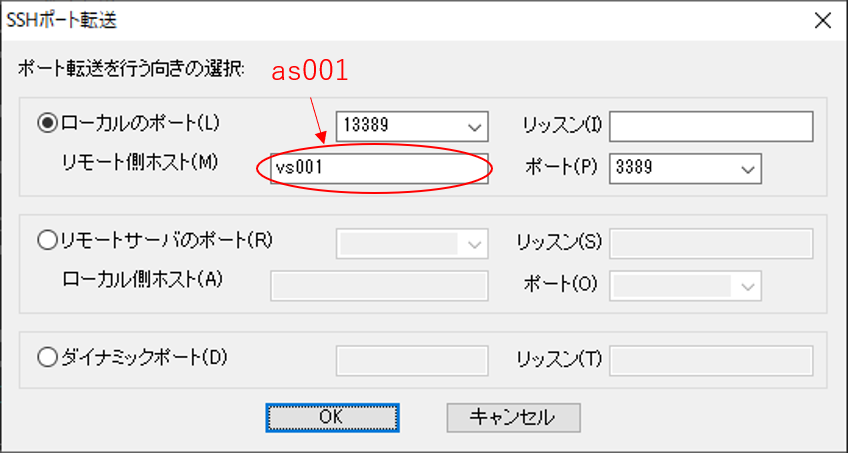

ACRi Room の FPGA 利用環境の予約・使用方法を参考にしながらサーバーの利用予約をしましょう。利用可能なボードが何種類かありますが、今回は Alveo U200 が搭載されているサーバー as001 を使用します。予約受付を完了すると、予約受付完了のメールが直ちに届きます。

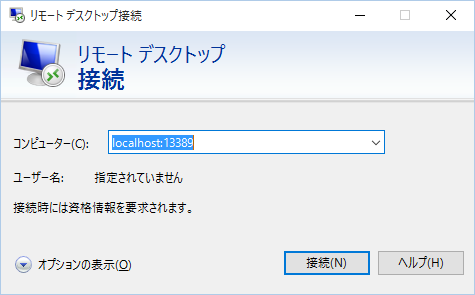

予約時間になったら、お勧めの方法として紹介されている「Windows 10 の「リモート デスクトップ接続」で FPGA 利用環境 (ACRi ルーム)を使う」を参照しながらリモート接続しましょう。注意点として、説明のSSHポート転送の図例で vs001 となっているリモート側ホストアドレスをサーバーに合わせて変更する必要があります。今回は使用するサーバ 「as001」を入力します。予約完了通知メールには [サーバ] として案内されています。

リモートデスクトップ接続画面で「コンピューター (C) 」に説明に沿って入力して「接続 (N) 」をクリックします。リモートデスクトップ接続ログイン画面で username の入力欄が表示されない場合は自分のアカウント password のみを入力します。

リモートデスクトップ接続ができたら、いよいよ Vitis を使用するための環境設定から始めます。「サーバで Vivado と Vitis (または SDK) を使用する」に説明されているとおり、画面左上にある Activities から Terminal を起動してコマンドウィンドウを開きます。

Vitis チュートリアル

ここからは「Alveoサーバーの利用方法 – Vitis チュートリアル」をもとに進めましょう。

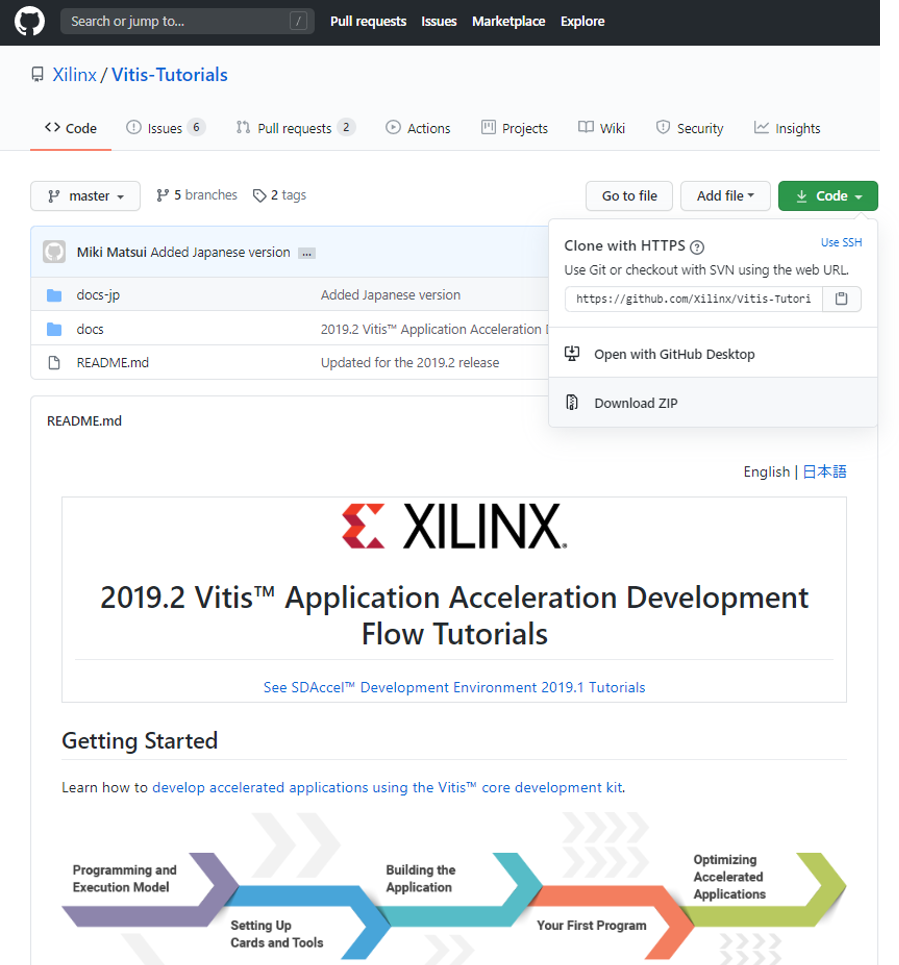

初めに Vitis チュートリアルのダウンロードと転送を行います。 ブラウザからダウンロードする場合は下記のサイトの緑色の “Code” アイコンから “Download ZIP” を選択してダウンロードします。

チュートリアルの zip ファイルをパソコンから Alveo サーバに送信するのに WinSCP を使う場合はこちらのページにある「WinSCP を使う場合」の説明が参考になります。

scratch 領域に移動して Vitis チュートリアルのファイルを unzip した後、今回試す /scratch/Vitis-Tutorials-master/docs-jp/docs/my-first-program/reference-files フォルダに移動します。

次に Vitis と XRT をセットアップします。 XRT とは Xilinx Runtime Library のことでホストプログラムがターゲットプラットフォームにアクセスするための API およびドライバーを提供し、ホストプログラムとアクセラレーションカーネルの間のトランザクションを担います。詳しく知りたい方はオンラインマニュアルを参照してください。

Vitis コア開発キットを使用したアクセラレーションアプリケーションの開発 入門編は以下の 5 つのステップで構成されています。

1. プログラミングおよび実行モデル

2. Alveo データセンター アクセラレータ カードおよび Vitis コア開発キットの設定

3. アクセラレーションされたアプリケーションのビルド – 基本的な概念

4. はじめてのプログラム

5. Vitis 環境手法に基づいたアクセラレーションされた FPGA アプリケーションの最適化

今回取り上げる Vitis チュートリアル My First Program はこれらのうち4番目「4. はじめてのプログラム」となります。1~3 に目を通すと基本的なポイントについて理解を深めることができるでしょう。

「4. はじめてのプログラム」には日本語の詳しい解説「はじめてのプログラム」があります。演習は以下の4つのステップを含んでいます。

- はじめての C++ カーネルの記述: アクセラレータで実行するハードウェア カーネルを作成します。

- はじめてのホスト プログラムの記述:カーネルを実行するのに必要な API 呼び出しの作成を含め、単純なホスト プログラム コードを作成します。

- アプリケーションのコンパイルおよびリンク: ホスト プログラムおよびハードウェア カーネルをビルドします。

- アプリケーションのプロファイル: アプリケーション デザインをプロファイルおよび最適化します。

今回は Vitis チュートリアルに沿って make ファイルの実行までを行うことで、上記 1~3 を体験しましょう。各解説を参照すれば演習を進められますが、いくつかポイントを補足します。

初めての C++ カーネルの記述

関数引数のマップについて

ソフトウェアの場合、引数や結果の関数との受け渡しはレジスタやスタックを介して行われているのが一般的です。この割り当てはコンパイラが行ってくれるため、通常は意識する必要がありません。

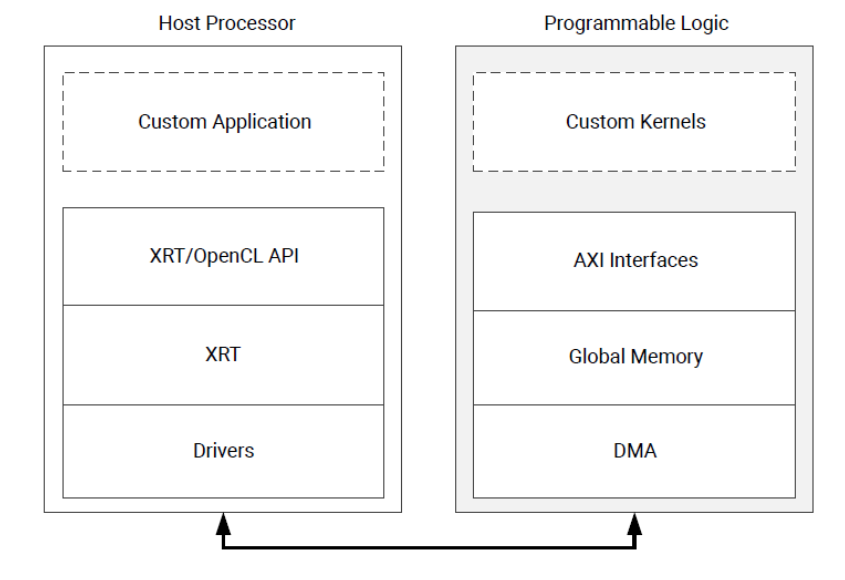

アクセラレータの場合、アプリケーションプログラムはホストプログラムとアクセラレーションカーネルに分割され、両者はホストプログラムから XRT を通して PCIe バスを経由する通信チャネルで接続されます。

ホストとカーネルの間の制御およびデータの転送にはカーネル側にあるグローバルメモリが使用されます。グローバルメモリにはホストプロセッサとアクセラレータの双方がアクセス可能です。一方、ホスト側のメモリにはカーネルからはアクセスすることができません。

典型的なアプリケーションでは以下の手順が行われます。

1. ホストプログラムが PCIe を介してグローバルメモリにデータを書き込みます。

2. ホストプログラムがカーネルを設定します。

3. ホストプログラムが FPGA のカーネル関数の実行を起動します。

4. カーネルがグローバルメモリからのデータを読み出しながら計算を実行します。

5. カーネルがグローバルメモリに計算結果を書き込み、タスクが終了したことをホストに通知します。

6. ホストプログラムがグローバルメモリからホストメモリにデータを読み出します。

ホストとカーネル間のデータ転送には2つのタイプがあります。ひとつはデータ ポインターでグローバルメモリを介してホスト CPU とアクセラレータ間で転送されます。もうひとつはスカラーデータでホストからカーネルに直接受け渡されます。

• C/C++ 関数のポインター引数には AXI4 マスターインターフェイス (m_axi) が割り当てられます。

• スカラー引数、配列の制御信号、グローバル変数、およびソフトウェア関数の戻り値には、AXI4-Lite インターフェイス (s_axilite) が割り当てられます。

この割り当てを明示的に定義するために Vitis バージョン 2019.2 まではチュートリアルのソースコードに定義されているように #pragma HLS INTERFACE の宣言が必要でした。最新の Vitis バージョン 2020.1 からはツールが受け渡しのインターフェースを自動的に割り当てることができるようになりましたので、これらの #pragma HLS INTERFACE の宣言は不要となっています。Vitis 2019.2 と 2020.1のそのほかの HLS 関連の違いは UG1391 (Vitis HLS Migration Guide) を参照してください。

はじめてのホストプログラムの記述

FPGA のアクセラレータ開発環境は OpenCL (オープンシーエル : Open Computing Language) というヘテロジニアス・コンピューティングを利用した並列コンピューティングのためのクロスプラットフォーム API がサポートされています。

OpenCL について詳細は Khronosのサイト や書籍等を参照下さい。

アプリケーションのコンパイル、リンク、実行

今回は makefile を使用して gcc によるホストプログラムのビルド、v++ による FPGA カーネルハードウェア実行ファイルのビルドおよびビルドしたアプリケーションを実行します。

$ make all TARGET=hw DEVICE=xilinx_u200_xdma_201830_2実行開始からほぼ1時間で正常終了し、TEST PASSED のメッセージがターミナルに表示されます。途中の実行過程のメッセージ出力が 5分~10分程度止まって見えることがありますが実行していますので安心して下さい。

TARGET に hw を指定したことでカーネルのコードは実際に Alveo カード上の FPGA にロードされ実行されています。ハードウェアカーネルのコードをビルドするためには、FPGA 内にたくさん埋め込まれている素子をどのように利用してどの素子とどのように接続して機能を実現すると効率的で高い周波数を安定的に達成できるか、といった計算をおこないます。

自由度が高いことで高い性能を実現できるのですが、自由度が高いがゆえに選択と組合せが膨大なため、ソフトウェアのコンパイルと比較して長い時間がかかります。開発初期のデバッグ段階において TARGET に sw_emu や hw_emu を指定して CPU でハードウェアの論理をエミュレーションすることでコンパイル時間を大幅に短縮し、論理チェックを短時間で実施できます。エミュレーションのモードについてはこちらのページが参考になります。

アプリケーションのプロファイリング

実際の開発では、全体のコードのどの部分をカーネルで実行すると効果的か、設計したカーネルの実行時間が目標を満たしているか、といった検討や検証を行う必要があります。また、カーネルが処理時間を短縮できたとしても、ホストとカーネル間のデータ転送時間が長いと全体として思ったほどの効果を得られなくなります。

Vitis に組み込まれている vitis analyzer はプロファイリング、タイムライントレース、レポートといった機能を提供しています。これらの機能を使用して分析を行い、様々なテクニックを使って全体の最適化を進めることができます。

Vitis IDE

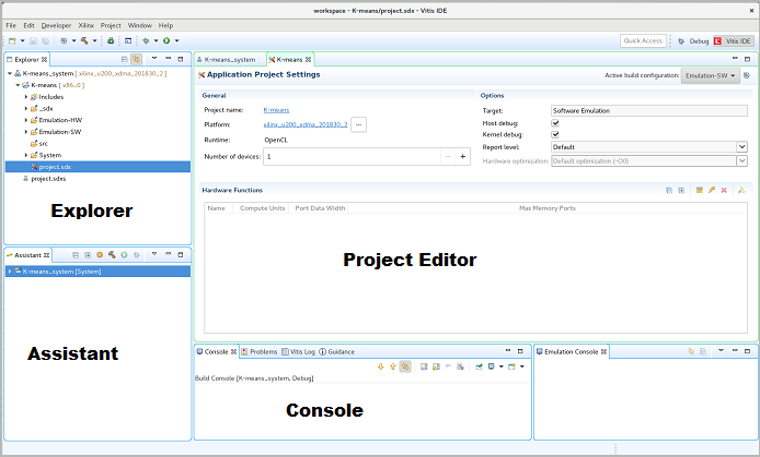

今回はコマンドラインと makefile でフローを体験しました。vitis は GUI で使用することも可能です。

ACRi ルームの環境においても環境設定をおこなったあと、ターミナルに vitis と入力することで Vitis IDE を起動することができます。プロジェクトの作成など Vitis IDE の使用方法についてはオンラインマニュアルを参照してください。

まとめ

今回は Vitis 開発環境が従来の課題をどのように解決するかについて解説しました。さらに ACRi ルームを使って実際にツールとハードウェアを動かしてみました。

次回は高いスループット、超低遅延と低消費電力を同時に実現する Vitis AI について解説します。さらに画像認識をおこなうまでのフローを ACRi ルームを使用して体験してみたいと思います。

ザイリンクス株式会社

堀江義弘