本コースでは、複数の FPGA を用いた計算機システムの構成と、私達が研究開発が行っているカスタム・コンピューティング・システムについて紹介していきます。

第5回では、FPGA をカスタム・コンピューティング・システムとして利用するために開発を行っている、我々の独自シェル “AFUShell” について解説していきます。

先日、クラスタの名称が、

“ESSPER: Elastic and Scalable System for high-PErformance Reconfigurable computing”

と決まりました!

シェル (Shell) とは

シェル (shell, 貝殻) は、FPGA を搭載したシステムの運用には欠かせない機能です。ここでは、用語の定義を行い、Intel 社のシェルを例に役割を見ていきます。

「シェル」の用語の定義

明確な定義はありませんが、一般的にシェルは以下の様なものを指しています。

FPGA を固定機能部とユーザロジック部に分離した際の、固定機能部の名称。シェルには、ユーザロジック部に実装される回路で共通して利用されるハードウェア・モジュールがまとめて実装され、それらのインターフェースがユーザロジック部に提供される。

提供される機能は、DDR メモリや PCIe, SL III などの I/O コントローラや, LED, JTAG など。また、ユーザロジック部はユーザが利用する領域で、動的部分再構成 (パーシャルリコンフィギュレーション) 機能を用いて FPGA の電源を切らずに回路の切り替えが可能。

回路の書き換えに電源のオンオフが必要なくなることで、FPGA ボードを搭載するサーバ本体の電源をオンのまま役割を変更できる様になり、実運用が可能となります。

なお、シェルという名称は、2014年の Microsoft 社の Catapult v1 の論文が始まりだと思われます。

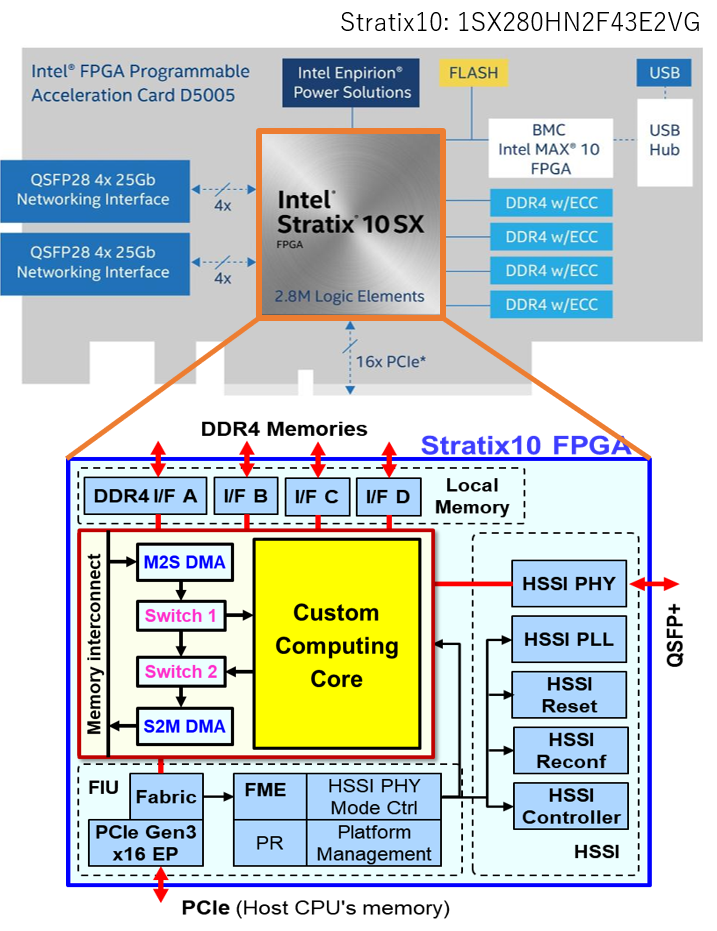

Intel 社の PAC シリーズのシェル

例として、Intel 社の PAC (Programmable Accelerator Card) シリーズのブロック図を示します。

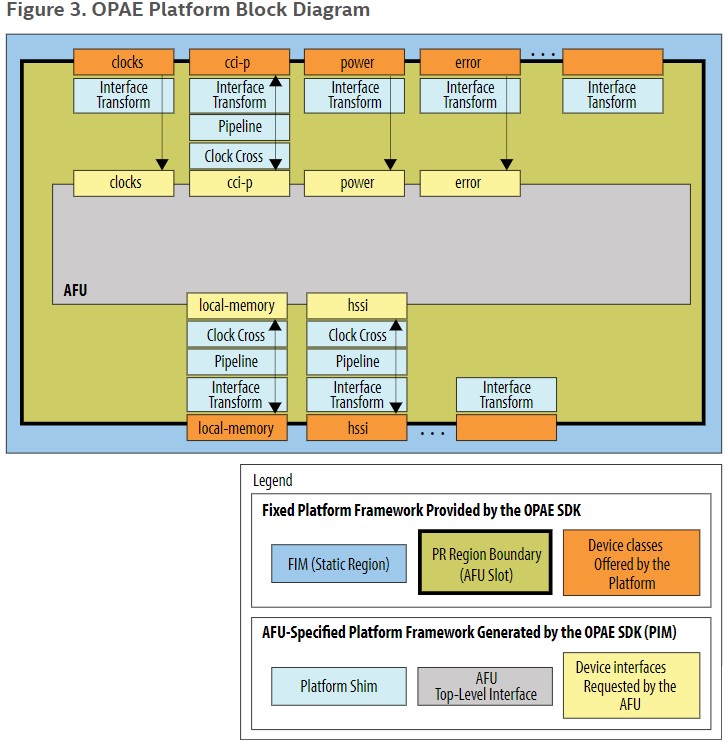

水色の FIM という部分がシェル、灰色の AFU という部分がユーザロジック部にあたります。薄い黄色の部分がユーザロジック部に提供されるインターフェイスになります。からし色の部分が動的再構成領域になり、ユーザロジック側で必要なインターフェイスのみがインスタンス化されます。

出典:Accelerator Functional Unit Developer’s Guide for Intel FPGA Programmable Acceleration Card

Intel 社のシェルの場合、インターフェイスは提供されるのですが、コントローラは実装されていません。例えば、 DDR4 メモリ用の外部メモリ・インターフェイス (EMIF) は提供されますが、DMA コントローラは実装されていないので、ユーザロジック部に実装する必要があります。

ユーザロジック部として、ユーザが利用可能なリソースは、Arria10 PAC の場合、ALMs (Logic): 381213 (92%)、 M20K (RAM Blocks): 51004 (94%)、 Block memory bits: 55562240 (100%)、 DSP Blocks: 1518 (100%) です。十分に大きな回路を実装することが可能でしょう。

なお、ユーザロジック部は、動的再構成領域の内部に存在するため、クロックの引き回しなどに少し癖があります。また、領域は 1 つです。

各社のシェルのまとめ

簡単にではありますが、各社のシェルの概要を以下にまとめます。ユーザロジック部は、ベンダやユーザによって呼称が異なりますが、シェルについては、多くのベンダが「シェル」と呼称しているようです。

Xilinx 社 SDAccel のシェル

- 解説ページ

- シェルの名称:Staric Region (shell)

- ユーザロジック部の名称:Dynamic Region

Intel 社 PAC のシェル

- 解説ページ

- シェルの名称:FIM (FPGA Interface Manager)

- ユーザロジック部の名称:AFU (Accelerator Function Unit)

Amazon 社 AWS F1 インスタンスのシェル

Microsoft 社 の Catapult のシェル

- 解説論文

- シェルの名称:Shell

- ユーザロジック部の名称:Role

理研の内製シェル AFUShell

我々が研究開発中の AFUShellは、カスタム・コンピューティング・システムを実現するための独自シェルです。Intel 社の PAC シリーズのシェルに更にシェルを追加した、いわば、Shell in Shell と言えるものです。

この様に、領域を絞った独自のシェルを定義することで、領域特化アーキテクチャが簡単に実現・提供できると考えています。

AFUShell の概要

AFUShell は、Intel 社の PAC シリーズの AFU (ユーザロジック部) の内部に実装される、追加のハードウェア・モジュール (HWモジュール) と、ホスト CPU で利用される C 言語の API から構成されます。全体としては、下図の様な構成になっており、カスタム・コンピューティング・システムを行う上で必要と考えられる機能を提供しています。

出典:FPGA Cluster as Off-loading Engine for Supercomputers, Kentaro Sano, ReHPC conjunction with FPL2019

原稿執筆時点での追加 HW モジュールを以下に列挙します。DMA コントローラは、第4回でお話したもので、SL III は 第2回でお話したように FPGA 間の直接通信に利用されるものです。また、クロスバースイッチは、各モジュールを繋ぐスイッチになります。

- DMA コントローラ

- Serial Lite III (SL III) コントローラ

- フロー制御機能搭載のルーター

- Ethernet コントローラ (研究開発中)

- クロスバースイッチ

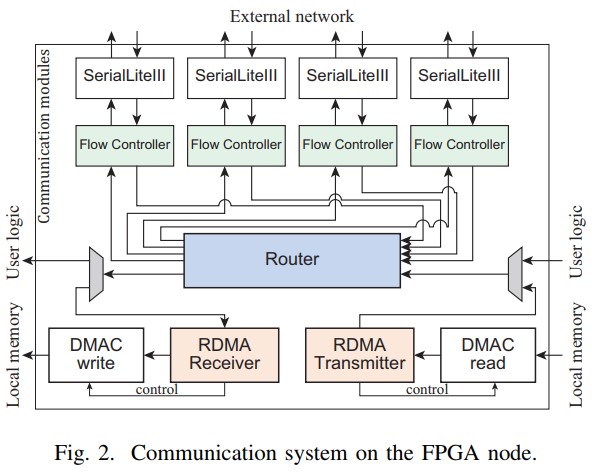

フロー制御機能搭載のルーター

我々が開発した独自のルーターは、SL III と組み合わせることで間接通信を可能にしています。詳細は論文をご覧頂ければと思いますが、ルーターの概要とブロック図は以下の様になります。

出典:Hybrid Network Utilization for Efficient Communication in a Tightly Coupled FPGA Cluster, Ueno et.al, FPT2020

本ルータの特徴は、クレジットベースのフロー制御機能を搭載している点です。この機能は、データの喪失を抑えるもので、実運用には欠かせません。また、ルータから DDR メモリだけでなく、ユーザロジックへ直接データを転送することが可能で、計算全体のレイテンシを低く抑えることができます。

クレジット・ベースのフロー制御とは、受信側にバッファの大きさを元にクレジット値を設定し、受信側と送信側でクレジット値を適宜やり取りするものです。送信側でクレジットがゼロにならない様に自律的に転送データサイズを調整することで、受信側がバッファ溢れでデータを喪失してしまうことを防ぎます。また、バッファが溢れそうな場合は、受信側からバックプレッシャーをかけて、データの送信を一時的に止めることも可能です。

ルーティングには、テーブルベースの次元順ルーティングを採用しており、Turn restriction を行うことでデッドロックを回避しています。

ユーザロジック部の開発方法

ユーザロジック部の開発方法は一般的な FPGA への回路実装の手法が利用できます。

RTL や高位合成言語だけでなく、我々が研究開発中のデータフロー向けコンパイラ SPGen での実装も可能です。

例えば、我々の論文では SPGen で数値流体力学の分野で注目されている Lattice Boltzmann Method をユーザロジック部に実装しました。結果として、1.06 TFLOPS の計算性能と12.6 GFLOPS/W の電力性能を達成しています。

また、開発のビルドフローはスクリプト化されコマンド一発で合成が可能です。(一部 Quartus の GUI ツールでの結線が必要ですが)

今後の展開

我々は、カスタム・コンピューティング・システムの実現に向け、FPGA クラスタとそのシステムを研究開発中です。現時点では、これまでにご紹介したシェルやノード間通信機能が完成し実用段階に入っております。

第1回でお話 したコンセプトの実現には、まだまだ解決すべき問題が山積しています。

今後は、アプリケーションの実装やシステムソフトウェアの開発を始めとした研究を進めていく予定です。

共同研究などのお問い合わせをお待ちしております 🙂

https://www.r-ccs.riken.jp/jp/overview/lab/prt.html

理化学研究所 計算科学研究センター (R-CCS) プロセッサ研究チーム

特別研究員 宮島敬明

チームリーダー 佐野健太郎