20Q2.02A

20Q2.02AIP の世界からこんにちは (5)

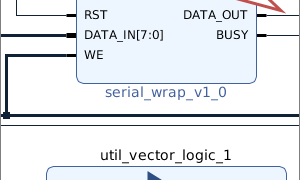

IP インテグレータを用いた回路やシステムの設計について学ぶコースも、いよいよ今回が最終回です。前回は、文字送信回路の IP コアを MicroBlaze と組み合わせるための IP コアを作成し、これらを含むブロック図からシステムを合成しました。今回は、このシステムの上で動作するソフトウェアを記述し、動作確認を行います。 なお,今回の内容は基本的に Vivado/Vitis 2019.2 を対象に記述しています。2019.1 以前の Vivado では、こうした FPGA 上の組込みプ...