20Q3.01B

20Q3.01BAXI でプロセッサとつながる IP コアを作る (3)

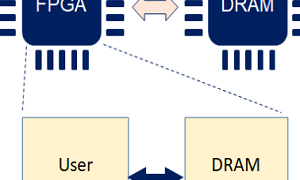

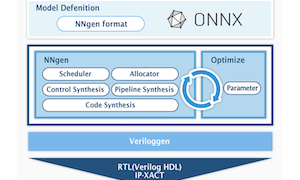

この記事は、AXI を使ってプロセッサと連携する回路の設計例について説明するコースの第3回です。前回は、AXI-Lite で制御や少量のデータのやりとりを行うインタフェース回路について説明しました。今回は、AXI-Stream でテストパターンの動画像を生成する IP コアを作成し、これらを既存の IP コアと組み合わせて、HDMI 接続のディスプレイにテストパターンを表示させるシステムを構築します。 今回示すシステムは HDMI を扱うため、残念ながらその動作を ACRi ルームの検証...