20Q2.01A

20Q2.01AFPGA で始めるエッジディープラーニング (6)

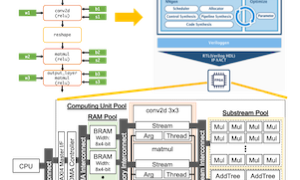

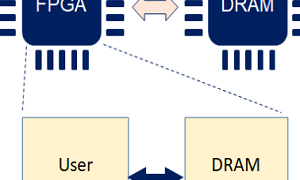

みなさんこんにちは。この記事は ACRi ブログの Deep Learning コースの第6回目です。 この記事では、前回の記事で作った推論関数を Alveo U200 ボード上で動作させていきます。このデザインは ACRi ルーム の Alveo U200 搭載サーバー上で動作を確認済みです。 また、このブログに記載しているコードは で公開しています。コードの権利、ライセンスに関してはライセンスファイルを参照するようにして下さい。興味がある方はコードをダウンロード後、READM...