20Q4.03A

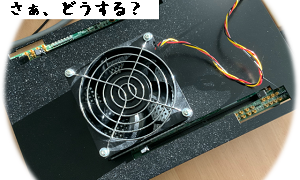

20Q4.03AFPGA 使え、って社長に言われた。さぁ、どうする? (5)

前回までのお話 自社の主力製品を調査し、FPGA 事業部の方向をすり合わせることにした Y 君。ただ、自社製品で取り扱っているからという理由だけで通信を対象とした製品を扱うのは不十分と考え、幾らかの市場調査を加え、特にリアルタイム性を有する Social Media という分野に焦点をあててプレゼンを行った。打ち合わせにおいて大きな反対はなかったものの、宿題として具体的な製品イメージおよび製品仕様の提出が課された。慌てた Y 君は、作成したプレゼン資料を持参し、改めて先生のもとへ向かっ...