20Q2.01A

20Q2.01AFPGA で始めるエッジディープラーニング (2)

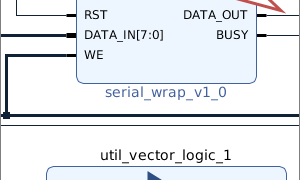

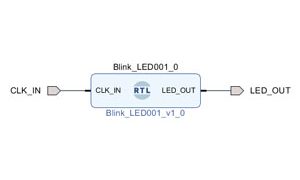

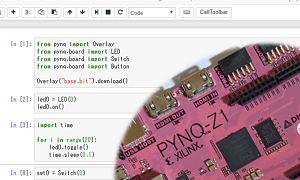

みなさんこんにちは。この記事は、ACRi ブログの Deep Learning コースの第2回目です。 前回の記事では、Deep Learning とは何か、FPGA で Deep Learning するメリットについて話しました。このコースのこれ以降の記事では、FPGA をターゲットとした Deep Learning 用デザインの開発を始めていきます。特にこの記事では、まずは Python 上で学習コードを動作させ、FPGA 上で動かすためのネットワークモデルを作成します。 これ...