21Q1.02B

21Q1.02BFPGA for HPC:宇宙物理アプリケーションをマルチ FPGA で高速化 (2)

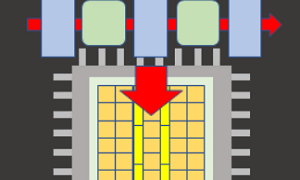

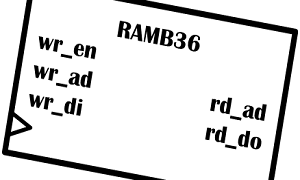

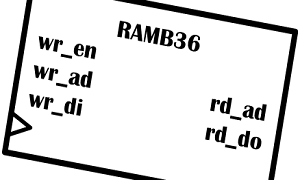

前回の記事では、宇宙物理アプリケーションになぜ FPGA を利用しようと考えるに至ったかについて紹介しました。2 回目となる今回は、宇宙物理アプリケーションの支配的な処理である ART 法 (前回の記事参照) のハードウェアアクセラレータをどのように FPGA に実装していくかをご紹介します。 FPGA-based ART accelerator 実装の概要 1 FPGA に実装される ART 法のハードウェアアクセラレータ。各 Processing Element (PE)...