20Q3.03B

20Q3.03BFPGA の高速シリアルトランシーバ (2)

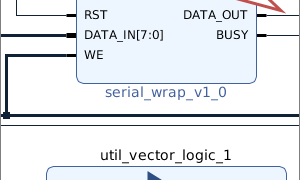

連載2回目となりました。前回は FPGA 設計ツールはさわらずに、高速シリアルトランシーバに関する基本的なことがらを紹介しましたが、「習うより慣れろ」とか「百聞は一見にしかず」と申しますので、今回は難しい設計は一切やらずに、Xilinx の Aurora コアをぽちぽちっと生成して、シミュレーションで動かしてみることにしましょう。シミュレーションなので、トランシーバのポートを持った FPGA ボードがなくてもできますし、ボードをお持ちの方はちょっと手を加えれば実機で動かすこともそれほど難しくあ...